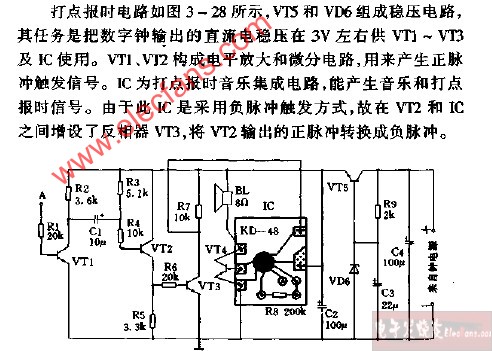

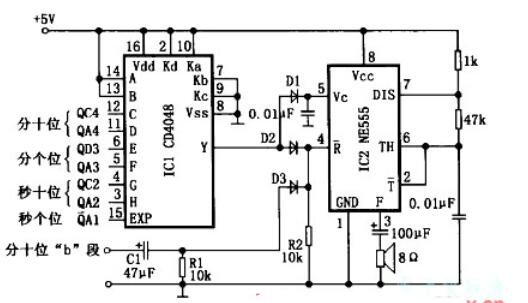

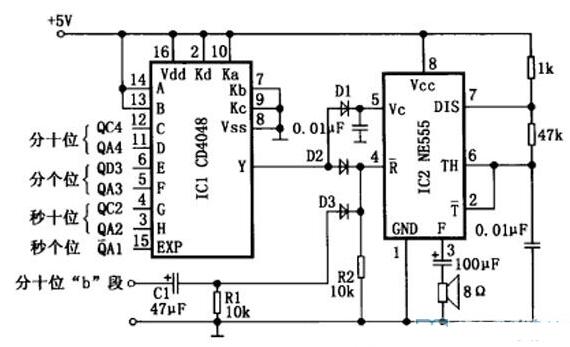

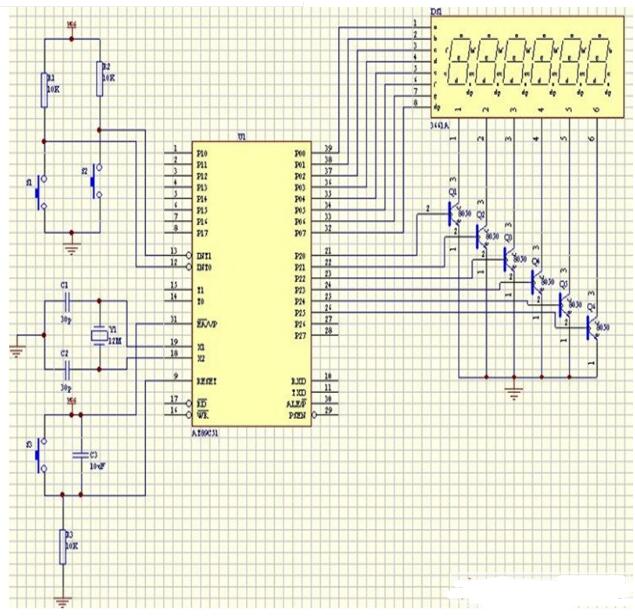

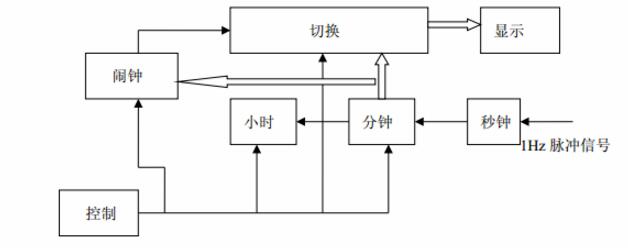

数字钟打点报时电路图

电子发烧友App

电子发烧友App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网>电子技术应用>电子技术>电路图>消费类电子电路图>数字钟打点报时电路图

相关推荐

13

13 45

45 15

15 2365

2365

32

32 4166

4166

29

29 809

809 654

654 155285

155285

96265

96265

9768

9768

131

131 48

48 58

58 30

30 7634

7634

8

8 105

105 32123

32123 826

826 470

470 1973

1973

评论