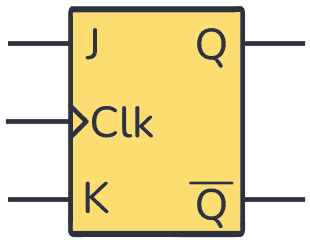

JK触发器是一种可以设置、重置和切换的人字拖。它可用于制造计数器、事件检测器、分频器等等。

2023-06-29 11:48:23 7203

7203

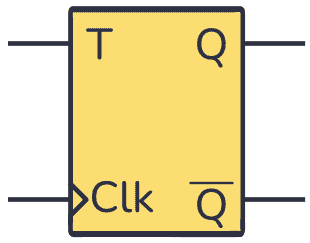

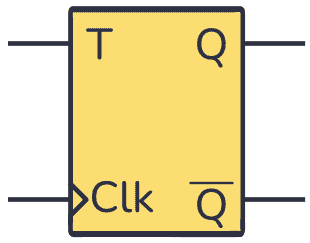

T触发器是一种可以切换其输出的人字拖。切换意味着将其输出切换到相反的输出;1 变为 0,0 变为1。这种类型的触发器通常用于计数器和分频器。

2023-06-29 11:37:55 3325

3325

电子发烧友网站提供《在Verilog HDL中使用分频器的8位计数器的设计.zip》资料免费下载

2023-06-15 10:14:44 0

0 基于51单片机的分频器1(计数器实现)例程源代码

2023-05-18 09:54:09 0

0 在数字电子产品中,计数器是由一系列触发器组成的时序逻辑电路。顾名思义,计数器用于计算输入在负或正边沿转换中出现的次数。根据触发触发器的方式,计数器可以分为两类:同步计数器和异步计数器。了解这两种计数器的工作原理以及它们之间的区别。

2023-03-25 17:31:07 11617

11617

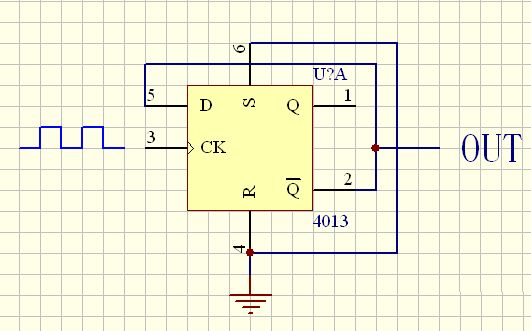

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种触发器也称为延迟触发器,经常用于许多时序电路,如寄存器、计数器等。下面一起来了解一下D触发器不同应用下的电路图。

2023-01-06 14:19:46 1874

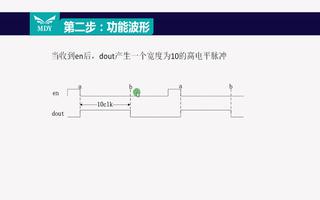

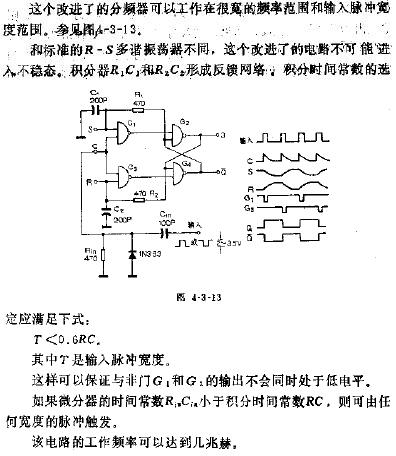

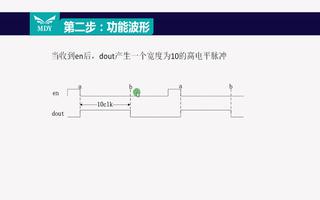

1874 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2022-11-21 09:41:24 536

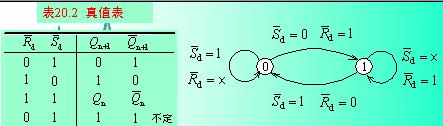

536 rs触发器电路图与rs触发器内部电路图 rs触发器电路图 主从RS触发器电路图: 主从触发器由两级触发器构成,其中一级接收输入信号,其状态直接由输入信号决定,称为主触发器,还有一级的输入与主触发器

2022-10-19 19:16:03 16964

16964

电子发烧友网站提供《内插倒数频率计数器FC510预分频器(LMX2324)开源.zip》资料免费下载

2022-08-08 11:32:02 0

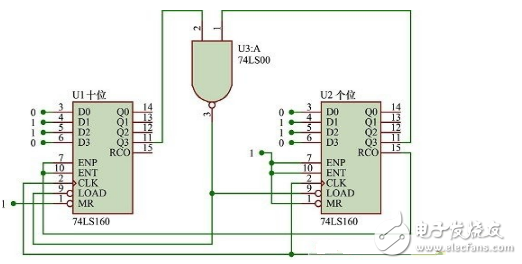

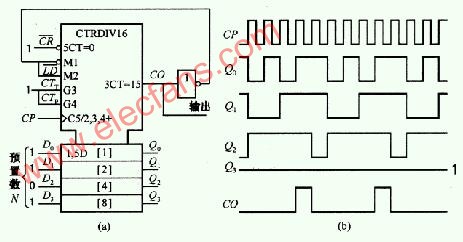

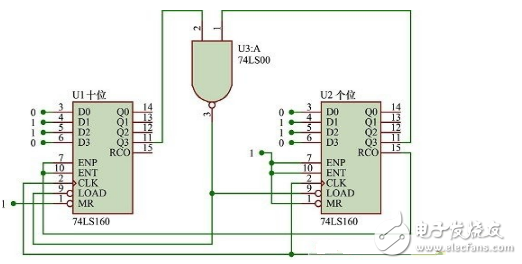

0 1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制

2022-07-10 14:37:37 15

15 电子发烧友网站提供《带预分频器的Arduino射频频率计数器.zip》资料免费下载

2022-07-06 09:26:04 0

0 集成触发器、集成计数器及译码显示电路实验目的1. 验证基本RS、D、JK触发器的逻辑功能。2. 了解十进制加法计数器和减法计数器的工作过程。3. 了解计数、译码、显示电路的工作状态。实验原理在数字电路

2008-12-11 23:38:01

单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。 如何用二进制加法计数器芯片接成计数长度为6的计数器? 其实很简单:用两片级联,第一片

2021-07-13 14:09:37 11289

11289 计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

2019-12-23 07:07:00 1242

1242

计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等,计数器在数字系统中应用广泛。

2019-12-19 07:09:00 2315

2315

计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

2019-12-10 07:08:00 1186

1186

计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

2019-09-29 07:05:00 751

751

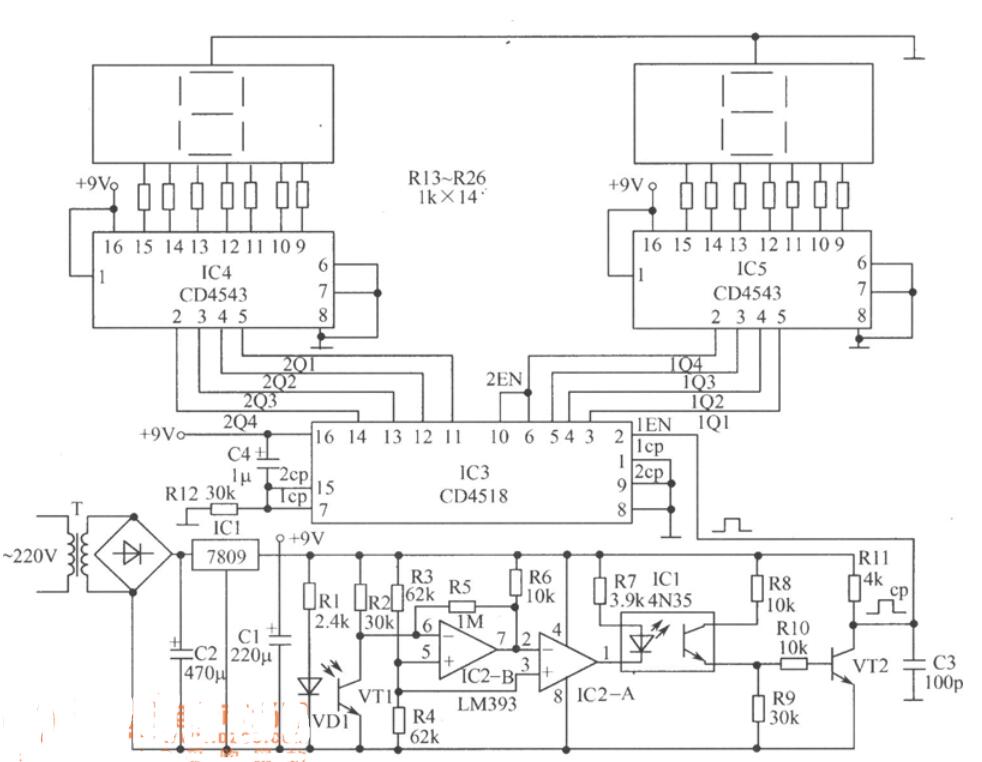

本文主要介绍了电子计数器电路图及电子计数器的接线方法。

2019-09-26 10:06:37 41514

41514

我们之前看到,切换T型触发器可以作为个体使用除以两个计数器。如果我们将串联链中的几个触发器触发器连接在一起,我们就可以生成一个数字计数器,用于存储或显示特定计数序列发生的次数。

2019-06-23 08:47:00 14774

14774

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2019-02-01 01:49:00 933

933

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2019-01-24 14:35:40 62199

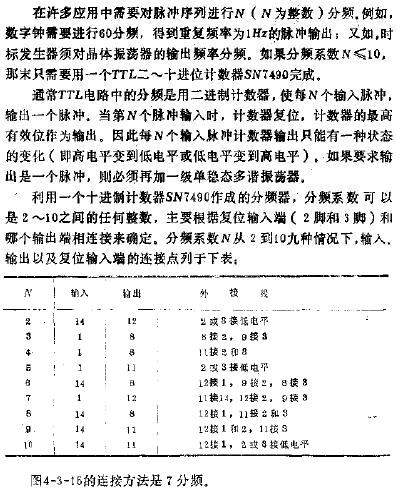

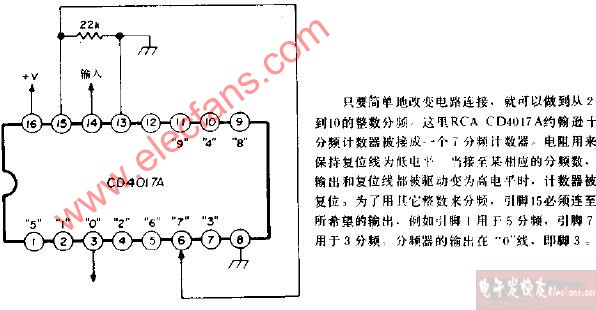

62199 关键词:TTL , 分频器 , 计数器 , 十进制 如图所示为由TTL十进制计数器构成的分频电路。在许多情况下。需要对脉冲序列进行N(N为整数)分频。例如,数字钟需要进行60分频,得到重复频率为

2018-10-03 18:46:02 2650

2650 关键词:S8424 , 分频器 , 分频系数 如图所示为分频系数可变的分频电路。该分频器由R-S触发器、门电路和二-八进制拨盘开关组成,可以进行1~8分频。图中的8058是二-八进制拨盘开关

2018-10-03 18:37:02 338

338 ,计数器的“借位”输出除驱动触发器SN7476外,还作为SN74193的寄存输入脉冲。五位二进制数加在D0、D1、D2、D3、D4输入端,由它确定分频系数(2~32)。其中,D0是最低位。当D0=1时,多路调制器输出脉冲的相位则根据触发器的状态确定。触发器Q输出为“0”时,多路调制器的输出与钟

2018-10-03 18:34:01 480

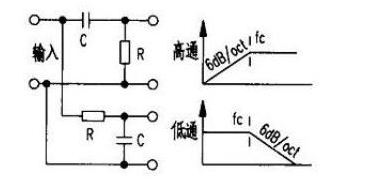

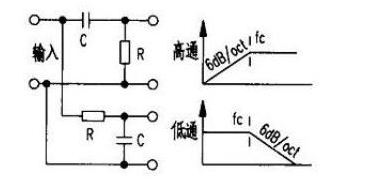

480 采用有源分频器可以降低对功放带宽的要求;省去了大功率的LC元件;分频点也易于调整,且可以获得比功率分频更佳的效果。这里介绍两种有源二分频器电路。如图9-4所示为有源二分频器组成的功放电路

2018-08-10 16:19:37 18326

18326

本文主要介绍了74ls161分频电路图大全(脉冲分频电路\同步加法计数器)。计数器又称为分频器。N进制计数器的进位输出脉冲就是计数器输入脉冲的N分频。N进制计数器可直接作为N分频器。用同步加法计数器

2018-05-08 14:41:38 95799

95799

和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。计数器在数字系统

2018-03-26 11:22:00 84513

84513

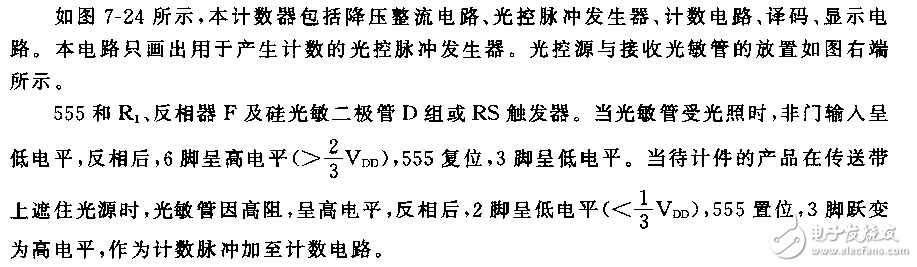

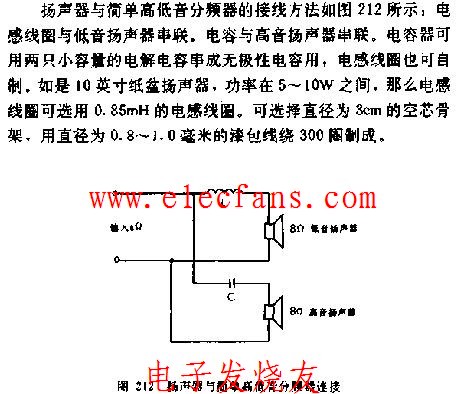

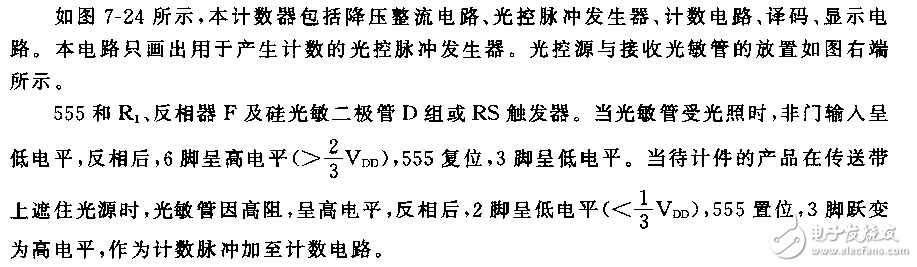

本文主要介绍了电子分频器电路图大全(六款电子分频器电路设计原理图详解)。从工作原理看,分频器就是一个由电容器和电感线圈构成的滤波网。高音通道只让高频信号经过而阻止低频信号;低音通道正好相反,只让低音

2018-03-02 09:41:17 117553

117553

本文开始对CD4017功能与CD4017逻辑结构图进行了介绍,其次分别介绍了用CD4017和选择开关组成多进制计数器、CD4017组成的1/n计数器电路与用CD4017组成1~17进制计数器电路图。

2018-01-31 13:58:06 22819

22819

,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。本文为大家带来七种任意进制计数器设计方案及其电路设计的原理详解。

2018-01-17 17:36:07 67188

67188

分频器分为主动式、被动式、脉冲分频器三种。主动式电子分音器的原理就是要把适当频率讯号传给适当的单体,被动式分音器“功能、用途”是介于扩大器与喇叭之间,由于单一喇叭无法达到“全频段响应”,脉冲分频器利用汉稳态电路的计数功能实现分频的电路,又称为数字分频器。

2018-01-10 15:36:20 10336

10336 计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2017-10-23 17:48:48 15

15 计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2017-09-25 10:13:37 8

8 HL开发板配套C实验例程100例之分频器1(计数器实现),很好的单片机C语言资料。

2017-09-01 09:28:27 4

4 HL配套C实验例程分频器1(计数器实现),配合开发板学习效果更好。

2016-04-11 17:14:06 7

7 由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B

2011-11-25 15:16:42 29662

29662

分析了应用于倍频电路的预置可逆分频器的工作原理,推导了触发器的驱动函数。并建立了基于simulink 和FPGA 的分频器模型,实验结果表明分频器可以实现预置模和可逆分频功能,满足倍

2011-08-17 16:50:45 1840

1840

本内容介绍了采用新触发器的高速CMOS 前置分频器 ,欢迎大家下载

2011-07-26 18:05:25 37

37 D触发器的常规使用一般是用作二分频器、计数器或移位寄存器。然而,只要对D触发器的外围电路加以改进,根据其基本逻辑功能。就可充分发挥其独特的作用。数

2010-12-29 11:44:46 2899

2899

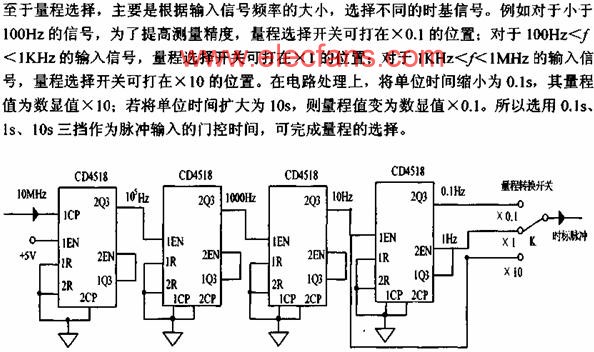

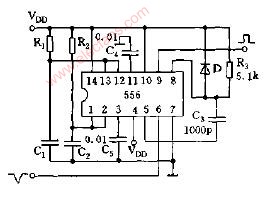

分频器及量程选择电路 分频器是由多级计数器完成,目的是得到不同的标准时基信号。采用4片双十进制中规模计数器CD4518级联可获得10

2010-11-06 11:57:17 1770

1770

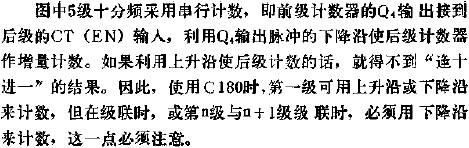

图中所示是用C180 2-10进制同步加法计数器组成的时基分频器(多级串行计数)线路.图中晶体振荡器采用振荡频率为

2010-10-19 15:03:29 1511

1511

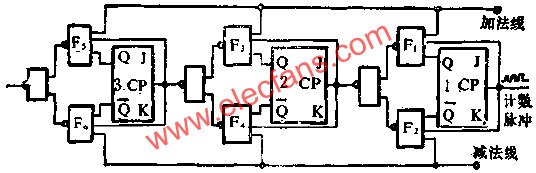

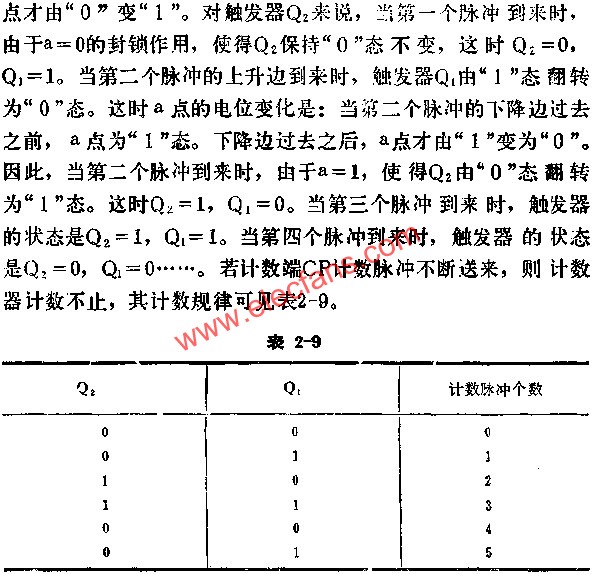

图中所示是J-K触发器组成可逆计数器电路。要求计数器能够在一定条件下,从加法计数改换成减法计数,也可以

2010-09-24 01:03:53 2756

2756

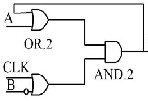

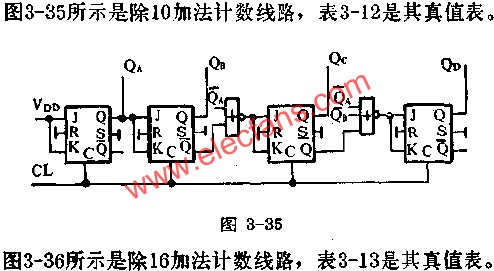

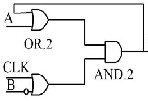

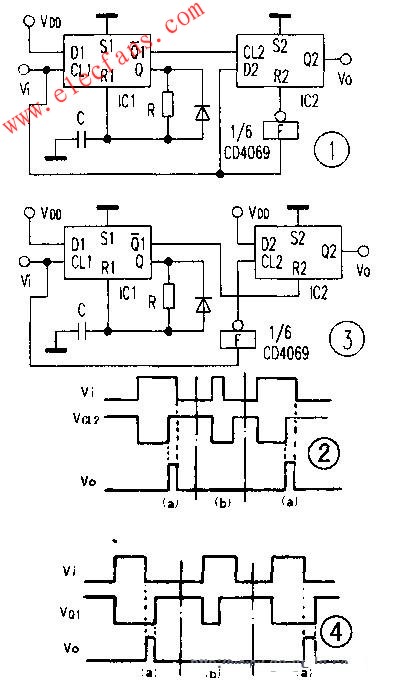

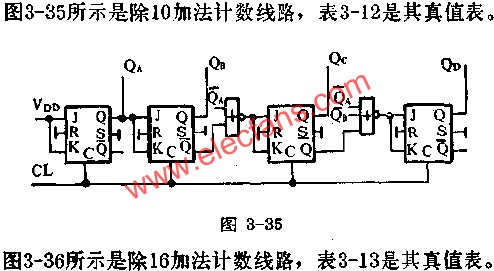

图A所示是用CMOS电路J-K触发器组成的除2加法计数线路,表A是其真值表。

图B所示是除3加法计数线路,表B是其真值表。

2010-09-24 00:51:15 1916

1916

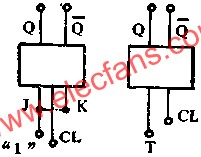

图中所示是J-K触发器组成T触发器的电路和逻辑符号。将J端和K端连接,作为T端,它的功能是当T=“1”,即J,K

2010-09-24 00:26:06 6756

6756

图中所示是用J-K触发器组成的D触发器电路。

从J-K触发器的逻辑图已知在D触发器端增

2010-09-24 00:21:27 5729

5729

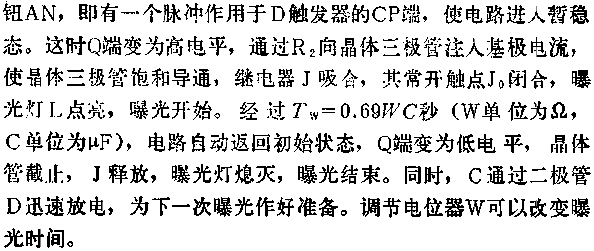

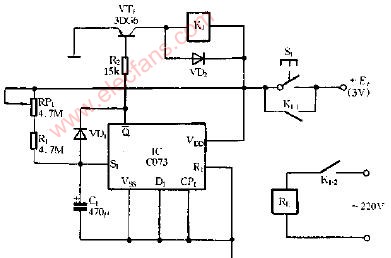

图中是用D触发器组成的曝光定时器电路。曝光时间可在1秒至30秒内任意选择。

2010-09-23 23:53:40 757

757

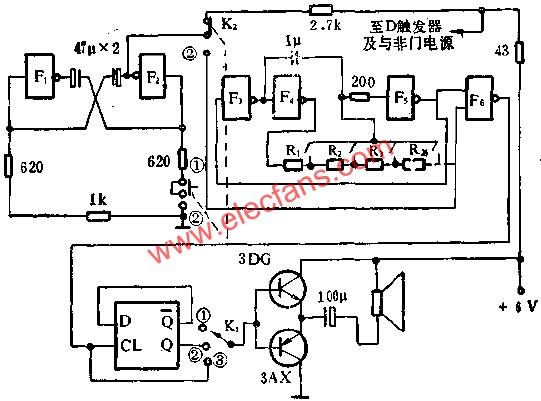

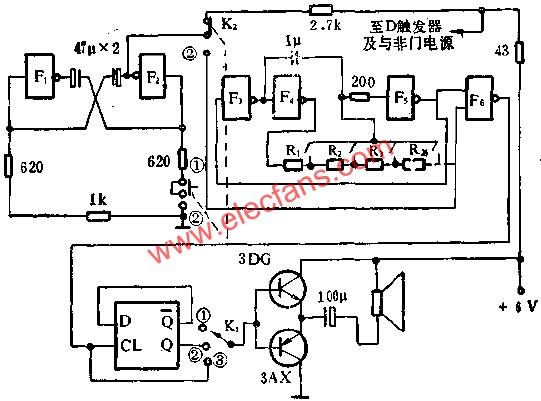

乐器或其它某些乐器的碎音效果;分频器由D触发器组成,当K1置于2位时,D触发器将F6输出的类似双簧管音阶信号从CL端输入,经二分频后从Q端输出,这声音很象黑管;音频功放采用互补型,不赘述了。调整颤音振荡器620欧和1K电阻的数值可改变颤音的弹拨乐音型的调制频率。

2010-09-21 01:40:16 1347

1347

图中所示是用CMOS电路D触发器组成的单稳态多谐振荡器.因为D触发器除了具有传送D端数据的功能外,还具

2010-09-21 00:08:57 3792

3792

图中所示是用CMOS电路D触发器组成的十进制环形计数器.图中先将D触发器拼成移位寄存器,然后把最后一级D触发器

2010-09-20 23:46:58 17358

17358

如果连接N个D触发器,则组成N位移位寄

2010-09-20 04:48:02 9137

9137 图中所示是用CMOS电路D触发器组成T型触发器和J-K触发器线路。图示线路将D触发器的Q端与D端相连,就可组成T

2010-09-20 03:31:35 15895

15895 图中所示是用与非门组成的二进制计数器,实际上它是用与非门组成的维持-阻塞触发器而组成的计数器.图

2010-09-19 00:54:13 2214

2214

一、基本要求1、理解R-S触发器、J-K触发器和D触发器的逻辑功能;2、掌握触发器构成的时序电路的分析,并了解其设计方法;3、理解计数器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 计数器的定义和分类

计数器定义在数字电路中,计数器属于时序电路,它主要由具有记忆功能的触发器构成。计数器不仅仅

2010-03-08 17:37:35 11724

11724 D触发器,D触发器是什么意思

边沿D 触发器: 电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高

2010-03-08 13:53:13 4130

4130 可编程分频器电路

可编程分频器:计数器可以对计数脉冲分频,改变计数器的模便可以改变分频比。根据这个原理,可以用集成计数

2010-01-12 13:58:07 3041

3041

d触发器构成2分频电路

2009-06-22 07:36:33 7322

7322

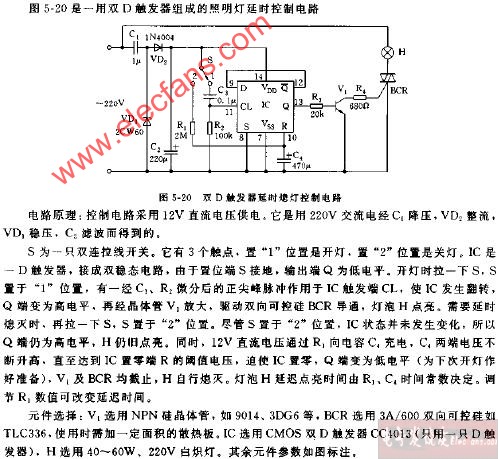

双D触发器延时熄灯控制电路图

2009-06-13 17:11:57 1944

1944

D触发器实现二分频电路(D触发器构成的2分频电路)&

2009-06-12 13:58:56 73460

73460

D触发器的制作及电路图

2009-05-19 09:35:49 33

33

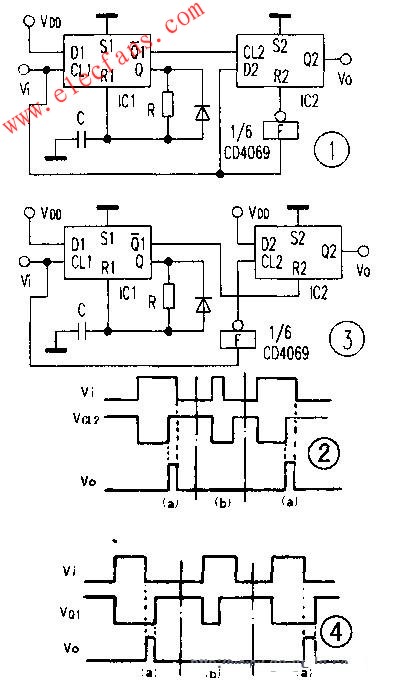

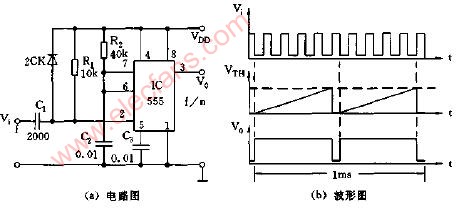

单稳电路用作分频器电路图

2009-05-18 15:49:55 735

735

时基触发器电路图

2009-05-18 15:05:38 375

375

D触发器构成的定时电路图

2009-05-08 15:15:26 3107

3107

T触发器电路图

2009-05-08 14:27:49 9043

9043

D触发器电路图

2009-05-08 14:26:44 3484

3484

触发器的输入电路图

二极

2009-05-08 13:58:03 583

583

分频器和阶梯波发生器电路图

2009-04-15 09:30:23 796

796

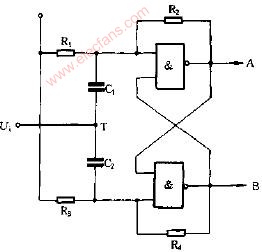

由R-S触发器构成的分频器

2009-04-11 10:28:43 870

870

TTL十进位计数器构成的分频器

2009-04-11 10:14:57 1067

1067

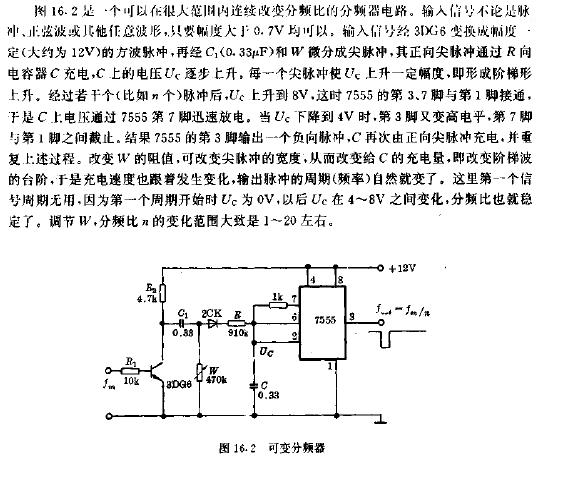

可变分频器电路图

2009-04-09 12:00:35 2320

2320

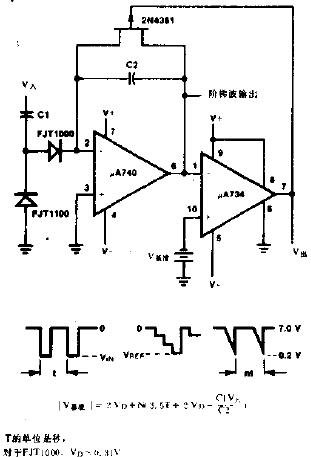

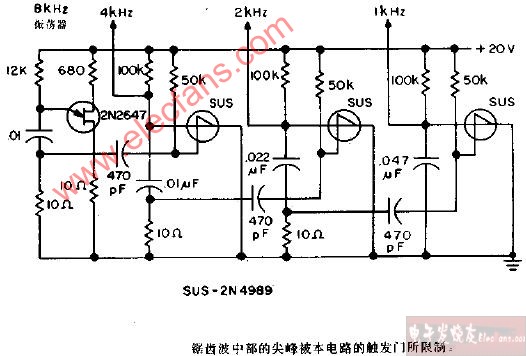

抑制尖峰干扰的分频器电路图

2009-03-29 09:57:26 1127

1127

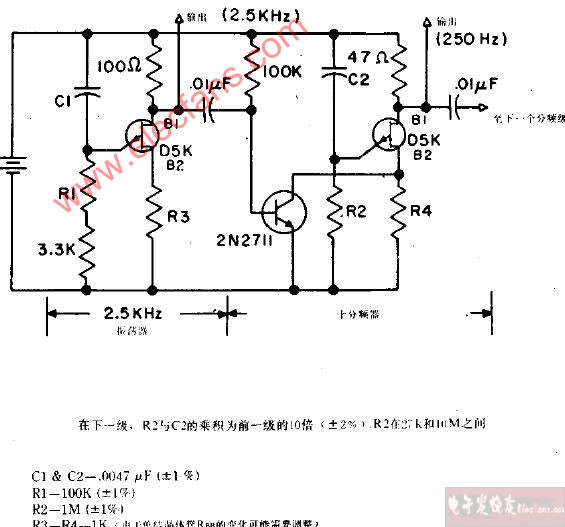

十分频器电路图

2009-03-29 09:57:00 6221

6221

CMOS可编程N分频计数器电路图

2009-03-29 09:55:36 738

738

D触发器的功能测试74LS74型双D触发器芯片引脚图,D触发器功能测试的引脚连线图,D触发器功能测试的引脚连线图,用D触发器构成二进制计数器,用D触发器构成四位移位寄存器

J-K

2009-02-14 15:27:51 290

290 同步式D触发器逻辑电路图

2008-10-20 09:58:19 7678

7678

D触发器

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 1846

1846

基本RS触发器电路图

2008-10-20 09:49:49 21386

21386

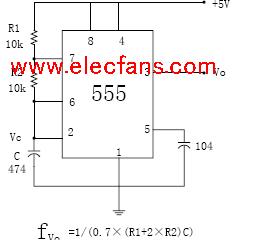

1. 555单稳态触发器

图3.10 单稳态触发器电路图

2008-09-22 11:31:17 2809

2809

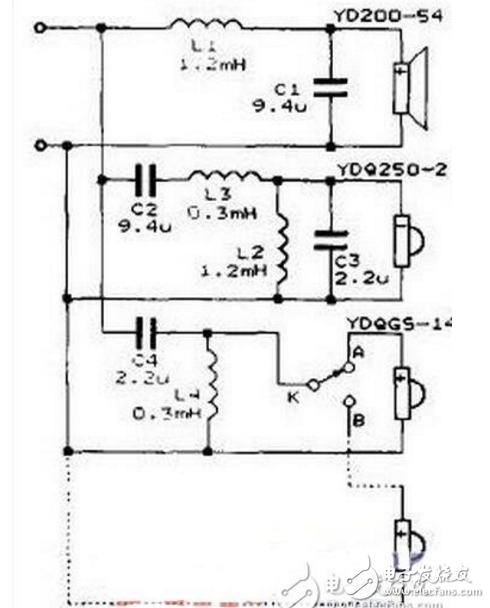

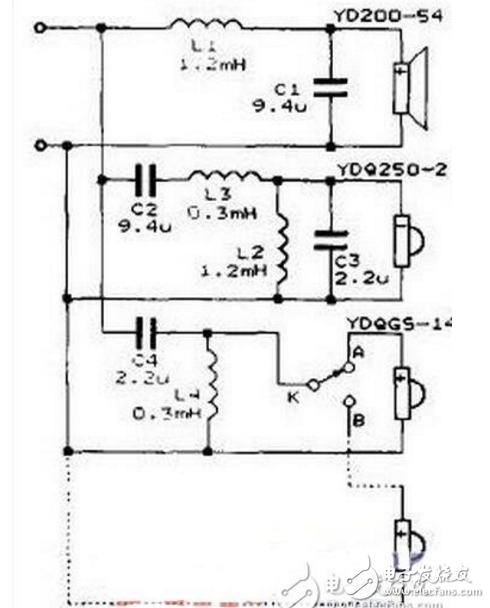

脉冲计数器电路图,本计数器包括降整流电路,光控脉冲发生器,计数电路,译码,显示电路。

2008-04-03 13:37:11 3295

3295

cd4013双d触发器

CD4013双D触发器做的脉冲4分频器应用

-----------------------------. ┌─────

2008-01-09 23:48:45 4487

4487 扬声器与简单高低音分频器连接电路图

2007-11-24 00:28:50 4461

4461

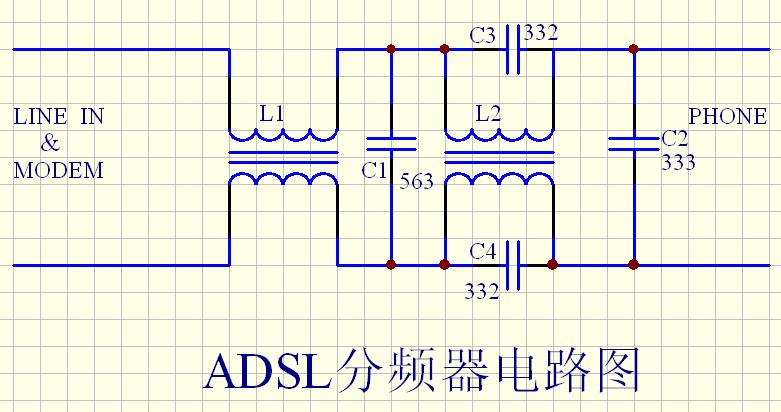

ADSL分频器电路图从电路上可以看出,该分频器的作用只是针对电话座机,而非针对MODEM。在一般

2007-09-30 19:53:24 2025

2025

电子发烧友App

电子发烧友App

硬声App

硬声App

3325

3325

11617

11617

1874

1874 536

536 16964

16964

15

15 11289

11289 1242

1242

2315

2315

1186

1186

751

751

14774

14774

933

933

62199

62199 2650

2650 338

338 480

480 18326

18326

95799

95799

84513

84513

117553

117553

22819

22819

67188

67188

10336

10336 15

15 8

8 29662

29662

1840

1840

2899

2899

1916

1916

1347

1347

57

57 290

290 4487

4487

评论