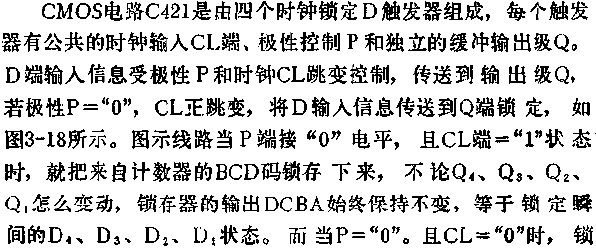

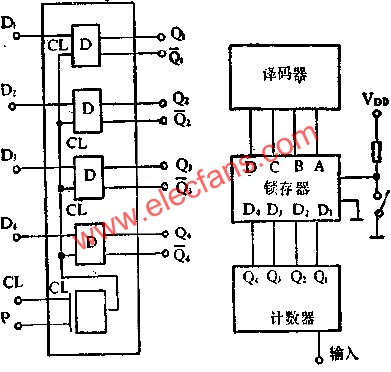

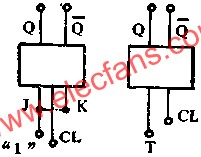

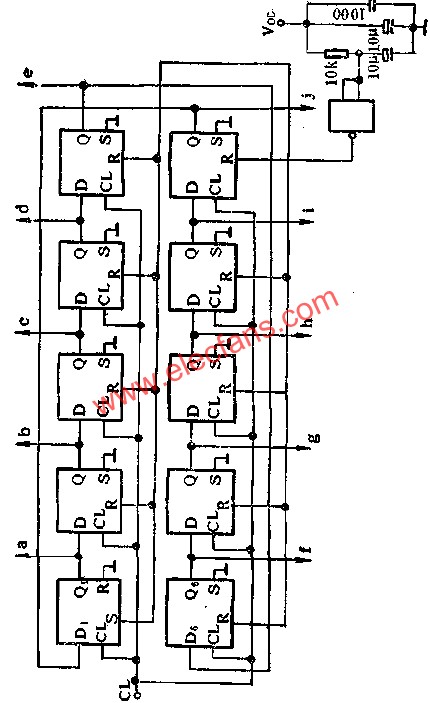

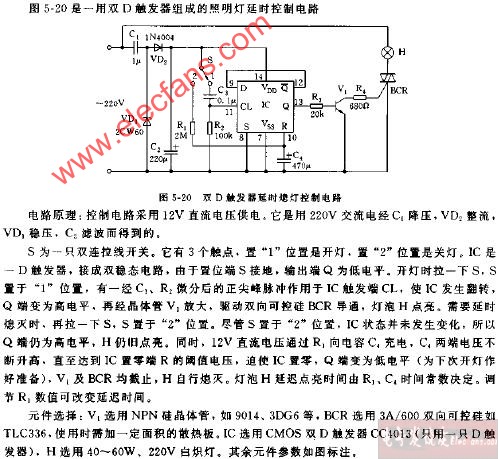

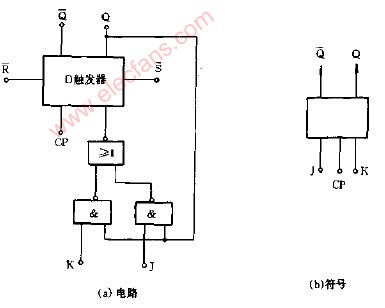

4D触发器组成锁存器电路图

- 锁存器(40691)

相关推荐

D触发器与Latch锁存器电路设计

D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 234

234

234

234

rs触发器和rs锁存器的区别是什么

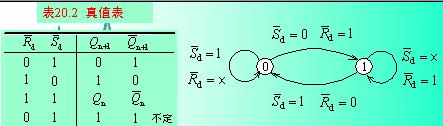

在传统的异步 RS 触发器中,当输入的 R 和 S 同时为 1 时,会引发互锁问题,输出结果是不确定的。为了避免这个问题,常常使用带有使能控制的同步触发器,如带有时钟信号的 D 触发器或 JK 触发器。这些触发器在时钟边沿上才会响应输入信号,解决了异步 RS 触发器的互锁问题。

2023-08-28 15:44:35 641

641

641

641什么是D触发器,D触发器如何工作的?

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 5258

5258

5258

5258

锁存器、触发器、寄存器和缓冲器的区别

的缓冲器(5)数据传输和处理中不同装置间温度和时间不同时,加一级缓冲器进行弥补等等。锁存器与触发器的区别锁存器和触发器是具有记忆功能的二进制存贮器件,是组成各种时序逻辑电路的基本器件之一。区别

2011-10-09 16:19:46

锁存器和触发器的定义和比较

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

2023-03-23 14:48:54 1357

1357

1357

1357

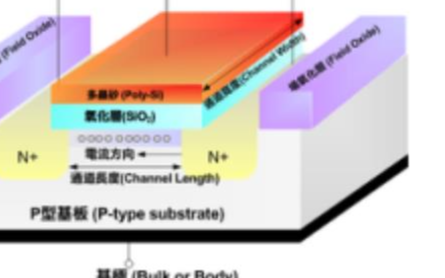

解读从CMOS到触发器 锁存器常见结构与锁存器应用

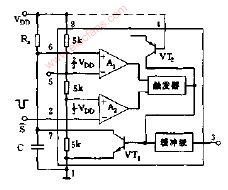

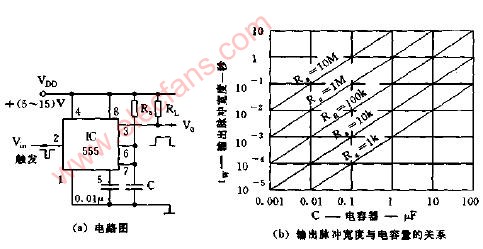

主要内容: ·双稳态器件 ·锁存器常见结构 ·锁存器的应用 ·触发器 ·触发器的建立时间和保持时间 1、双稳态器件 ** 双稳态器件**是指稳定状态有两种,一种是0,一种是1的器件;双稳态器件

2023-01-28 09:28:00 2426

2426

2426

2426

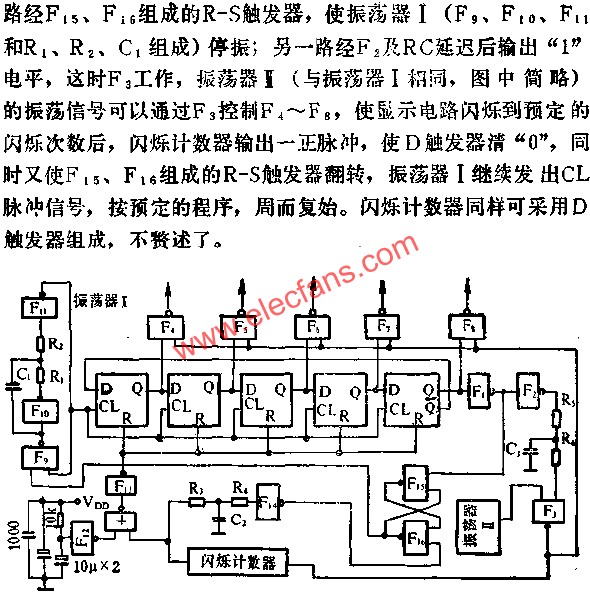

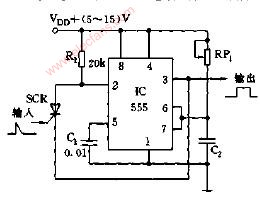

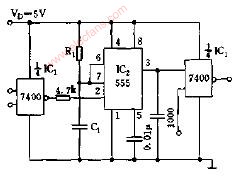

D触发器不同应用下的电路图详解

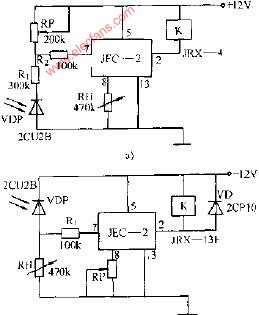

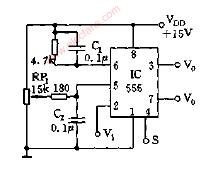

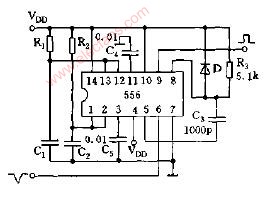

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种触发器也称为延迟触发器,经常用于许多时序电路,如寄存器、计数器等。下面一起来了解一下D触发器不同应用下的电路图。

2023-01-06 14:19:46 1874

1874

1874

1874锁存器、触发器、寄存器的关联与区别及其相应的verilog描述

1:锁存器、触发器、寄存器的关联与区别 首先应该明确锁存器和触发器是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合逻辑电路的特性。 锁存

2022-12-19 12:25:01 3721

3721

3721

3721浅谈四种入门触发器

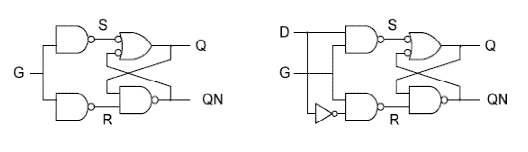

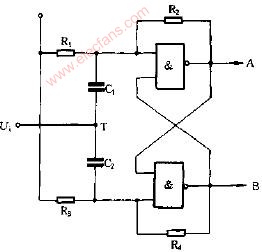

来源:罗姆半导体社区 触发器的电路图由逻辑门组合而成,其结构均由R-S锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时钟频率之间的相互影响。 在R-S锁存器的前面加一个由

2022-11-29 17:35:40 1584

1584

1584

1584rs触发器电路图与rs触发器内部电路图

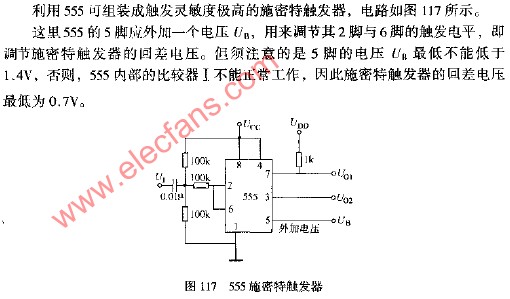

rs触发器电路图与rs触发器内部电路图 rs触发器电路图 主从RS触发器电路图: 主从触发器由两级触发器构成,其中一级接收输入信号,其状态直接由输入信号决定,称为主触发器,还有一级的输入与主触发器

2022-10-19 19:16:03 16964

16964

16964

16964

带有时钟使能和同步清零的D触发器

每个 Slice 有 8 个 FF 。四个可以配置为 D 型触发器或电平敏感锁存器,另外四个只能配置为 D 型触发器,但是需要记得是:当原来的四个 FF 配置为锁存器时,不能使用这四个 FF 。

2022-07-22 10:05:01 2518

2518

2518

25188位CPU设计(1) 门电路和锁存器、触发器

这是一个系列文章,从最简单的门电路介绍,从基础的锁存器、触发器、编码器、译码器等一系列数字逻辑电路开始,最终构造一个简易版的CPU实物

2021-11-06 09:20:58 16

16

16

16锁存器与触发器的区别

,锁存器有两个输入,一个是有效信号EN,一个是输入数据信号DATA_IN,有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 2)触发器 触发器(Flip-Flop,简写为FF)也叫双稳态门,又称双稳态触发器,是一种可以在两种

2020-11-29 11:02:11 20662

20662

20662

20662如何操作基本类型的锁存器和触发器

锁存器(有时也称为S/R锁存器)是最小的存储器块。它们可以使用两个NOR逻辑门(S和R为高电平有效)或两个NAND门(输入为低电平有效)构建,并用于构建更复杂的锁存器和触发器。

2019-07-30 11:23:28 5658

5658

5658

5658

d触发器逻辑电路及符号

CP=1时,门。。打开,门。。被封锁,从触发器保持原来状态不变,D信号进入主触发器。但是要特别注意,这时主触发器只跟随而不锁存,即。。跟随D变化,D怎么变。。也随之怎么变。

2019-07-15 08:57:32 42337

42337

42337

42337

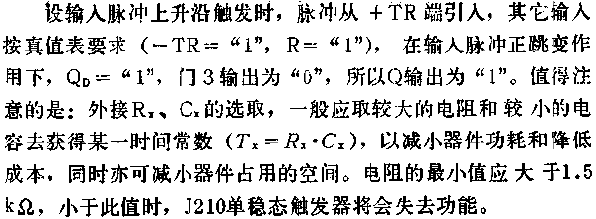

D型触发器电路真值表和计数器数的据锁存器摘要

D型触发器是一个改进的置位复位触发器,增加了一个反相器,由此可见以防止S和R输入处于相同的逻辑电平,此状态将强制两个输出都处于逻辑“1”,超越反馈锁存动作,无论哪个输入先进入逻辑电平“1”都将失去控制,而另一个仍处于逻辑“0”的输入控制锁存器的结果状态。

2019-06-26 15:36:28 14537

14537

14537

14537

锁存器Latch和触发器Flip-flop有何区别

本文首先介绍了锁存器Latch结构和锁存器latch的优缺点,其次介绍了触发器Flip-flop的结构与优缺点,最后介绍了锁存器Latch和触发器Flip-flop两者之间的区别。

2018-04-18 14:10:10 128942

128942

128942

128942

d锁存器与sr锁存器的区别

锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。

2018-01-31 14:48:13 28618

28618

28618

28618

锁存器和触发器的区别

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2017-11-02 09:24:41 92855

92855

92855

92855

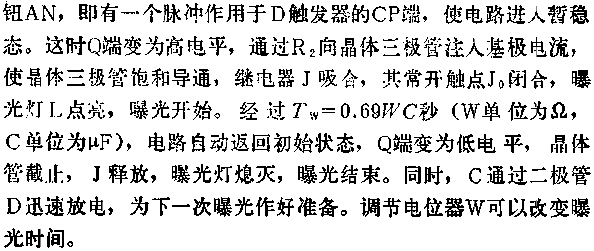

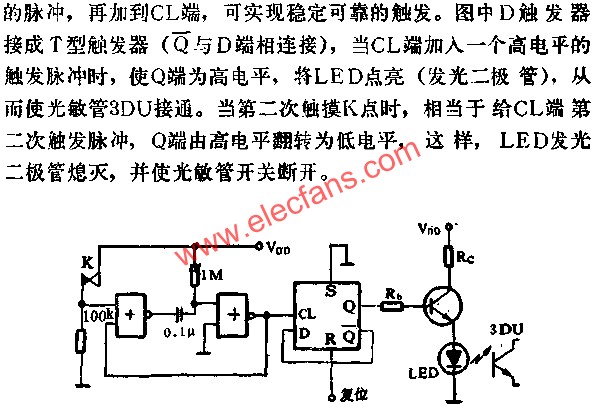

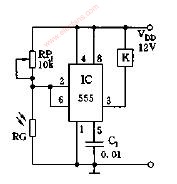

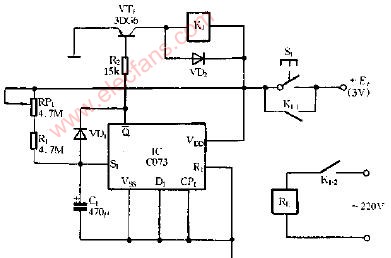

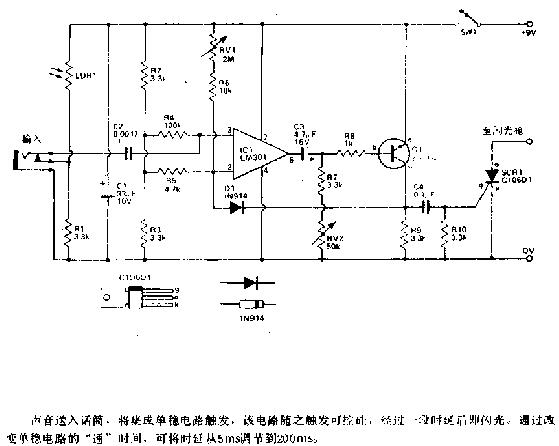

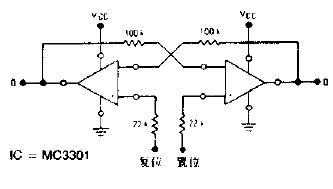

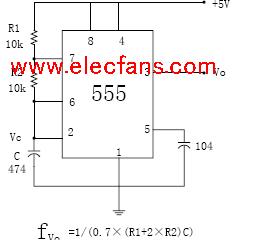

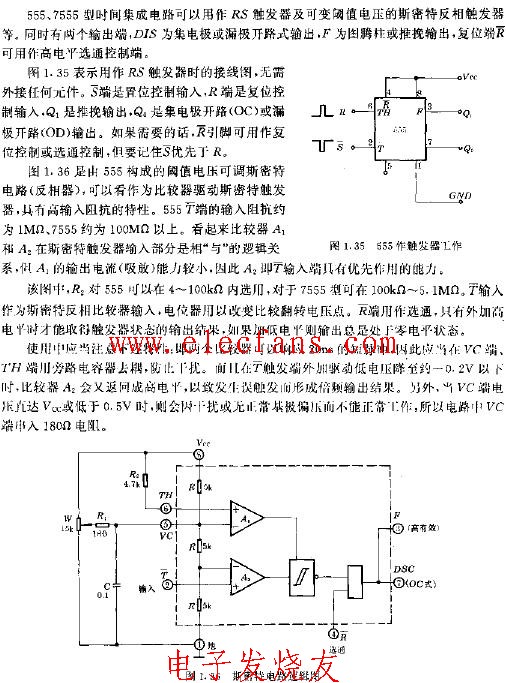

锁控防盗报警电路图

锁控防盗报警电路图,该电路由RS触发器、选通振荡器、报警电路等组成。其中RS触发器由与非门F2、F3组成,选通振荡器由集成电路TWH8751和R、C组成。

2012-03-28 14:30:02 3464

3464

3464

3464

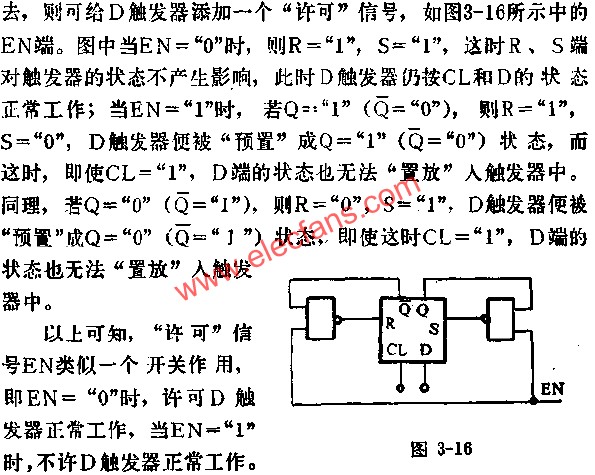

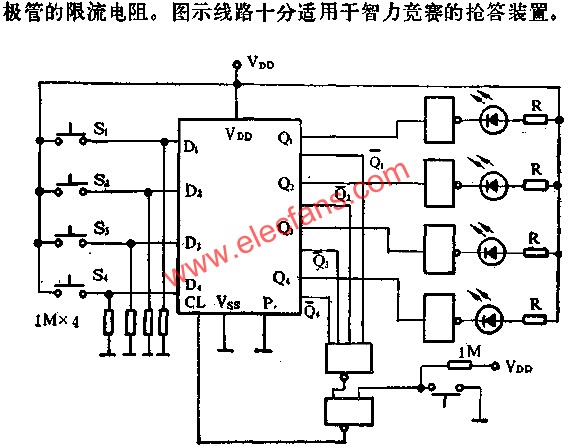

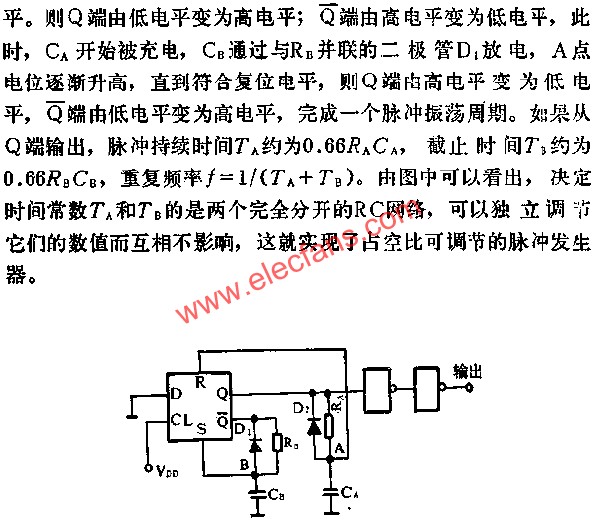

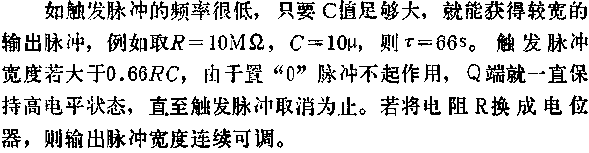

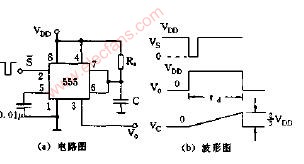

D触发器加“许可”信号电路图

从D触发器的真值表可知,当时钟脉冲CL="1"时,数据输入端D的状态会被“置放”入触发器中去,而与触发器原状无关。如果当时钟冲CL="1",D端状态不旋转放入

2010-09-21 01:27:59 577

577

577

577

锁存器和触发器原理

1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 233

233

233

233 电子发烧友App

电子发烧友App

评论