防侵入式智能监控系统

它是由红外传感器、监视器、中央控制器、记录设备及报警辅助设备等几部分组成。当有物体进入被监控区域时红外传感器给控制系统相应的信号,控制系统对信号进行分析并自动启动所对应的监视器,当控制系统得到视频信号时,系统控制记录设备进行记录,这样不但可以节省记录媒介,并且可以更进一步提高数据质量,亦可降低便携设备的能耗。

红外信号处理电路设计

如图4所示,热释电红外传感器的额定工作电流 15mA,工作电压为2.2-15 V,由4个运放组成2级放大和1个比较电路。辅以4个施密特触发器构成的延时电路,在本电路里用的7805提供1个稳定的电源。当给传感器的+Vss端施加稳定的5V电压时,只要有300-320K的黑体温度被检测到时,传感器的输出电压通过连续两级信号放大,再由比较放大器比较放大,当达到一个设定的门限阈值时就输出一个有效的信号经过施密特触发器组成的延时电路,使执行机构动作。

我们采用PDIUSBD12芯片,这是一种价格便宜、功能完善的并行接口芯片,它支持多路复用、非多路复用和 DMA并行传输。PDIUSBD12接口芯片遵从协议USB1.1,适合于不同用途的传输类型。PDIUSBD12需要外接微控制器(MCU)来进行协议处理和数据交换,它对MCU没有特殊要求,而且接口方便灵活,因此设计师可以选用自己熟悉的MCU对芯片进行控制,也可利用Philips公司的固件结构来缩短开发时间、降低风险、减小投资。

性能特点:PDIUSBD12除了具有USB设备的一般特性外,还具有如下特点:(1)是一种高性能的USB接口芯片,其内部集成有 SIE(Serial Interface Engine)、320字节的FIFO、收发器和电压调节器。(2)适用于大部分设备类规范。可与任何外部微控制器/微处理器实现高速并行接口,其速度可高达2Mbit/s。(3)可进行完全独立的DMA操作。(4)主端点配置有双缓冲,因而可提高数据的吞吐量、减小数据传输时间,轻松实现数据的实时传输。(5)当采用同步传输方式时,数据的传输速度为1Mbit/s;而采用批量传输方式的速度为1Mbyte/s。在使用上述方式进行数据传输时,可方便地使用多种中断方式。(6)带有可编程的时钟输出,与USB总线的连接可通过软件来控制(Soft Connect TM)。(7)有两种工作电压可供选择:分别为3.3±0.3V和3.6~5.5V。(8)输出和数据传输状态可通过USB连接指示灯来监控。

红外传感信号处理模块设计

为了节约电能, 本终端采用红外传感器来检测监控区域有无人员进入, 只在有人员进入监控区域时, 终端才进入图像采集、处理、传输状态。本设计采用BISS0001芯片为热释电红外传感信号处理核心元件, 其应用电路如图2 所示。

图2 红外信号处理电路

图2 中,7805 为三端稳压集成电路, 为信号处理电路提供电源。BISS0001 芯片的第9 引脚为触发控制信号Vc的输入脚, 工作中应当保证输入电压, 可以通过调节电阻R3来达到目的。当有行人进入监控区域时, 热释电红外传感器PIR 将检测到的人体发出的红外线转化为电信号, 并将其送到BISS0001内部, 信号经BISS0001 处理后由2 脚输出, 输出Vo为低电平到高电平的跳变。如果BISS0001 工作在有效状态不可重复触发的情况下(即图2 中S1 接低电平), 高电平的持续时间为Ts (Ts=49 152 R1C1), 在Ts时间段结束时,输出Vo即刻由高电平进入低电平并被封锁Ti (Ti =24R2C2 ) 时长; 对于有效状态可重复触发的情况来讲( 即图2 中S1 接高电平), 如果在前一Ts时间段内, 输入的变化使得输出有效状态再次触发, 则Vo高电平信号将从此刻算起再持续一个Tx时长, 之后才转换为低电平并进入封锁时间Ti。在封锁时间内, 即使由于负载的切换而引入的干扰也不会改变输出Vo的状态。本设计中让S1 接高电平, 红外传感信号处理电路的输出信号Vo作为DM642 的外部中断信号, 同时也作为TVP5150 芯片的节电模式输入控制信号, 如图2 所示。

图像采集模块设计

对于图像采集模块, 本设计采用TI 公司的TVP5150作为解码芯片。TVP5150 是一款超低功耗的解码芯片,正常操作时的功耗只有113 mW, 节电模式下功耗为1 mW, 并支持PAL/NTSC/SECAM 等格式, 它能将摄像头所采集到的模拟图像信号转换为YUV4:2:2 格式的ITU-R BT.656 数字信号, 它可以接收2 路复合视频信号(CVBS) 或1 路S -Video 信号, 通过I2C 总线设置内部寄存器, 可以选择输出8 位4:2:2 的ITU-R BT.656 数字信号( 同步信号内嵌), 以及8 位4:2:2 的ITU-R BT.601 信号(同步信号分离, 单独引脚输出)。TVP5150 与DM642 的硬件连接如图3 所示。

图3 TVP5150 与DM642 硬件连接图

TVP5150 芯片的AIP1A 和AIP1B 为模拟信号的输入端, 该引脚需接0.1~1 μF 的滤波电容,HSYNC 为行同步信号的输出引脚。由于本设计采用了同步信号内嵌的ITU-R BT.656 格式, 所以该引脚未与DM642 相关引脚相连接。PND 引脚为省电模式的控制信号输入端, 低电平有效, 与红外传感信号处理电路的输出信号Vo连接,当监控区域无行人走动时,Vo为低电平, 这将使TVP5150 芯片进入省电模式。YOUT[6:0] 为BT.656/YUV数据输出引脚,YOUT [7]/I2CSEL 是BT.656/YUV 数据的第7 位, 也是I2C 接口设备地址设置位,TVP5150 设备地址由I2CSEL 引脚所接的上拉电阻或下拉电阻确定,I2CSEL 引脚的状态与设备地址映射关系如表1 所示,DM642 和TVP5150 应答过程中需要从片TVP5150 的地址。SCL、SDA 分别为I2C 接口的串行时钟和数据引脚,DM642 对TVP5150 内部寄存器的访问通过I2C 总线实现。DM642 芯片的VP0D [19:0] 为视频口VP0 的数据总线引脚, 其中VP0D [8:2] 与多通道串行口McBSP0 引脚复用, 为了将VP0D [8:2] 配置为VP0 的低位数据引脚,需要把PERCFG 寄存器中的VP0EN 位置1。VP0CLK0 为外部像素时钟输入引脚, 与视频解码芯片TVP5150 的像素时钟输出引脚PCLK/SCLK 连接。

TOP2 基于DSP的视频监控系统硬件电路设计

目前视频监控广泛应用于安防监控、工业监控和交通监控等领域。视频监控系统大致经历3个阶段:首先是基于模拟信号的电视监控系统,其功能单一、易受干扰且不易扩展;随后出现基于PC机的图像监控系统,其终端功能较强.但价格昂贵,稳定性差;近年来,随着嵌入式技术成熟,嵌入式视频采集处理系统具有可靠性高、速度快、成本低、体积小、功耗低、环境适应性强等优点。

视频信号处理电路

本设计采用SONY公司专用信号处理器件CXD3142R作为信号处理器。CXD3142R是专用于对Ye,Cv,Mg和G补色单片CCD输出信号进行处理的低功耗、高效率的信号处理器;具有自动曝光和自动白平衡功能,可同时输出复合视频信号和YUV 8位数字信号输出。内部集成9位A/D转换器同步信号产生电路、外部同步电路和时钟控制电路。此外,CXD3142R还具有串口通信功能,用户可在PC机中预先设定好DSP中的寄存器值,通过串口下载到DSP,并对图像信号进行自动曝光和自动白平衡等处理。图2为视频信号处理模块电路连接图。

图 2中,H1,H2,XVl,XV2,XV3,XV4是CCD图像传感器的时序驱动信号,EEPROM用来存储DSP初始化的寄存器值。D0~D7是YUV 数字信号。其具体工作流程:将CCD图像传感器采集的模拟信号经CXA2096N进行相关预处理后,相应数字信号经VIN引脚传给 DSP(CXD3142),DSP接收数字信号后,利用其内部AE/AWB检测电路、同步信号产生电路、外同步电路以及相关算法对其进行相关处理,处理完成后在行(H引脚)、场(V引脚)信号及时钟信号(PCLK)的控制下将8位数字信号经过D0~D7引脚传给FPGA模块进行相关处理。通过引脚SCK、 SI、SO、XCS串口通信,通过CSROM、CASI、CSASO、CASCK引脚与外部EEPROM通信,实现DSP相关的初始化。此外,IO引脚输出经DSP处理过的复合视频信号,通过相关接口直接在CRT显示器上显示图像处理结果。

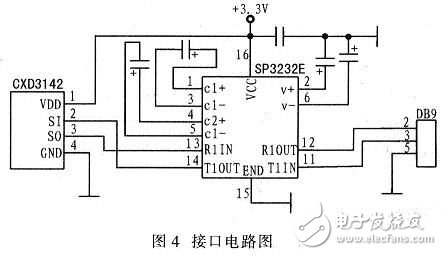

外围接口模块设计

本设计支持RS-232C串口通信。但该串口通信需把3.3 V逻辑电平转化成RS-232C标准电平。因此采用SP3232E系列器件完成电平转换。SP3232E可从+3.0~+5.5 V的电源电压产生2Vce的RS-232C电压电平。该系列适用于+3.3 V系统。SP3232E器件的驱动器满载时典型数据速率为235 kb/s。图4为系统设计的接口电路图。

需要注意的是,由于采用SP3232E器件,其驱动能力有限,该接口电路只适用于近距离传输。如果要进行远距离传输,则必须加强信号传输能力。

智能视频监控信号采集电路模块设计

矩阵切换器电路设计

本系统设计的是容量为32路音视频的监控,为简化设计,及调试、安装、升级等的方便,32路音视频不在一块PCB板上处理,而是分成4块子板,每块子板处 N8路音视频,实现8路音视频通道的8选1输出功能,即4块子板组成一个矩阵切换器,在同一时间实现32选4输出功能。每块子板的电路图如图3所示。

语音信号采集与处理电路设计

因为要采集教室各个位置(一般在20~50m2范围内)的语音信号,使用普通的话筒放大电路显然达不到要求。本系统采用对数放大电路进行语音放大,比较清晰地采集到了50m2范围内各个位置的语音信号。设计的对数放大电路如图5所示。IC2为运算放大器,系统选用LM358实现二级运算放大。

利用传感技术和电子技术系统设计思路简单、成本低廉、方便实用。对提高学生自主学习的自觉性,监控自主学习设备和软件平台运行情况,防止人为破坏造成的不必要损失,提高设备运行的稳定性和可靠性等起到了非常重要的作用。

欲了解更多视频监控相关解决方案与电路图设计,可关注电子发烧友荣誉出品的Designs of week栏目:

TOP3 智能视频监控系统以太网电路设计

视频监控系统以其直观、方便等特点,一直应用于许多场合。随着嵌入式系统和通信技术的快速发展,传统的基于模拟信号的监控方式己经不能满足日益增长的市场需求。本文在深入研究ARM体系结构、Linux软件结构、视频服务器之上,将基于ARM的嵌入式开发方法与网络技术相结合,实现了基于 S3C2440和嵌入式 Linux的远程图像监控系统。

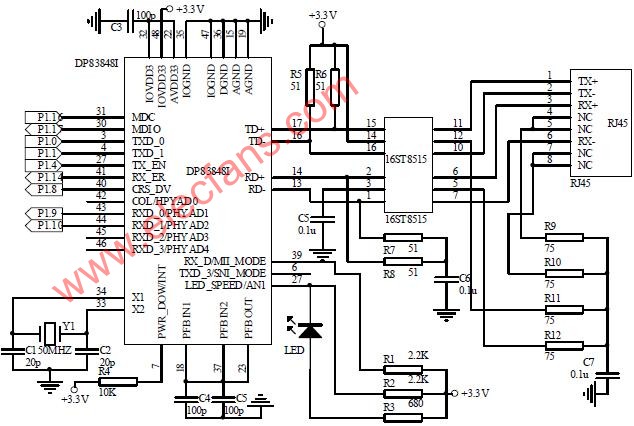

以太网电路模块设计

基于以太网的网络连接最典型的应用形式是Ehernet和TCP/IP的组合,它的底一层是以太网,网络层和传输层采用国际公认的标准TCP/IP协议。本系统中采用的是Crystal公司的CS8900,该芯片是一款单口的10/ 100Mbps快速以太网物理层接口芯片[8]。它与S3C2440的接口电路如图所示。

简易智能视频监控切换器电路设计

电路原理:电路的核心是一块视频切换电路MAX454。它具有质量良好的输出图像和很低的相位失真特点。电路内部包含4路视频输入(IN0~IN3)和一个低输入阻抗的线路放大、驱动器,两个地址输入(A0、A1),一个视频输出和两个电源端子。监控镜头通过J1-J4与切换器视频输入端相联。75Ω电阻构成输入的终端电阻。内部放大器的增益由接在IC1的13脚的反馈网络设置。反馈网络由R5-R8和C3构成。其增益设置为2是为了补偿在终端电阻R9(75Ω)上的消耗。最后在输出端J5的增益为1。由于电路用于处理高频的视频信号,我们在制作时应注意必需要采用印刷电路板,请特别注意在信号端子周围需用接地铜箔保护,以免引入噪声和串扰。在安装元器件时,建议先焊装电阻和二极管,然后用前面的零件剪下来的引线用做两根跳线。之后是S1和IC2、IC3的插座,但是 IC1不要使用插座。在这之后是 Q1~Q4及电容和LED1。最后将IC1直接焊接在电路板上,并尽可能缩短接脚引线以有利于信号传输。它采用视频切换专用集成电路,可以将两、三或四个镜头的监控画面依次显示在一个监视器上。切换镜头的数量由电路板上的DIP开关设定。在自动模式下,镜头的切换速度可由面板上的旋扭从1到20秒之间调整。手动模式时,可将一路监控镜头画面固定在监视器上,并可通过手动触发开关来逐个控制切换监控镜头。 电源部分由T1、IC4、IC5和D5、D6及C6~C9构成±5伏电源。

基于视频监控系统图像传感器接口电路模块设计

电路原理:OV9650 与处理器的接口包括SCCB接口、数据输出接口和控制接口等3 部分。SCCB 接口起到传递处理器提供的初始化OV9650内部寄存器参数的作用, 其数据线SIOD 和时钟线SI-OC, 相当于I2C 总线中的SDA 与SCL。也就是说, SC-CB 起到I2C 总线的作用。OV9650 是I2C 总线的从器件, S3C2440 是对应的主器件。I2 C 总线采用串行方式从高位到低位传输字节数据, 每个字节传输完后, 主控制器将SDA 置为高电平并释放, 等待从设备发送确认信号。OV9650 内嵌了一个10 位A/ D 转换器, 对应有10 个数据输出口D[ 0: 9] 。输出图像数据的格式可以为10 位原始RAW, RGB 或经过内部DSP 转换的8 位RGB/ YCbCr。本系统选择的微处理器芯片S3C2440的CAM IF 单元支持8 位的YU V/ YCbCr 格式, 故需将OV9650 的数据接口D[ 9: 2] 与CAM IF 的数据口CAMDAT A[ 7: 0] 相连接。OV9650 的XVCLK 用于接收CPU 输出的24 MHz 的工作时钟。OV9650 内部产生的帧同步信号VSYNC、行同步信号HREF、像素时钟信号PCLK 等3 个时钟信号传入ARM 芯片中, 用于控制图像采集。每一个VSYN C 脉冲表示一帧图像数据采集的开始, HREF 的高电平则表示采集一行图像数据, 图像传感器按从左到右的顺序在每个PCLK脉冲过程中依次采集一个字节的数据, 直到一帧图像数据全部采集完成。摄像头使用的是CAM130 模块, 其中的图像传感器为OV9650, 该部分原理图及接口电路如图2 所示。

图2 CAM130 模块原理图及OV9650 接口电路

TOP4 智能视频监控终端电路模块设计

红外传感信号处理电路模块设计

本终端采用红外传感器来检测监控区域有无人员进入, 只在有人员进入监控区域时, 终端才进入图像采集、处理、传输状态。本设计采用BISS0001芯片为热释电红外传感信号处理核心元件, 其应用电路如图2 所示。

图2 红外信号处理电路

图2 中,7805 为三端稳压集成电路, 为信号处理电路提供电源。BISS0001 芯片的第9 引脚为触发控制信号Vc的输入脚, 工作中应当保证输入电压, 可以通过调节电阻R3来达到目的。当有行人进入监控区域时, 热释电红外传感器PIR 将检测到的人体发出的红外线转化为电信号, 并将其送到BISS0001内部, 信号经BISS0001 处理后由2 脚输出, 输出Vo为低电平到高电平的跳变。如果BISS0001 工作在有效状态不可重复触发的情况下, 高电平的持续时间为Ts (Ts=49 152 R1C1), 在Ts时间段结束时,输出Vo即刻由高电平进入低电平并被封锁Ti (Ti =24R2C2 ) 时长; 对于有效状态可重复触发的情况来讲( 即图2 中S1 接高电平), 如果在前一Ts时间段内, 输入的变化使得输出有效状态再次触发, 则Vo高电平信号将从此刻算起再持续一个Tx时长, 之后才转换为低电平并进入封锁时间Ti。在封锁时间内, 即使由于负载的切换而引入的干扰也不会改变输出Vo的状态。本设计中让S1 接高电平, 红外传感信号处理电路的输出信号Vo作为DM642 的外部中断信号, 将Vo与DM642 的GP[5:4]连接, 同时也作为TVP5150 芯片的节电模式输入控制信号。

图像采集电路模块设计

对于图像采集模块, 采用TI 公司的TVP5150作为解码芯片。TVP5150 是一款超低功耗的解码芯片,正常操作时的功耗只有113 mW, 节电模式下功耗为1 mW, 并支持PAL/NTSC/SECAM 等格式, 它能将摄像头所采集到的模拟图像信号转换为YUV4:2:2 格式的ITU-R BT.656 数字信号, 它可以接收2 路复合视频信号 或1 路S -Video 信号, 通过I2C 总线设置内部寄存器, 可以选择输出8 位4:2:2 的ITU-R BT.656 数字信号, 以及8 位4:2:2 的ITU-R BT.601 信号(同步信号分离, 单独引脚输出)。TVP5150 与DM642 的硬件连接如图所示。

图3 TVP5150 与DM642 硬件连接图

TVP5150 芯片的AIP1A 和AIP1B 为模拟信号的输入端, 该引脚需接0.1~1 μF 的滤波电容,HSYNC 为行同步信号的输出引脚。由于本设计采用了同步信号内嵌的ITU-R BT.656 格式, 所以该引脚未与DM642 相关引脚相连接。PND 引脚为省电模式的控制信号输入端, 低电平有效, 与红外传感信号处理电路的输出信号Vo连接,当监控区域无行人走动时,Vo为低电平, 这将使TVP5150 芯片进入省电模式。YOUT[6:0] 为BT.656/YUV数据输出引脚,YOUT [7]/I2CSEL 是BT.656/YUV 数据的第7 位, 也是I2C 接口设备地址设置位,TVP5150 设备地址由I2CSEL 引脚所接的上拉电阻或下拉电阻确定,I2CSEL 引脚的状态与设备地址映射关系,DM642 和TVP5150 应答过程中需要从片TVP5150 的地址。SCL、SDA 分别为I2C 接口的串行时钟和数据引脚,DM642 对TVP5150 内部寄存器的访问通过I2C 总线实现。DM642 芯片的VP0D [19:0] 为视频口VP0 的数据总线引脚, 其中VP0D [8:2] 与多通道串行口McBSP0 引脚复用, 为了将VP0D [8:2] 配置为VP0 的低位数据引脚,需要把PERCFG 寄存器中的VP0EN 位置1。VP0CLK0 为外部像素时钟输入引脚, 与视频解码芯片TVP5150 的像素时钟输出引脚PCLK/SCLK 连接。

基于DSP的智能视频监控图像处理电路模块设计

本监控系统采用一片TI的TPS3307-33D作为电源检测IC。该器件定义在其供电1.1V时其 /Reset即可输出有效的信号。如图4所示,在本系统中,该电路可以完成对5V、3.3V和1.8V三种供电电压的监测,并可以对系统的三种器件(C6211、EPLD和 AT89C2051)同时进行上电复位和手工复位。

图4 TPS3307电源监控电路

其中+3.3V是TMS320C6211的I/O接口所需的电压,这是DSP外围接口电压,必须能够保持稳定、持续供电。其外接的SDRAM和 FLASH ROM都是3.3V器件,若电压不稳,这些器件无法稳定工作,容易导致损耗甚至烧毁这些器件。+1.8V供电是为了满足TMS320C6211的CPU核心工作电压需要。对于TMS320C6211来说,其工作频率为150MHz,对电压的变化非常敏感。电压过高会使器件损伤,电压过低芯片会自动复位。

TOP5 基于TMS320DM643的视频监控系统电路模块设计

视频编、解码电路模块设计

视频解码模块的主要功能是将从摄像头采集来的PAL/NTSC复合视频信号进行采样、量化得到任意分辨率的数字信号,为DM643提供视频流。视频解码器选用的是TI公司的TVP5150视频解码芯片。该芯片是一个高性能数字视频解码器,可以将NTSC/PAL制模拟视频信号转换成BT.656格式的标准数字视频信号。下面是视频解码的滤波部分电路图:

图2 滤波电路图

视频解码器TVP5150视频信号输入范围为0.75Vpp,而外部视频信号输入范围一般为1Vpp,所以外部视频输入与TVP5150视频输入之间串接到地分压电阻网络,以达到TVP5150所需的输入电平。DM643支持标准的BT.656格式的数字视频数据流的输入格式,能与TVP5150的视频数据流进行无缝连接。

串行通信电路模块设计

该模块实现的功能是DSP芯片通过异步串行总线RS-485向机械控制电路(云台)发送指令,实现摄像头的自动跟踪。该系统采用的是TL16C752通用异步收发器UART,它采用8位异步并行存储器接口,并采用+3.3V电源供电,可以与DM643的外部存储器接口(EMIF)直接连接。

图4 串口连接图

一种3G移动视频监控系统电源电路模块设计

系统电源分为+5V、+3.3V、+1.8V、+1.2V 四种,系统主供电电源为+5V,其余均由+5V 电源供给。因此,采用一片TPS75003 和一片TPS62040 完成系统四种电源的转换。设计用TPS75003 的SW1 引脚经过SI2323 续流整形后输出1.2V 电压用于DM6446 内核供电,IS1 引脚连接参考电压,FB1 引脚接输出1.2V 电压作为反馈,SW2 引脚输出3.3V 电压用于DM6446 外设接口供电。TPS62040 的SW1 和SW2 引脚短接后输出1.8V 电压用于DM6446 存储器接口供电,FB 引脚连接1.8V 作为反馈输入。这样,用一片TPS75003 和TPS62040 电源管理芯片就可以满足本系统供电。TPS75003 和TPS62040电源转换电路如图2 所示。

图2 TPS75003 和TPS62040 电源转换电路图

TOP6 基于Internet的智能视频远程监控系统电路模块设计

在ARM9和ARM11后的就是当下最热门的ARM- Cortex内核,该内核是ARM公司最新的内核,增加了众多的中断控制器,内核效率更高,单位执行代码效率也更高,Cortex系列分为三个子系列有A 系列,R系列,M系列。A系列主要面向应用类的,更加高端,主频也更快等优点;R系列主要面向于实时控制,主要有响应特别快等优点;而M系列主要面向微控制器,特点是低功耗,低成本,适合低端控制场合。

主控电路采用TI公司的Stellaris系列的LM3S8962,由于我们考虑了是自己制板,因此我们的MCU做成了最小系统板,主控芯片的电路如下。

图4-1 主控芯片

摄像头电路设计

本课题所采用的摄像头是数字接口的,因此接线很简单,八根数据线与摄像头的灰度图像输出信号,MCU直接通过GPIO口来读取数据。行中断和场中断的信号线需要加电容和电阻滤波,否则可能引起中断不稳定。

图4-2 摄像头接口电路

热敏电阻传感器电路设计

热敏电阻一般分为正温和负温两种,根据其灵敏度不同,采用合适的热敏电阻在合适的场合使用,如果需要精度很高的话可以采用PT-100铂电阻,需要电桥电路配合信号处理,并且需要非线性校正,而我们的方案是的同工电阻分压通过AD来采集数据,进行简易的处理之后就可以通过上位机显示。

图4-4 温度传感器电路

时钟电路设计

时钟电路采用外部的DS1302电路,由于ARM内部也集成了RTC,因此本系统中可以使用两套时钟,该时钟有外部钮扣电池供电,不会因为系统掉电而停止运行,时钟芯片与主芯片通过串行通信进行配置和传输数据,使用很方便。

图4-5 时钟模块

TOP7 基于89C51单片机的智能视频监控系统控制电路设计

系统硬件电路设计

本系统采用89C51单片机与PC键盘接口相连,图2给出了系统硬件电路原理。其中P3.0和P3.1分别与主机键盘接口的时钟线CLK和数据线 DATA相连,P2口与4×4键盘矩阵相连,P0口经过驱动后与输入输出报警设备相连接。为保证键盘可靠工作,系统配置了看门狗电路MAX813L,另外,系统还配置了蜂鸣器,每次按键均有声音提示。

图2 系统硬件电路原理

两种智能视频监控系统中矩阵切换电路设计

介绍了两种基于不同芯片组合的矩阵切换-字符叠加系统,包括这两种实现方案的元件构成、结构框架、工作原理和它们各自的特点及应用范围。当系统视、音频信号的输入、输出通道不是很多,尤其在输出通道较少且不需要汉字字符叠加的情况下,该文豪以获得较高的性价比。

电路原理:在设计中,输入8路视频信号经过标题、时间叠加后送去录像,同时送往矩阵切换电路选出一路进行监视。监视时可采用自动定时切换或手动切换。计了较多的面板按键。同时8路叠加芯片的片选线、数据线、CLK线以及切换模块CC4051的地址线也较多,从而造成89C52单片机的 I/O口比较紧张。为了解决这个问题,采取了三种办法:(1)使用移位寄存器,用CPU串口扩展I/O口来控制面板按键;(2)视、音频信号切换和音量切换的6根地址线均从P1口引出,同时8路叠加芯片共用数据线、CLK线,这两根线也从P1口引出;(3)CPU的P0口蚋射为总线方式,控制时钟芯片 DS12887。同时P2口映射为I/O口方式,控制8路叠加芯片的片选信号。在设置存储系统的信息时,若信息量不是很多,可以不外扩RAM,而将设置信息保存在时钟芯片DS12887中,其内部含有114个字节不挥发的RAM。另外在设置标题、时间等信息时,采有了菜单界面方式,同时使用叠加芯片 μPD6450提供的内部彩色视频信号,既美观也方便用户操作。

大容量、汉字字符叠加系统电路设计

电路原理:当系统视、音频信号的输入、输出通道数较多,且需要进行汉字字符叠加时可以采用该方案。在设计中,48路输入视频信号经过矩阵切换后输出12路信号,然后送往字符叠加模块进行汉字标题和时间的叠加,最后送往12路监视器。整个系统分为三个模块,控制模块、矩阵切换模块和字符叠加模块。下面介绍各模块主要元件的构成。

元件构成控制模块

TOP8 基于DSP+FPGA多视频监控的采集电路模块

视频采集电路模块设计

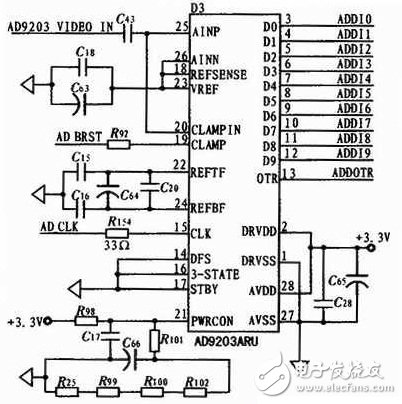

AD9203是ADI公司出品的一款单通道、低电压的高速A/D转换器,采样速率可达40 Ms/s。其精度稳定可靠,在全采样带宽范围内,始终基本保持着10位的精度;在40 Ms/s的采样速率下,ENOB(有效位数)仍然达到9.55位,差分非线性度±0.25 LSB,信噪比和失真度保持在59 dB左右。AD9203的工作电压比较灵活,允许住2.7~3.6 V范围内变动,特别适合于便携式设备在低电压下的高速操作。在3 V的供电下,40 Ms/s全速工作时,功耗只有74 mW;在5 Ms/s时,功耗将会降到17 mW,在待机模式下,功耗只有0.65 mW。对于输入信号的峰峰值,通常设置为1 Vp-p或者2 Vp-p。另外,AD9203允许外部电压参考,可以根据设计需要,在1~2 V间灵活地设置输入信号的峰峰值。

图2 AD9203的电路应用原理图

基于ARM9的远程无线智能视频监控电路设计

图像采样接口电路设计

S3C2440的摄像头接口支持ITU-R BT.601/656 YCbCr8比特标准的图像数据输入,最大可采样4096×4096像素的图像。摄像头接口可以有两种模式与DMA控制器进行数据传输:一种是P端口模式,把从摄像头接口采样到的图像数据转为RGB数据,并在DMA控制下传输到SDRAM;另一种是C端口模式,把图像数据按照YCbCr4:2:0或 4:2:2的格式传输到SDRAM。上述两种工作模式都允许设置一个剪辑窗口,只有进入这个窗口的图像数据才能够传输到SDRAM。S3C2440的摄像机接口接收ITU标准的图像数据,不能直接接收CCD摄像机输出的模拟视频信号,因此还需要1片SAA7113视频解码芯片。

SAA7113 的CE 引脚与S3C2440 的一个GPIO 引脚相连,这样可以控制SAA7113的工作状态。当无须采集图像时,将该GPIO口输出低电平,使SAA7113芯片处于低功耗状态,节省电能的消耗。对照图2和图3可以看出,SAA7113芯片就是图2的“外部图像传感器”。它向嵌入式系统的摄像机接口提供了采样到的标准ITU视频数据。这些数据经过 DMA的P端口或C端口控制传输到了内存,这样就可以在内存中对图像数据作进一步的加工处理。

摄像机云台控制电路设计

摄像机的云台控制接口采用RS485通信方式。因S3C2440内部只有RS232的控制器,为此使用MAX485芯片设计了一个RS232到RS485的转换接口。该电路原理如图4所示。

远程图像无线监控系统在高压输电线路的覆冰监测中得到了成功的应用。在野外全天候环境下,适时准确地监测高压输电线路覆冰厚度,同时发出预警处理信息,从而有效地避免了断缆事故的发生。远程图像监控技术是随着计算机技术、数字通信技术、网络技术、自动控制技术以及LSI、VLSI集成电路的发展而发展的,而基于ARM9嵌入式处理器的本系统正是这些技术学科相互交叉和融合发展的集中体现。实践证明,ARM9处理器的低功耗、高性能和多功能的特性满足了远程图像监控的许多特殊需求,是实现远程图像监控的很好选择。

TOP9 基于CC2530的无线路灯节能智能监控系统电路设计

ZigBee 新一代SoC 芯片CC2530 是TI 公司推出的用于嵌入式应用的片上系统,是使用IEEE 802.15.4 标准、ZigBee 和ZigBee RF4CE 的一个片上系统解决方案。CC2530 内部已集成了一个8051 微处理器与高性能的RF 收发器。CC2530 能够以非常低的总材料成本建立强大的网络节点, 拥有较大的快闪记忆体, 其存储容量多达256 B, 它是理想的ZigBee 专业应用芯片; 支持新RemoTI 的ZigBee RF4CE, 这是业界首款符合ZigBeeRF4CE 兼容的协议栈。此外,CC2530 具有不同的运行模式, 使得它尤其适应超低功耗要求的系统, 运行模式之间的转换时间短, 进一步确保了低能源消耗。图3 为CC2530 外围电路设计。图 中的D3 倒F 天线是单端天线, 也就是非平衡天线, 所以需要用电容、电感组成一个非平衡变压器(BALUN) , 如图 中的虚线框图, 来满足RF 输入/输出匹配的要求。

图3 CC2530 外围电路

PCB 天线设计难度较大, 通常还需要仿真工具的支持, 但TI 公司已经把倒F 型PCB 天线设计的规格公布了。对于终端设备的设计来说,PCB 天线不失为一种较经济的选择, 因为其通信距离可以满足本系统的要求。路灯节点设计采用光敏电阻传感器检测的方式采集路灯状态信息并通过无线传回主控中心( 协调器), 同时经主控中心处理后, 将相应的控制命令发送至指定的路灯节点。协调器的设计是根据电子时钟产生的精确时间和光敏电阻采集外界光线的强弱来控制整个网络的路灯。在下半夜采用隔柱亮灯(开部分灯) 的方法降低电能消耗; 在大白天, 采用关全部路灯的方法, 如果天气突然转阴, 系统就会自动打开部分路灯, 满足人们照明要求; 傍晚时分, 用光敏传感器采集的光线强弱来判断是否需要开关灯, 做到及时开关灯。根据以上的控制实现智能和节能控制。表1 所示的为协调器主控制路灯的状况( 此表要根据城市的实际情况制定)。

视频信号选择电路的设计

系统外部前端设备摄像机录入各个门禁场所视频,通过视频传输线路传到主机控制系统的视频信号选择电路视频信号。选择电路具有四路视频输入、四路视频输出,一个公共视频端输出。一方面视频信号经过MAX4090进行阻抗匹配后从四路视频输出,供管理人员查看门禁的现场活动情况,同时在公共视频端不仅可以输出一路视频,而且可以通过视频处理板对视频信息进行存储并通过网络传输视频信息;输出的视频信号通过FPGA的控制转换为可视信号并存储到PC中,同时 FPGA可以不断检测视频警报信号量来触发报警信号。

如图2所示为只有1路输入,1路输出并带有一路公共视频的电路图作为视频选择电路系统的讲解示意,J1为视频信号输入端,J5,J9为视频信号输出端.CON2为短路跳线对相应的通道进行连通与断开。当CON2断开时,相应的通道连通,视频信号从左边输入,经过匹配后从右边输出;当CON2连通时,则视频信号输入后不能经过匹配处理而直接输出。然后利MAX4090用进行阻抗匹配进行多路视频的选择输出。该电路使用了交流耦合输出方式。从技术特征出发,将视频信号输出到媒体显示设备的最普遍方法是交流耦合,这使得接收电路可以在自己的输入端建立共模电平,该电平独立于输入视频信号的直流电平。一个 75欧的串联电阻应该尽可能近地放在靠近输出端的位置,这有助于隔离从输出端产生的下行寄生干扰,并提供最佳的信号条件。

USB接口电路的设计

为了方便的使用USB摄像头及USB的数据下载通道,系统总需要设计USB接口电路。

USB电路如图3所示,USB功能采用常见的CH375芯片作为USB借口控制芯片。CH375是一个USB总线的通用借口芯片,支持USB-HOST 主机方式和USB-DEVICE/SLAVE设备方式。 在本地端,CH375具有8位数据总线和读、写、片选控制线以及中断输出,可以方便地挂接到单片机/DSP/MCU/MPU等控制器的系统总线上。在 USB主机方式下,CH375 还提供了串行通讯方式,通过串行输入、串行输出和中断输出与单片机/DSP/MCU/MPU等相连接。CH375有串口和并口两种与单片机的连接方式,在本系统中,CH375 芯片是通过并行方式连接到副控制芯片的,CH375的 TXD引脚通过1千欧左右的下拉电阻接地或者直接接地,从而使CH375工作于并口方式。这种并行连接方式极大的提高了数据的传输速率。

TOP10 FPGA的EPROM及单片机存储电路设计

系统中使用了AT24C512EEPROM器件作为主要存储芯片,它的存储容量为512K及单片机对AT24C51系列E2PROM的读写操作完全遵守 12C总线的主收从发和主发从收的规则。数据的传送由四部分组成:起始(START)条件、从机地址的发送、数据的传送和停止(STOP)条件。每一个时钟高电平中期间传送一位数据,而且在SCL线为高电平时SDA线上的数据必须保持稳定,否则将认为是一个控制信号。这样设计的优点体现在其简单性和有效性上。

如图4所示电路,一般A0、A1、WP接VCC或GND,SCL、SDA接上拉电阻(上拉电阻的阻值可参考有关数据手册选择,通常可选5K到10K的电阻,本设计中选用的电阻阻值为10K)后再接单片机的普通I/O口,即可实现单片机对AT24C512的操作。在对AT24C512开始操作前,需要先发一个8位的地址字来选择芯片以进行读写。其中要注意“10100”为AT24C512固定的前5位二进制;A0、A1 用于对多个AT24C512加以区分;R/W为读写操作位,为1时表示读操作,为0时表示写操作。AT24C512内部有512页,每一页为128字节,任一单元的地址为

16位,地址范围为0000—0FFFFH。虽然FPGA芯片和单片机都有EEPROM读写的功能,但并不是说它们拥有各自独立的EEPROM芯片,而是两片单片机共同复用EEPROM芯片。如果两个芯片同时读写EEPROM芯片,则单片机肯定会产生死机现象,因此需要一个严格的机制保证不会出现两片单片机同时读或者写EPROM芯片的现象。该机制称为EPROM复用关系,即采用一个握手信号协调两者的使用。

在视频选择电路中采用了交流耦合技术,这样设计有利于保持高清晰视频信号的传输。同时利用FPGA作为中央控制部分的,采用了并行的两块单片机做为副控芯片,一块用于USB接口的数据控制与传输,另外一块用于其它接口操作和外部存储控制,既了协调视频信号的实时监控与传输,又能够保证FPGA的处理不受到外部电路的影响,大大提高了系统的工作效率。

欲了解更多视频监控相关解决方案与电路图设计,可关注电子发烧友荣誉出品的Designs of week栏目:

电子发烧友App

电子发烧友App

评论