3 设计实现

3.1 硬件设计

3.1.1 硬件架构

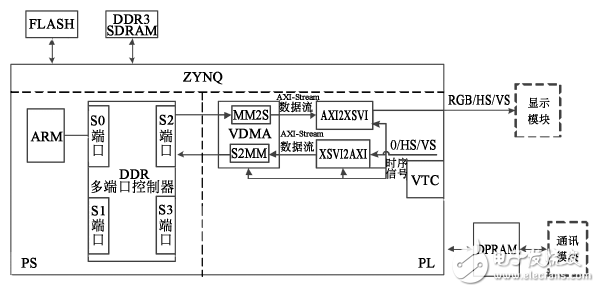

本文通过Zynq完成图形生成与显示功能,原理框图如图3所示,硬件模块主要包括Zynq、DDR3SDRAM、FLASH、双口RAM 等.正常工作时PS中的ARM 内核根据从双口RAM 中接收到的绘图指令和参数完成绘图算法,将图形数据写入DDR3SDRAM 存储器中.PL 从DDR3中读出图形数据进行显示,并对DDR3SDRAM中的图形数据进行清屏处理。

图3 Zynq图形生成原理框图

3.1.2 Zynq硬件平台设计

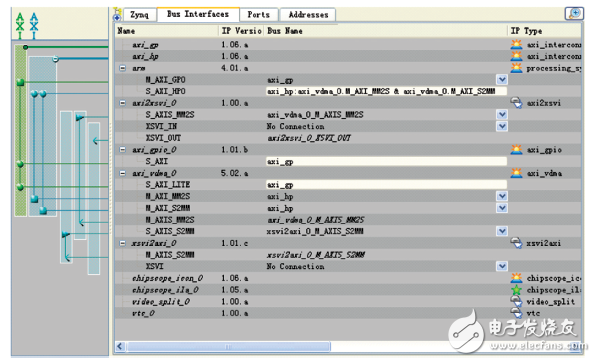

本文通过Xilinx 的ISE14.2 软件集成的XPS开发环境完成Zynq图形生成电路的硬件平台设计.利用XPS可以快速地对Zynq系统内的各种硬件资源进行定制设计,包括存储器、外设、ARM 处理器、系统IP和用户IP等.Zynq硬件平台结构图见图4所示.

图4 Zynq硬件结构图

本文在Zynq中的PL 部分应用了VDMA、AXI2XSVI、XSVI2AXI、VTC等几个IP核,其中VDMA 用于从DDR3SDRAM 中读出图形数据,同时向DDR3SDRAM 中写入全零数据以达到清屏目的.AXI2XSVI用于将AXIGStream 数据流用行、场同步信号进行区隔,供外部显示模块进行显示.XSVI2AXI用于将带有行场同步信号的视频数据转换成AXIGStream 数据流.VTC 用于生成系统运行所需时序信号.对VTC根据显示时序进行修改,系统即可产生多种分辨率图形画面。

3.1.3 图形缓冲设计

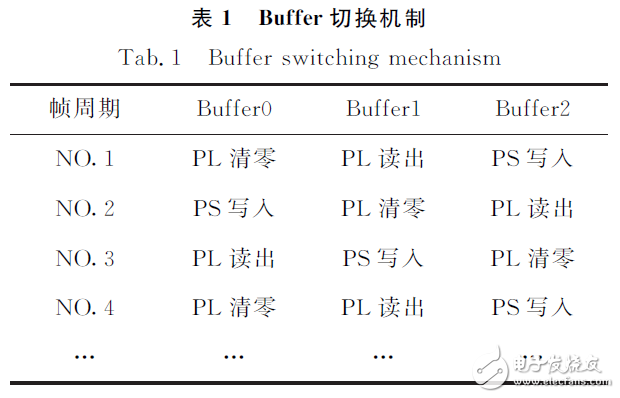

本文中对DDR3SDRAM 帧存的操作包括3种类型:PS写入、PL读取、PL清零.清零从本质上说也是一种写入操作,写入的是全零数据.读取和写入请求通过DDR 控制器中的调度机制和仲裁策略分别在不同时刻得以响应,得益于DDR3SDRAM 的高速高带宽优势,外部可以同时进行多个通道的读写操作.针对本文中DDR3SDRAM 的3种操作类型,在DDR3帧存中设置了3个缓冲区,分别为buffer0,buffer1,buffer2,相应地,VDMA 中的framebuffer数目也设置为3.buffer的切换机制如表1所示.

这种三缓冲切换机制保证了写入的都是已清零完成的buffer,清零的都是已读出完成的buffer,读出的都是已写入完成的buffer。

根据buffer切换机制,VDMA 中的S2MM和MM2S通道分别以指定的buffer为操作对象.初始化状态下为每个buffer指定默认的操作模式,而后在每个帧周期内启动VDMA 切换buffer操作模式,从而不间断地输出图形数据。

3.2 软件设计

3.2.1 Zynq系统软件

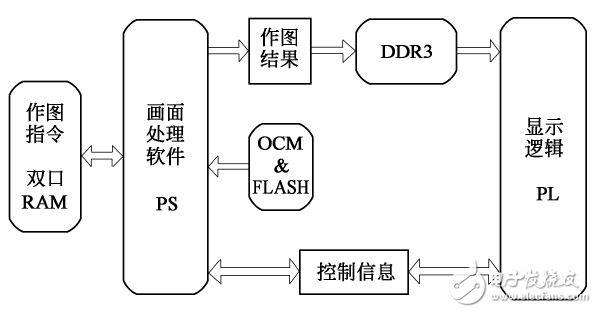

系统绘图时,根据双口RAM 提供的画面内容要求,启动绘图任务,并将绘图结果保存下来.显示工作完全由PL内部的显示逻辑负责,显示逻辑从显存中读取显示数据,按照标准时序送至显示接口.图形软件的接口关系如图5所示.

图5 图形生成软件接口示意图

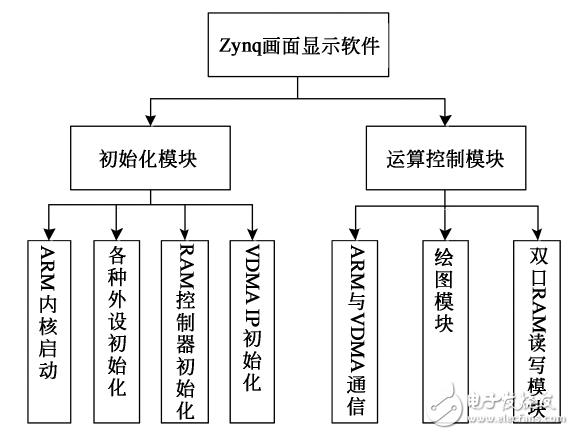

3.2.2 画面显示软件

画面显示软件主要包括初始化模块和主模块,结构如图6所示.初始化模块完成ARM 内核启动;外设初始化信息加载;DDR3SDRAM、UART等设备初始化;VDMA 寄存器配置等初始化工作.运算控制模块由双口RAM 读写模块;PS、PL 通信模块以及绘图模块3部分组成,其中双口RAM 读写模块主要负责从双口RAM中读取绘图指令数据,为绘图模块提供必要的绘图参数;PS、PL通信模块负责ARM 内核与VDMA的通信,切换缓存;绘图模块完成分配的绘图任务,并将相应的计算结果,也即对应的像素点信息写入DDR3SDRAM 中。

图6 图形生成软件结构图

电子发烧友App

电子发烧友App

评论