fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试? 在FPGA与DSP通讯时,同步时钟频率非常重要,因为不同的设备有不同的时钟频率,如果两者的时钟频率不同步,会导致通讯数据的错误或

2023-10-18 15:28:13 194

194 fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据? 在FPGA设计中,通常需要跨时钟域进行数据通信。跨时钟域通信就是在不同的时钟域之间传输数据。 当从一个时钟域传输数据到另一个时钟域

2023-10-18 15:23:51 154

154 本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 381

381

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0 。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 385

385

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 627

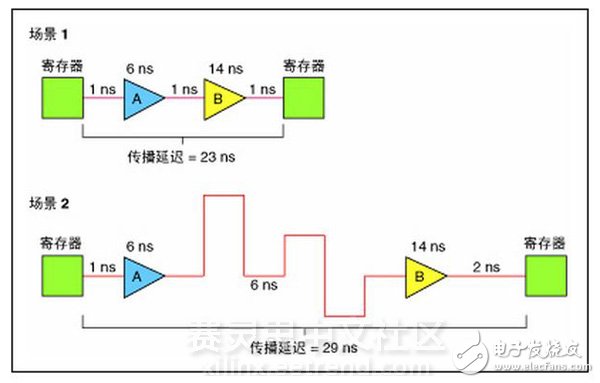

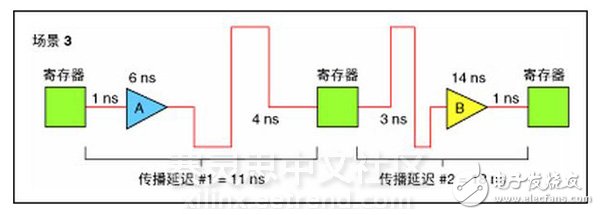

627 跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

2023-05-25 15:06:00 875

875

如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-04-07 09:42:57 401

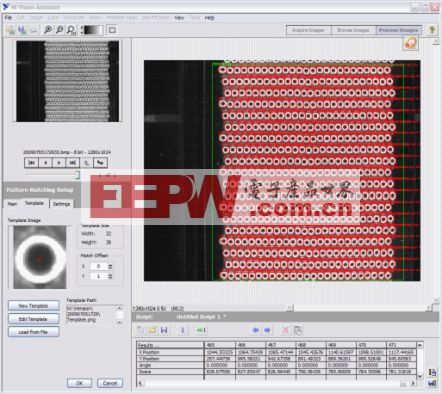

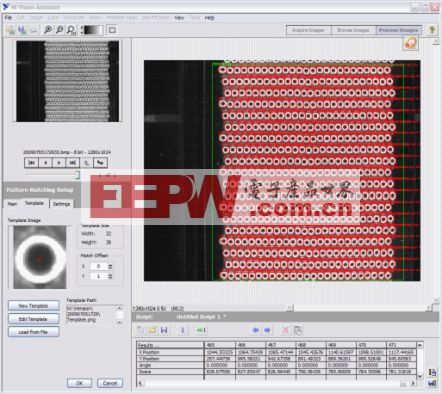

401 LABVIEW视觉模块的组成及系统说明

2023-02-17 13:52:27 1

1 时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源时钟同相,但

2023-01-05 14:00:07 645

645 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 586

586

当我刚开始我的FPGA设计生涯时,我对明显更小、更不灵活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常简单的时钟规则之一是尽可能只使用单个时钟。当然,这并不总是可能的,但即便如此,时钟的数量仍然有限。

2022-09-30 08:49:26 1082

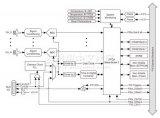

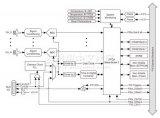

1082 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2156

2156 在外的高速PCB布线使还会带来串扰、信号完整性等非常严重的问题。如果可以在中低端FPGA上实现高速时钟数据恢复电路,则可降低成本且提高整个电路系统的性能。 &

2009-10-24 08:38:08

(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是

2021-12-29 19:41:48 6

6 (Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是

2021-12-29 19:41:38 5

5 Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产

2021-12-29 19:41:27 17

17 Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产品的设计

2021-12-29 19:41:17 2

2 Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产

2021-12-29 19:40:35 7

7 labview视觉中不同模块的使用综述

2021-09-10 16:16:22 31

31 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA中

2020-12-09 14:49:03 20

20 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2343

2343 时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 4370

4370

同步时序电路设计中最关键的是时钟设计, 随着电路规模与速度的提高, 对时钟的周期、占空比、延时和抖动等方面的要求也越来越高。为了顺应这需求, Spartan-6 系统器件在原有的DCM模块基础引入

2020-01-08 15:54:43 19

19 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 4795

4795

在本次演示中,NI的LabVIEW FPGA用于创建自定义视觉算法,使用3D非接触式测量提高精度。

LabVIEW FPGA还将LabVIEW图形化开发平台扩展到FPGA,使用户更容易使用

2018-11-22 06:09:00 3991

3991 NI FlexRIO是NI公司推出的FPGA应用的模块化产品,基于NI LabVIEW可重配置I/ O(RIO)架构的NI FlexRIO在一个平台中集成了高性能模块化I / O、功能强大的Xilinx FPGA以及基于PC的技术,是板载处理和实时分析应用系统的理想之选。

2018-07-05 09:11:00 2607

2607 LabVIEW可编程FPGA模块内嵌到示波器中,同时,内嵌到此系列示波器中的FPGA模块,可以通过LabVIEW FPGA开发工具进行重新编程和定向话设计,本系列示波器主要包括PXIe5170R,PXIe-5171R两种型号。

2018-06-30 07:37:00 3831

3831

内容包括:LabVIEW嵌入式产品族,FPGA技术,FPGA在系统中的重要性,简化的FPGA范例,图形化FPGA编程,图形化功能仿真,通信与I/O,商业现成可用的硬件(COTS),常见应用。

2018-06-25 13:01:00 4071

4071

对于利用LabVIEW FPGA实现RIO目标平台上的定制硬件的工程师与开发人员,他们可以很容易地利用所推荐的组件设计构建适合其应用的、可复用且可扩展的代码模块。基于已经验证的设计进行代码模块开发

2017-11-24 15:36:03 2055

2055

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8418

8418

介绍一种采用FPGA(现场可编程门阵列电路)实现SDH(同步数字体系)设备时钟芯片设计技术,硬件主要由1 个FPGA 和1 个高精度温补时钟组成.通过该技术,可以在FPGA 中实现需要专用芯片才能实现的时钟芯片各种功能,而且输入时钟数量对比专用芯片更加灵活,实现该功能的成本降低三分之一.

2017-11-21 09:59:00 1704

1704

"利用LabVIEW FPGA模块在NI PXI-7831R可重配置I/O板卡的FPGA上编程,不但使我们的系统性能超过了规格要求,还节省了90%的硬件搭建成本。"—— Matthew Viele

2017-11-18 18:24:14 1526

1526 开发和测试汽车电子、航空电子设备及数字传感器的工程师和设计师们,经常需要测量和模拟设备所产生的脉冲宽度调制(Pulse Width Modulation, PWM)信号。LabVIEW FPGA模块

2017-11-18 07:18:21 8848

8848

每个FPGA芯片(FPGA)是由有限个带有可编程连接预定义资源组成。这些互连资源通过LabVIEW FPGA模块实现用户设计的数字电路。用户创建FPGA VI时设计一个电路示意图,以说明FPGA逻辑

2017-11-18 05:57:01 646

646

相比其它FPGA设计工具,NI LabVIEW FPGA模块可帮助嵌入式设计人员使用更少的工程资源更快速地完成项目。LabVIEW FPGA 2014 中新增多项性能提升,可以帮助您使用最新的技术在

2017-11-18 04:44:58 3296

3296

NI FlexRIO设备包括了可采用NI LabVIEW FPGA模块进行编程的现场可编程门阵列(FPGA)模块,以及能提供高性能模拟和数字I/O的适配器模块。适配器模块是可互换的,并可以在

2017-11-18 02:30:02 1554

1554

通过LabVIEW 8.6实时模块中的新功能 - CompactRIO扫描模式,您可以在两个方案中选择其一:在无需对FPGA编程的情况下直接在LabVIEW Real-Time及主机应用程序中访问I

2017-11-17 08:55:09 2683

2683

一种基于FPGA 的将并行数据以SPI 串行方式自动发送出去的方法。 二、关键字: VHDL、FPGA、SPI、串行数据输出选择模块、移位脉冲产生模块、SPI 时钟采集信号和无相移的SPI 基准时钟产生模块、SPI 时钟输出选择模块、8bit SPI 时钟采集生成模块、16bit SPI 时钟采集生成

2017-10-19 10:33:01 18

18 基于异步FIFO在FPGA与DSP通信中的运用

2017-10-19 10:30:56 10

10 labview全模块

2017-04-19 16:57:48 85

85 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4128

4128 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 异步FIFO在FPGA与DSP通信中的运用

2016-05-19 11:17:11 15

15 通过 labview fpga定制硬件。

2016-05-17 17:47:59 24

24 [NI技术]-LabVIEW-FPGA代码模块设计,入门级资料。

2016-05-17 16:41:51 32

32 低功耗时钟门控算术逻辑单元在不同FPGA中的时钟能量分析

2015-11-19 14:50:20 0

0 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 借助NI LabVIEW,将嵌入式应用程序设计、建模并部署到各类处理目标(包括:现成的实时系统和基于FPGA的系统,以及自定义微处理器与微控制器设备)。包括LabVIEW RT模块、LabVIEW FPGA 模块

2012-08-01 15:47:49 369

369 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 997

997

将LabVIEW部署于联网可编程自动化控制器(PAC)以创建可靠的分布式监控系统,并连接现有的可编程逻辑控制器(PLC)和企业系统。 NI LabVIEW实时模块 实时执行跟踪工具包 NI LabVIEW FPGA模块 NI

2012-02-27 13:57:15 495

495 在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 177

177 为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定 FIFO 深度的方法。对FIFO不同深度的实验表明,采

2011-09-26 13:45:17 6638

6638

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3313

3313

提出了一种基于FPGA的时钟跟踪环路的设计方案,该方案简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方案能够使接收机时钟快速准确地跟踪发

2010-11-19 14:46:54 31

31 LabVIEW在全自动点胶机中的应用

挑战:运用LabVIEW+Vision+Motion的结合,迅速开发一套面向商用的全自动点胶机。

应用方案:应用NI的运动控

2010-05-13 10:18:30 2931

2931

对于利用LabVIEW FPGA实现RIO目标平台上的定制硬件的工程师与开发人员,他们可以很容易地利用所推荐的组件设计构建适合其应用的、可复用且可扩展的代码模块。基于已经验证的

2010-01-18 08:27:15 187

187 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 604

604

阐述了如何运用门控时钟来进行CMOS电路的低功耗设计。分析了门控时钟的实现方式,如何借助EDA工具在设计中使用门控时钟,并且附有部分脚本程序,以一个watchdog timer模块为例,给出

2009-11-19 11:49:37 22

22 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 影响FPGA设计中时钟因素的探讨:时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时

2009-11-01 14:58:33 26

26 基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 3352

3352

在虚拟仪器LabVIEW平台中串行通信模块的应用:本文介绍了虚拟仪器LabVIEW平台中含有的串行通信模块的应用,通过运用该模块,两台PC机、PC 机与单片机、PC 机与带有串口的测试仪器之间

2009-09-26 10:44:06 66

66 使用 LabVIEW FPGA 模块和可重新配置I/O 设备开发测量与控制应用通过使用LabVIEW FPGA 模块和可重新配置I/O(RIO)硬件,NI 为您提供了一种直观可用的解决方案,它可以将FPGA技术的灵活性

2009-07-23 08:09:28 65

65 摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1178

1178

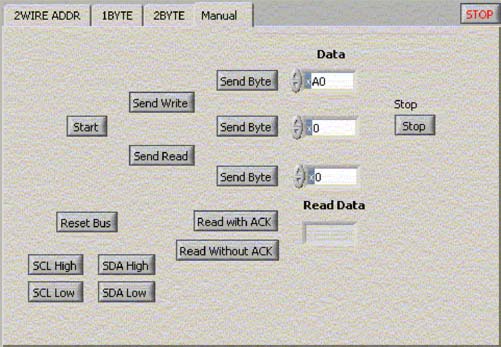

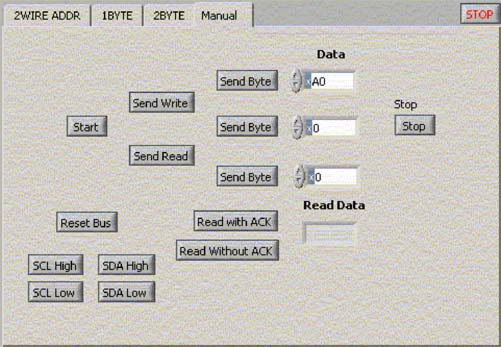

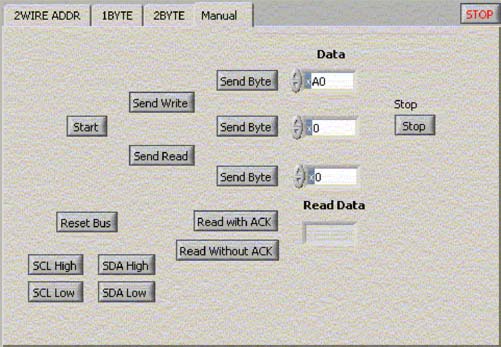

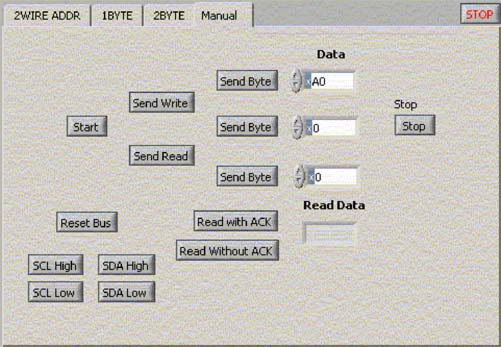

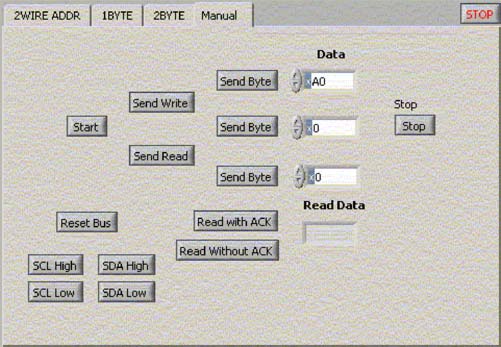

摘要:本篇应用笔记讨论了DS3900串口通信模块和LabView的使用问题,LabView是适用于嵌入式应用的图形化界面开发平台。本文可作为面向DS3900的LabView界面用户指南。

2009-05-07 11:30:40 473

473

精密参考时钟在时钟与数据恢复电路中的应用

2009-05-04 13:36:44 35

35 摘要:本篇应用笔记讨论了DS3900串口通信模块和LabView的使用问题,LabView是适用于嵌入式应用的图形化界面开发平台。本文可作为面向DS3900的LabView界面用户指南。

2009-04-28 11:38:27 698

698

运用LabView控制DS3900串口通信模块

本篇应用笔记讨论了DS3900串口通信模块和LabView的使用问题,LabView是适用于嵌入式应用的图形化界面开发平台。本文可作为面向DS3900的L

2009-01-06 13:52:39 1021

1021

LabVIEW8.5控制设计和仿真模块美国国家仪器有限公司(简称NI)宣布推出其NI LabVIEW8.5控制设计与仿真模块。作为LabVIEW图形化系统设计平台的扩展,该模块可以帮助

2008-05-19 13:34:43 1570

1570

电子发烧友App

电子发烧友App

评论