滤波器和接口设计程序

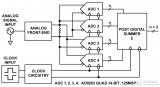

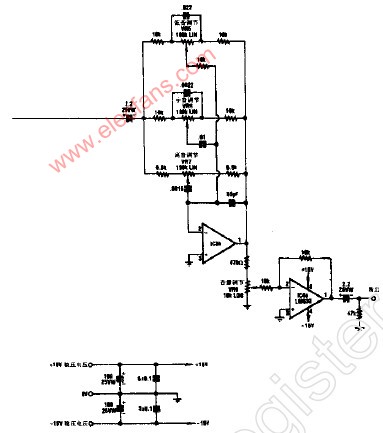

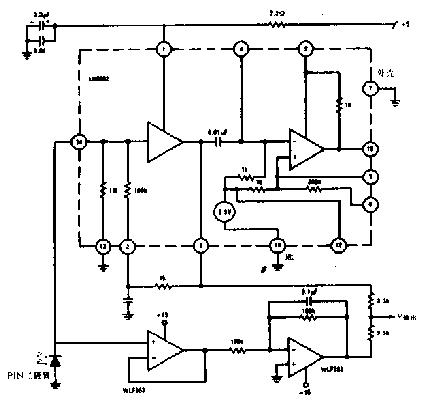

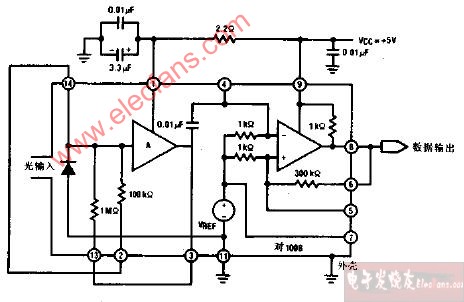

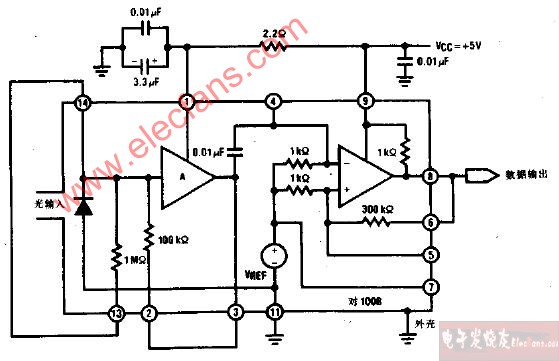

本节介绍放大器/ADC与滤波器接口设计的常用方法。为了实现最佳性能(带宽、SNR、SFDR等),放大器和ADC应对一般电路形成某些设计限制:

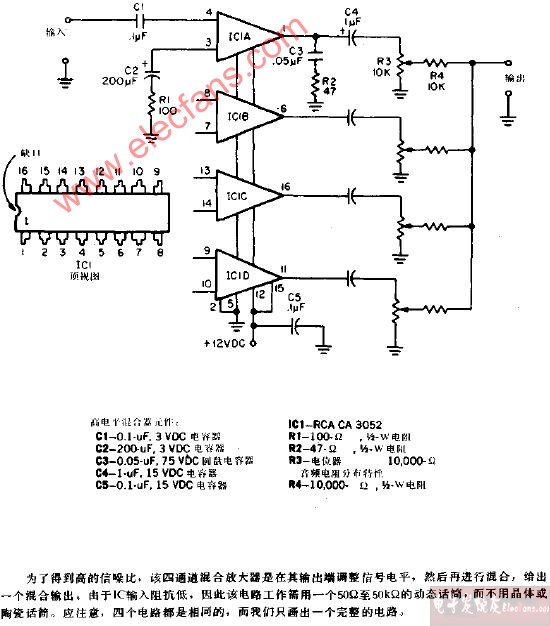

放大器应参考数据手册推荐的正确直流负载,以获得最佳性能。

放大器与滤波器的负载间必须使用正确数量的串联电阻。这是为了防止通带内的不良信号尖峰。

ADC的输入应通过外部并联电阻降低,并使用正确串联电阻将ADC与滤波器隔离开。此串联电阻也会减少信号尖峰。

此设计方法倾向于利用大多数高速ADC的相对较高输入阻抗和驱动源的相对较低阻抗,将滤波器的插入损耗降至最低。

设计程序的详情请参见电路笔记 CN-0227 和 CN-0238。

电路优化技术和权衡

本接口电路内的参数具有高互动性;因此优化电路的所有关键规格(带宽、带宽平坦度、SNR、SFDR、增益等)几乎不可能。不过,通过变更RA和RKB,可以最大程度地减少通常发生于带宽响应内的信号尖峰。

ADC输入端的串联电阻(RKB)应选择为尽量减少任何残余电荷注入(从ADC内部采样电容)造成的失真。增加此电阻也倾向减少带内的信号尖峰。

不过,增加RKB会增加信号衰减,因此放大器必须驱动更大信号才能填充ADC的输入范围。

优化通带平坦度的另一方法是略微变更滤波器分流电容。

ADC输入端接电阻(2RTADC)通常应选择为使净ADC输入阻抗介于200 Ω和400 Ω之间。降低该电阻可减少ADC输入电容的效应并稳定滤波器设计,但会增加电路的插入损耗。提高该值也会减少信号尖峰。

上述因素的权衡可能有些困难。本设计中,每个参数权重相等;因此所选值代表了所有设计特征的接口性能。某些设计中,可根据系统要求选择不同值,以优化SFDR、SNR或输入驱动电平。

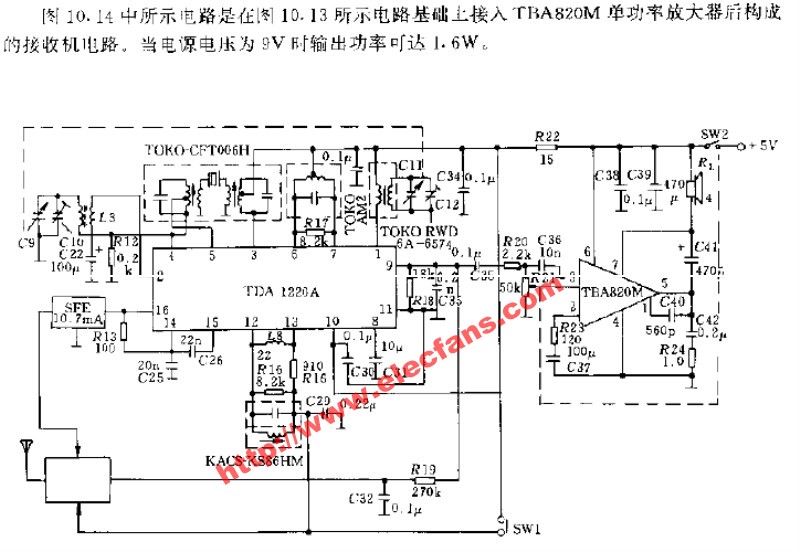

本设计中的SFDR性能取决于两个因素:放大器和ADC接口元件值,如图1所示。表1和图5所示的最终SFDR性能数字是在优化滤波器设计后获得的,考虑了用于滤波器设计的板寄生电容和非理想元件。

该特定设计中可以权衡的另一因素是ADC满量程设置。对于采用本设计获得的数据,满量程ADC差分输入电压设置为1.75 V p-p,它可以优化SFDR。将满量程输入范围更改为2.0 V p-p可稍稍改善SNR,但SFDR性能会略微降低。沿相反方向将满量程输入范围更改为1.5 V p-p可稍稍改善SFDR,但SNR性能会略微降低。

请注意,本设计中的信号与0.1 µF电容进行交流耦合,以阻挡放大器、其端接电阻和ADC输入之间的共模电压。共模电压的详情请参见AD6657A数据手册。

无源元件和PCB寄生考虑因素

该电路或任何高速电路的性能都高度依赖于适当的PCB布局,包括但不限于电源旁路、受控阻抗线路(如需要)、元件布局、信号布线以及电源层和接地层。高速ADC和放大器PCB布局的详情请参见教程MT-031和MT-101。

低寄生表面贴装电容、电感和电阻应用于滤波器内的无源元件。所选电感来自Coilcraft 0603CS系列。滤波器所用表面贴装电容的稳定性和精度是5%、C0G、0402型。

系统的完整文档请参见CN-0259设计支持包(CN0259-DesignSupport)。

常见变化

针对需要更少带宽和更低功耗的应用,可使用ADL5562差分放大器。 ADL5562的带宽为3.3 GHz。如需更低的功耗和带宽,还可使用 ADA4950-1。该器件的带宽为1 GHz,仅使用10 mA的电流。

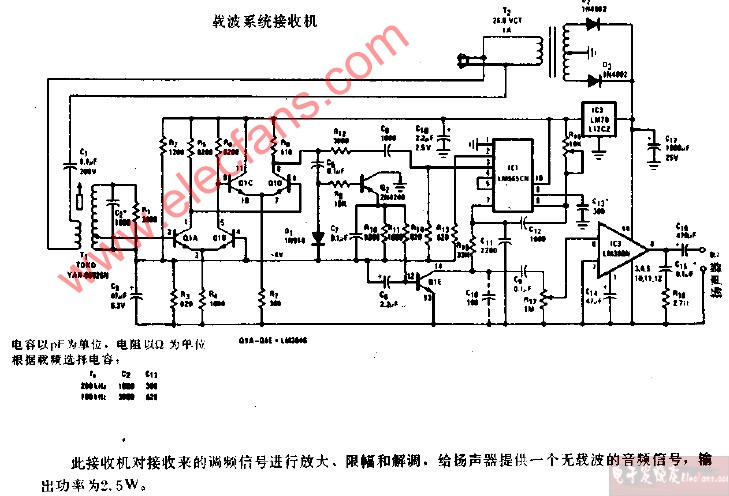

电子发烧友App

电子发烧友App

评论