布局考虑

该电路或其它任何高速/高分辨率电路的性能都高度依赖于适当的PCB布局,包括但不限于电源旁路、信号路由以及适当的电源层和接地层。有关PCB布局的详情,请参见指南 MT-031和MT-101以及“ 高速印刷电路板布局实用指南”一文。

系统性能

24位AD7192 Σ-Δ 型ADC可在该电路中提供非常好的性能。有关Σ-Δ 型ADC的更多详情, 请参见指南 MT-022 和 MT-023。

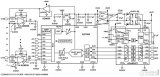

在配置设为斩波禁用、输出数据速率为4.7 Hz、增益为1且采用一个SINC4滤波器的情况下,噪声性能如图2所示,500个样本的噪声分布直方图则如图3所示。该电路中测得的峰峰值噪声约为 3.9 μV(见图2),均方根噪声为860 nV。这相当于峰峰值(无噪声码)分辨率为20位,均方根分辨率为23位。表3显示了斩波禁用且采用一个SINC4滤波器时一些数据速率和增益设置条件下的AD7192均方根噪声。

图2. 噪声输出(VREF = 4.096 V, AVDD = 5 V, Output Data Rate = 4.7 Hz, a Rate = 4.7 Hz,

图3. 噪声直方图(VREF = 4.096 V,AVDD =5 V,输出数据速率 = 4.7Hz,增益 = 1,斩波禁用,SINC4滤波器)

表3. 斩波禁用且采用一个SINC4滤波器时不同输出数据速率和增益设置条件下的AD7192系统均方根分辨率(减去2.7位以获取峰峰值或无噪声码分辨率)

常见变化

可使用其它集成PGA的24位或较低分辨率的Σ-Δ型ADC,例如AD7190、AD7193、AD7797和 AD7799。如果无需对输入信号进行衰减, 则可使用功耗低于AD8475 的 AD8476。

在无需衰减和高输入阻抗的应用中,可将AD7192 直接连接到传感器,以避免模拟前端调理电路引入的噪声。例如,满量程输出电压较小的称重传感器无需衰减,因此可以直接连接到AD7192 差分输入端(参见 CN-0102、 CN-0107、 CN-0108、 CN-0118、 CN-0119和 CN-0155)

电子发烧友App

电子发烧友App

评论