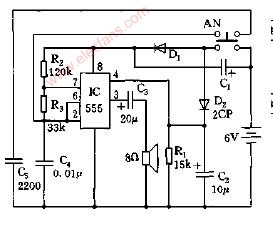

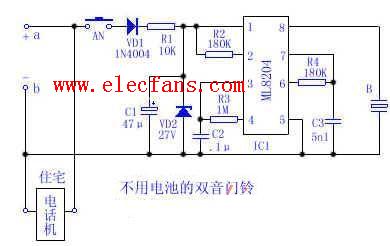

静态微功耗双音门笛电路图

电子发烧友App

电子发烧友App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网>电子技术应用>电子技术>电路图>游戏电路>静态微功耗双音门笛电路图

相关推荐

696

696

19

19 4727

4727

7470

7470

7401

7401

7366

7366

3687

3687

9172

9172

18

18 536

536

1561

1561

评论