数字测试电路

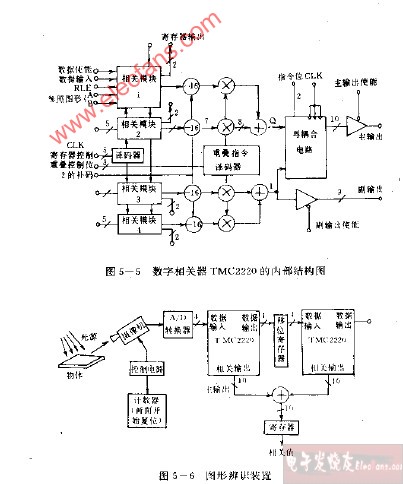

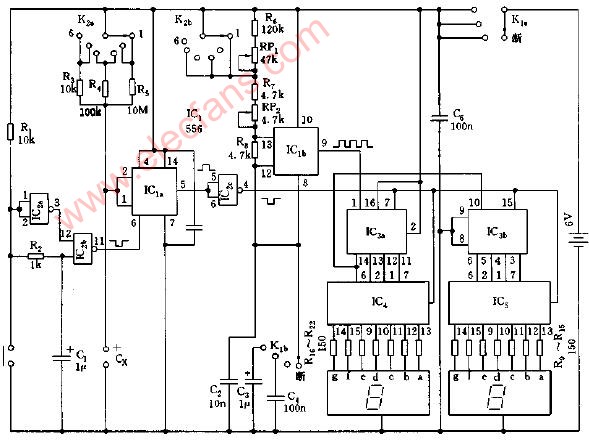

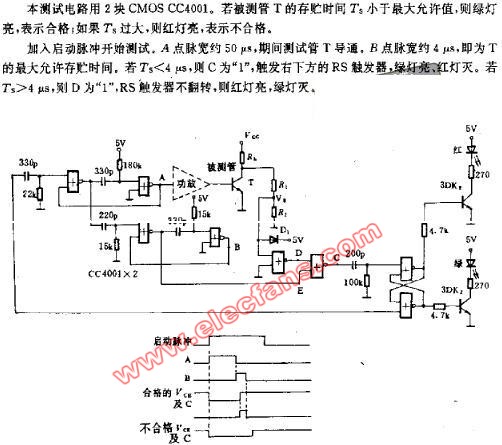

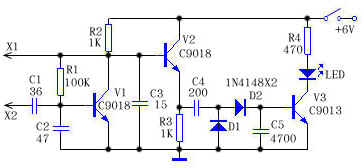

数字测试电路是为了测试动作时间和抖动时间面设计的,由于继电器内部结构同所用逻辑器件不同。因此根据DL(DY)—20C系列继电器的内部结构设计出合理的逻辑电路,配合微机系统内部时钟进行计时,从而测出继电器的动作时间并判断抖动时间是否小于7ms,从而确定继电器的动作可靠性及过电流、过电压能力是否合格。

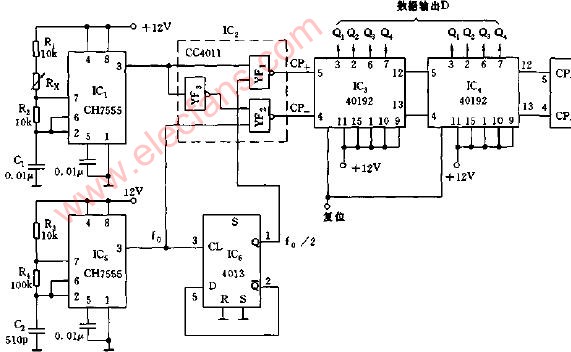

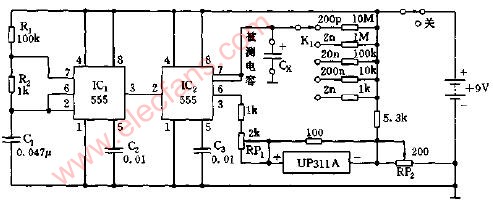

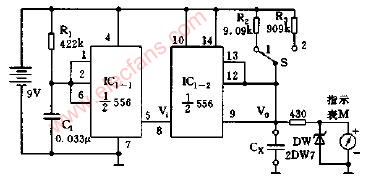

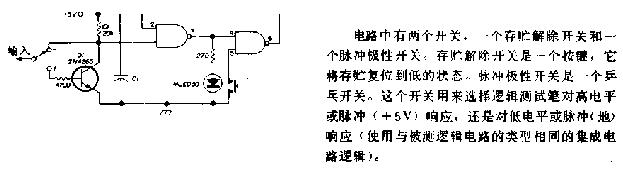

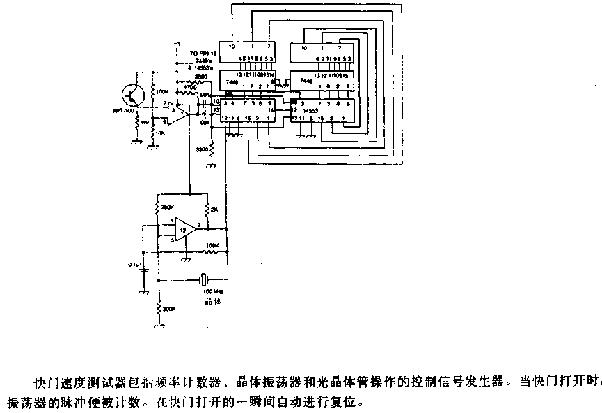

根据继电器的五种不同结构及继电器动作时间的定义分别设计出相应的动作时间测试电路。这五种电路的共同特点是从继电器施加激励量开始,程序设计使CPU读取计算机内部定时器的时间作为起始时间。直到继电器所有动合触点闭合或动断触点断开为止,再次读取内部定时器的时间作为终止时间,终止时间与起始时间之差即为一次动作时间。电磁继电器动合触点和动断触点的不同组合有五种结构方式。所以数字电路设计时应满足不论哪种形式的触点,只要触点动作就应微机的计数器停止计时,并再次读取计算机内部定时器的时间作为终止时间,因此逻辑电路设计时应考虑对不同触点方式应具有统一的逻辑关系,本着这个原则设计出一个常开触点、一个常闭触点、两个常开触点、两个常闭触点、一个常闭和一个常开五种不同的测试电路。

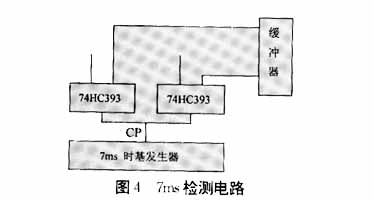

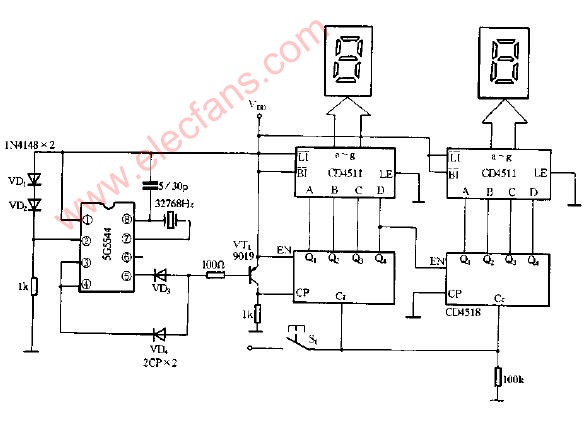

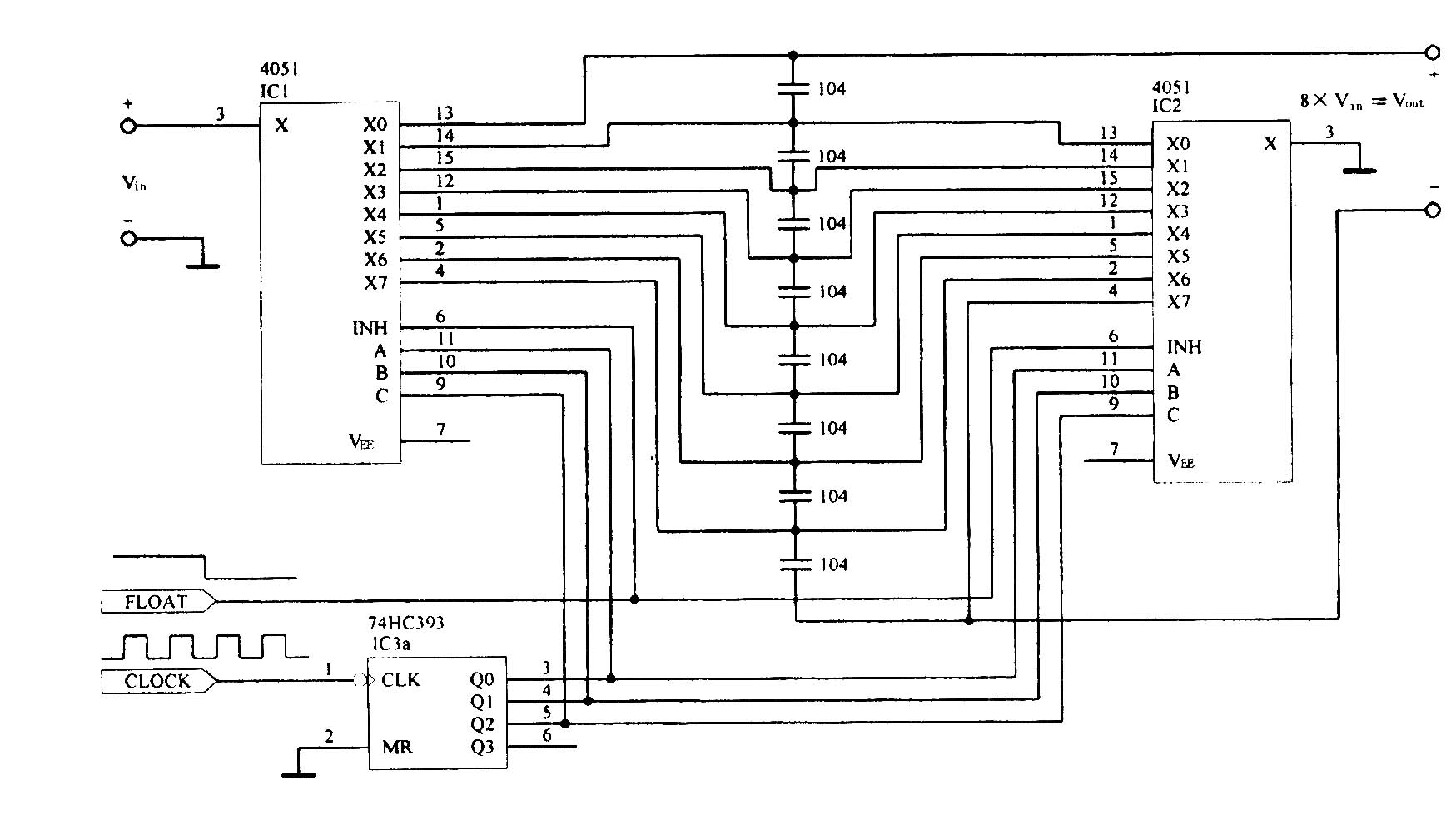

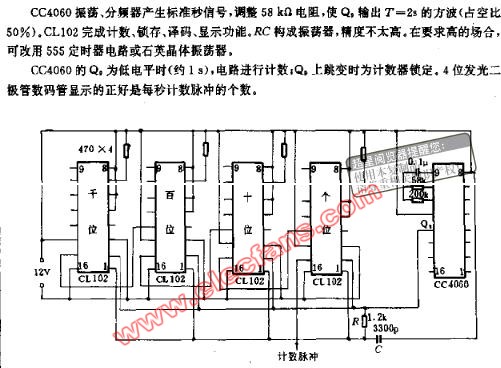

7ms抖动时间检测电路是在动作时间测试电路基础上加上一个74HC393计数器和一个7ms时基发生器及一个缓冲器,即构成了7ms检测电路,它具有各自独立的时钟输入,含有清零端和时钟输入端,当计数器满度时其值为256。此时各位均置“1”,而当只有最高位为“1”,其它位为“0”时,计数器值为128,因此,如果以最高位做为判断位时,如果CPU始终监测393的最高位,一旦最高位为“1”则表明计数器计数值为128,否则不足128,为达到对7ms时间的判断目的,即可以周期为7ms/128的时钟脉冲作为74HC393的时钟转入,因为此时,如果输入脉冲个数一旦等于128个时,计数器的最高位置“1”其余位为“0”, 那么此时计数器所计时间就为T=7ms/128*128=7ms。若输入脉冲少于128个,最高位始终置“0”,那么计数器所计时间T<7ms。因此当128*10.3/7Hz的时钟脉冲做为393的时钟脉冲时,以最高位置“1”否,即可判断计数器计数时间是否大于7ms。据此,当继电器动合触点闭合后,或动断触点断开后,此时因为反相三态门,正向三态门输出都为“1”。此计数器的R端为“1”,使计数器清零并开始计数,当继电器触点有抖动时,闭合触点断开,此时计数器R端为“0”,停止计数。如果抖动时间小于7ms,其计数器计数不足128,最高位始终为零,当抖动大于7ms时,计数器计数大于128,最高位输出“1”。此间CPU通过接口电路对其最高位不断地执行读操作,只要有“1”读出,就说明触点的抖动时间大于7ms,该继电器的过电流(电压)能力或动作可靠性为不合格,否则为合格。

电子发烧友App

电子发烧友App

评论