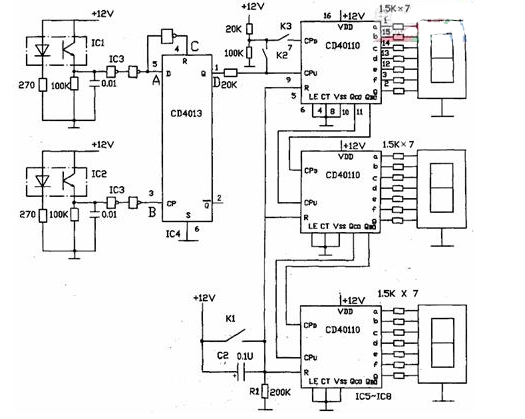

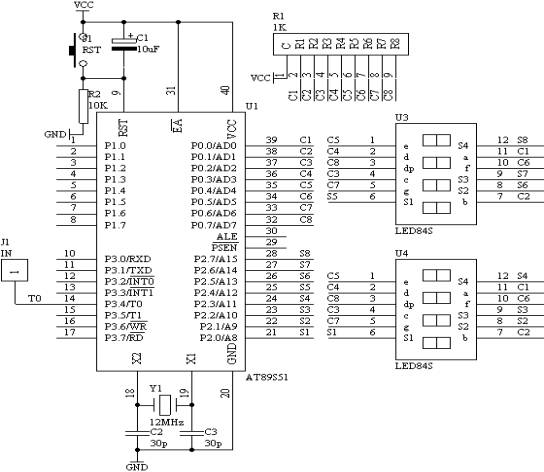

SJ-2微型6位通用累加计数器的总电路图

SJ-2微型6位通用累加计数器的总电路图

- 电路图(495405)

相关推荐

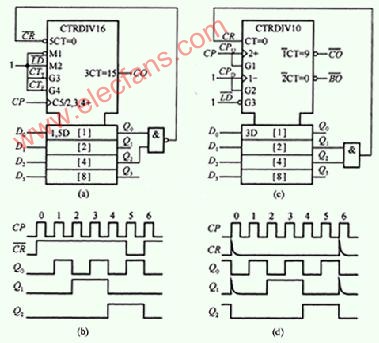

计数器及时序电路原理及实验

计数器。4、用74390两个宏连接成八位十进制异步计数器。5、用74161用清零和置数法组成六进制和十二进制计数器。6、分别用D触发器和同步计数器加译码电路的方法构成7进制电路实现如下编码:[0→2→5

2009-10-10 11:47:02

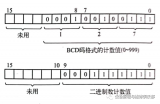

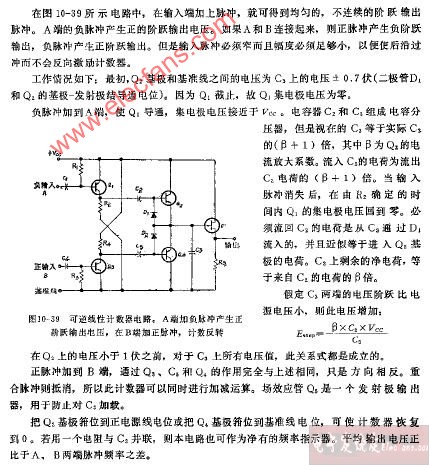

SIMATIC S7-1500 PLC SIMATIC计数器-加计数器

加计数器(S_CU)在计数初始值预置输入端S上有上升沿时,PV装入预置值,输入端CU每检测到一次上升沿,当前计数值CV加1(前提是CV 小于999);当前计数值大于0时,Q输出为高电平“1”;当R端子的状态为“1”时,计数器复位,当前计数值CV为“0”,输出也为“0”。加计数器指令和参数见图2

2023-04-27 15:38:22 741

741

741

741

SIMATIC S7-1500 PLC SIMATIC加计数器

计数器的功能是完成计数功能,可以实现加法计数和减法计数,计数范围是0~999.计数器有三种类型:加计数器(S_CU)、减计数器(S_CD)和加减计数器(S_CUD)。

2023-04-27 15:38:07 439

439

439

439

FX2N系列PLC的32位加减双向计数器

FX2N系列PLC的32位加减双向计数器(设定值-2147483648~2147483647)

Ø 通用加/减双向计数器:C200~C219(20点);

Ø 停电保持加/减双向计数器:C220~C234(15点);

2023-01-29 15:20:22 1124

1124

1124

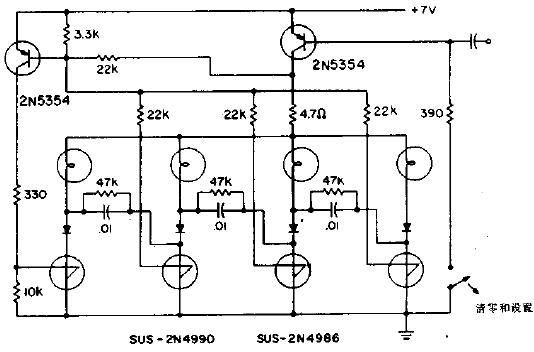

1124西门子S7-300PLC高速计数器的计数方式简介

单路脉冲输入的内部方向控制加/减计数。即只有一个脉冲输入端,通过高速计数器的控制字节的第3位来控制作加计数或者减计数。该位=1,加计数;该位=0,减计数。如图1所示内部方向控制的单路加/减计数 。

2023-01-04 10:20:46 2863

2863

2863

2863SCL语言之加计数-计数器函数S_CU

可使用“分配参数并加计数”指令递增计数器值。当 CU 参数的信号状态从“0”变为“1”(信号上升沿)时,当前计数器值递增 1。通过参数 CV 提供当前计数器值。计数器值达到上限 999 后,停止增加。如果达到限值,即使出现信号上升沿,计数器值也不再递增。

2023-01-03 11:02:18 617

617

617

617使用分配参数并加计数指令递增计数器值

可使用“分配参数并加计数”指令递增计数器值。当 CU 参数的信号状态从“0”变为“1”(信号上升沿)时,当前计数器值递增 1。通过参数 CV 提供当前计数器值。计数器值达到上限 999 后,停止增加。如果达到限值,即使出现信号上升沿,计数器值也不再递增。

2022-08-03 11:08:22 868

868

868

868

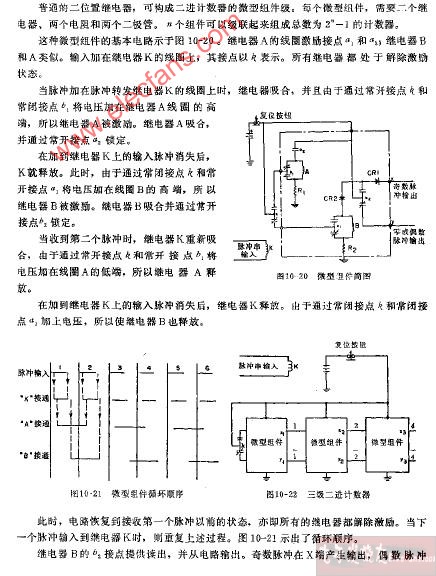

计数器及时序电路

1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制

2022-07-10 14:37:37 15

15

15

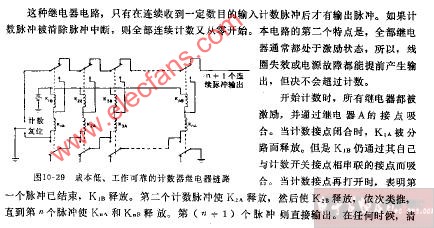

15C51定时器计数器

目录C51定时器计数器电路图定时/计数器的结构和工作原理相关寄存器C51定时器计数器电路图定时/计数器的结构和工作原理定时/计数器的实质是加1计数器(16位),由高8位和低8位两个寄存器TH1

2021-11-29 12:21:03 14

14

14

14SCL语言之加计数-计数器函数S_CU

当参数 S 的信号状态从“0”变为“1”时,计数器值将置位为参数 PV 的值。如果置位计数器且输入 CU 处的逻辑运算结果 (RLO) 为“1”,即使没有检测到信号边沿变化,计数器也会在下一周期计数一次。

2020-09-04 17:09:39 3277

3277

3277

3277

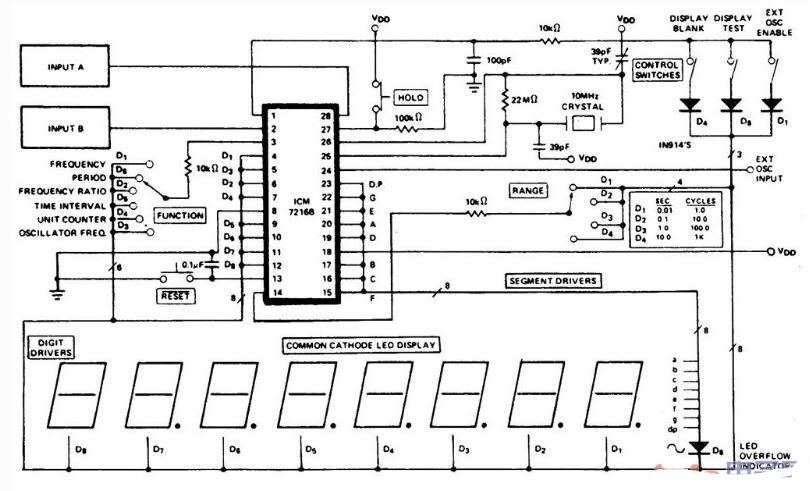

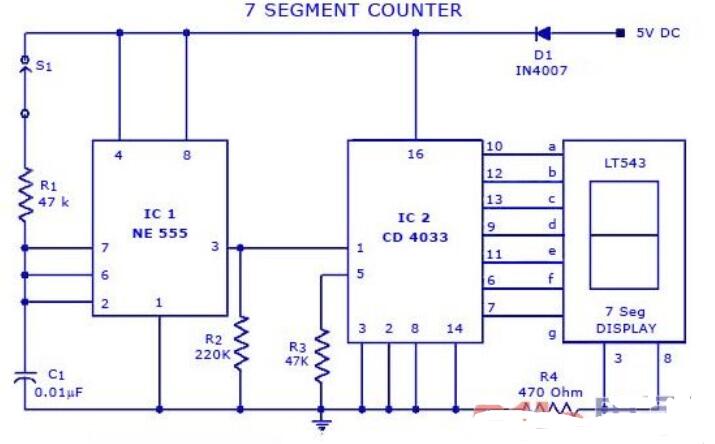

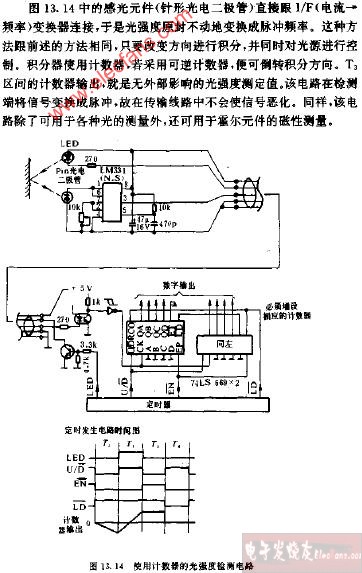

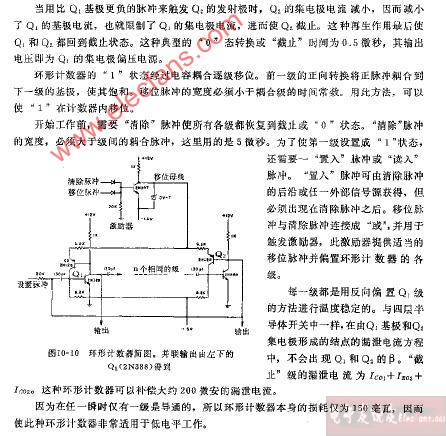

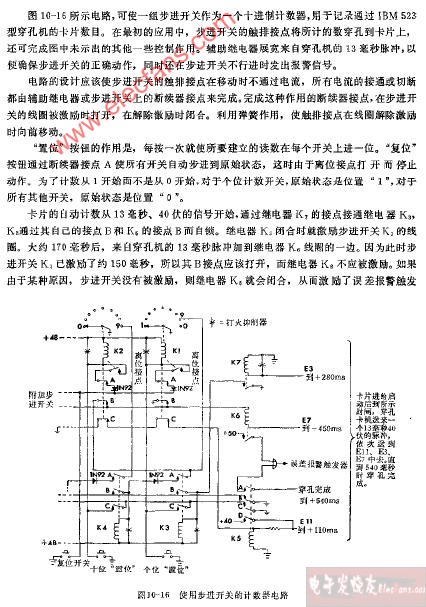

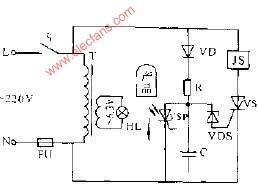

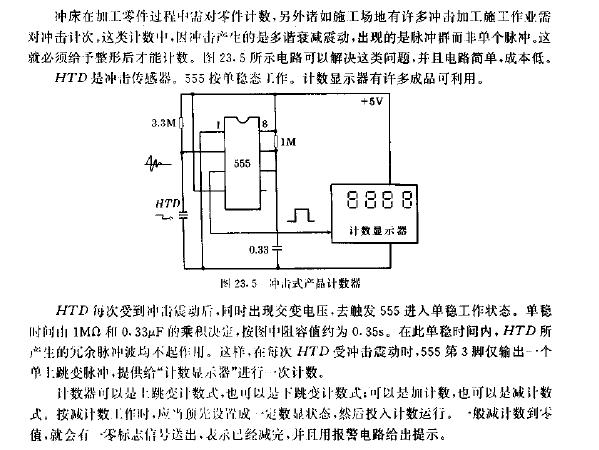

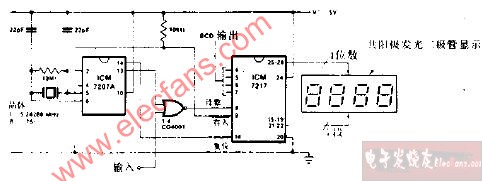

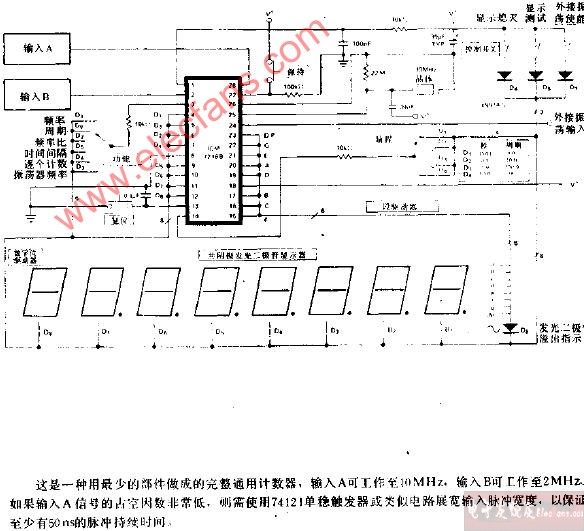

简易的通用计数器电路图

ICM7216A或者ICM7216B可用作一个最少元件的完整的通用计数器。该电路的A输入频率可达10MHz,B输入的可达2MHz。如果A输入的信号占空比很低,则需要使用一个74121单稳多谐振荡器或者相似的电路来扩展输入脉宽,保证最少有50ns的连续脉宽。

2020-01-24 14:55:00 10865

10865

10865

10865

74ls190应用电路图大全(五款74ls190不同进制计数器电路)

本文主要介绍了五款74ls190应用电路图。包括了60和100进制计数器(递增)电路,56进制递减计数器与100进制递减计数器电路和2位十进制可加减计数器电路。

2018-05-28 16:18:11 54071

54071

54071

54071

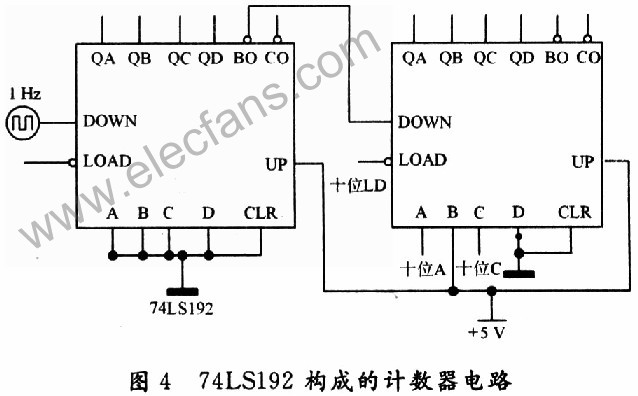

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)

本文主要介绍了五款74ls192计数器应用电路图。其中包括了74ls192电子骰子电路、74ls192计时电路、74ls192定时电路、74ls19230进制计数器电路及两位十进制计数器。

2018-05-28 10:20:01 116393

116393

116393

116393

74ls161分频电路图大全(脉冲分频电路\同步加法计数器)

本文主要介绍了74ls161分频电路图大全(脉冲分频电路\同步加法计数器)。计数器又称为分频器。N进制计数器的进位输出脉冲就是计数器输入脉冲的N分频。N进制计数器可直接作为N分频器。用同步加法计数器

2018-05-08 14:41:38 95799

95799

95799

95799

74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)

本文主要介绍了74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)。74LS163是(模16)四位二进制同步计数器。该计数器能同步并行预置数据,同步清零,具有清零、置数、计数和保持四种

2018-05-08 14:27:23 51924

51924

51924

51924

同步计数器74ls162设计24进制计数器

本文首先介绍了计数器种类与应用,其次介绍了74LS160并行置零法设计24进制计数器电路图,最后介绍了74ls162设计24进制计数器原理电路图。

2018-05-08 11:46:43 54648

54648

54648

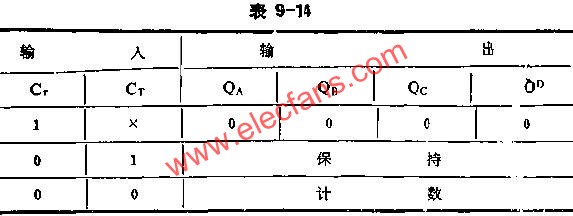

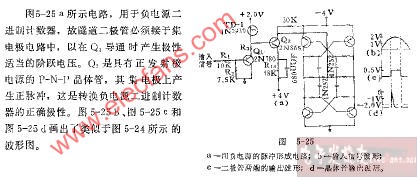

54648CD40110组成的一位数码计数器

本文主要介绍了CD40110组成的一位数码计数器。CD40110为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码输出等功能。CD40110有2个计数时钟输入端

2018-03-04 11:17:34 18394

18394

18394

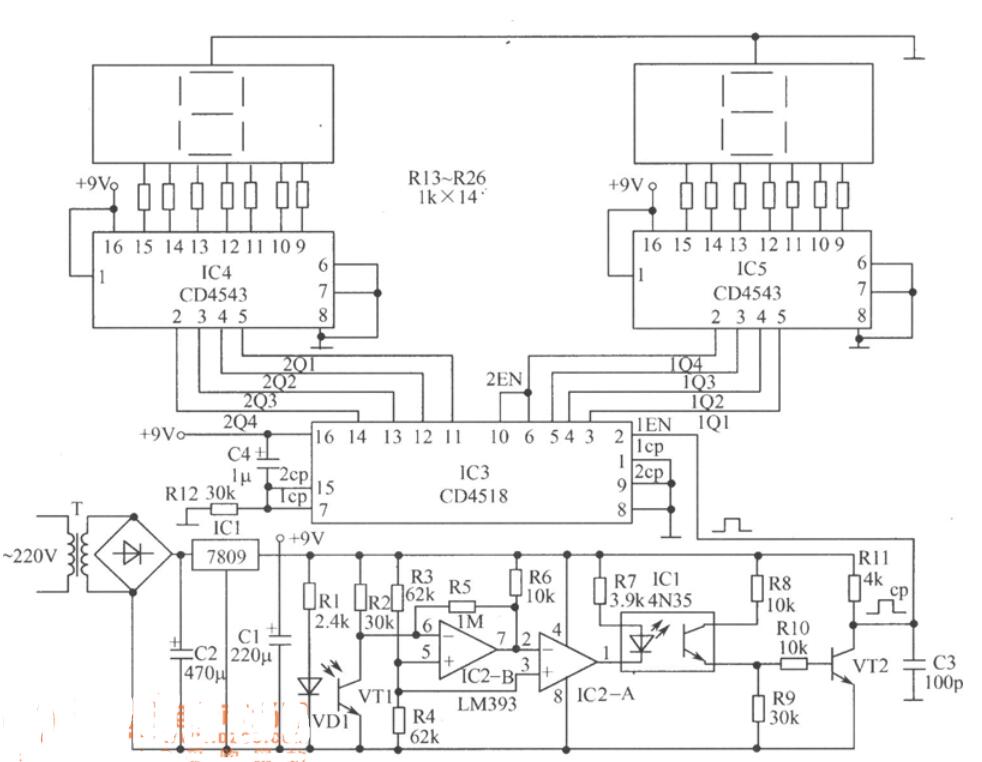

18394cd40110计数器电路图大全(七款cd40110计数器电路设计原理图详解)

本文主要介绍了cd40110计数器电路图大全(七款cd40110计数器电路设计原理图详解)。利用交流电源50Hz的输出频率通过分频,可以取得各种不同频率的时基脉冲。该电路选用lmin的时间长度作为

2018-03-04 11:09:50 31876

31876

31876

31876

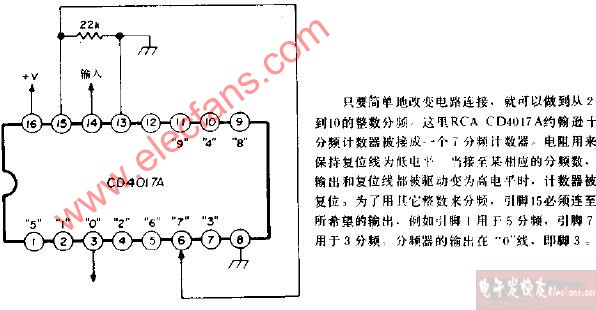

cd4017计数器电路图(三款cd4017计数器电路)

本文开始对CD4017功能与CD4017逻辑结构图进行了介绍,其次分别介绍了用CD4017和选择开关组成多进制计数器、CD4017组成的1/n计数器电路与用CD4017组成1~17进制计数器电路图。

2018-01-31 13:58:06 22819

22819

22819

22819

74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)

本文主要介绍了74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)。74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端

2018-01-18 10:56:39 324594

324594

324594

324594

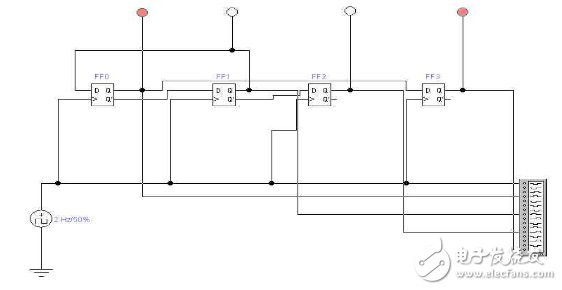

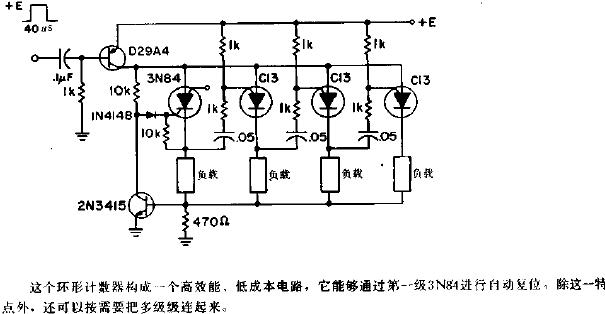

环形计数器介绍_4位环形计数器波形图

环形计数器是由移位寄存器加上一定的反馈电路构成的,用移位寄存器构成环形计数器的一般框图,它是由一个移位寄存器和一个组合反馈逻辑电路闭环构成,反馈电路的输出接向移位寄存器的串行输入端,反馈电路的输入端根据移位寄存器计数器类型的不同,可接向移位寄存器的串行输出端或某些触发器的输出端。

2018-01-16 14:54:44 40935

40935

40935

40935

T213 2-N-16可变进制计数器的应用电路图

T213计数器内部由四级J-K触发器串接成四位异步计数器,它的管脚外引线排列及功用如图所示,将T213计数器的

2010-10-19 13:40:10 1557

1557

1557

1557

74LSl92构成的计数器电路图

74LSl92构成的计数器电路图如图4所示:左边的1片74LSl92芯片为计数器的个位,右边的1片74LSl92芯片为计数器的十位,个位和十位计数器的四个输出端都接上数码管显示。其中作为个位

2010-08-23 09:35:03 2206

2206

2206

2206

1602液晶的6位计数器程序

;******************************;1602液晶6位计数器:本程序调试通过 *;************************************;* 硬件:此程序

2010-04-21 22:44:19 54

54

54

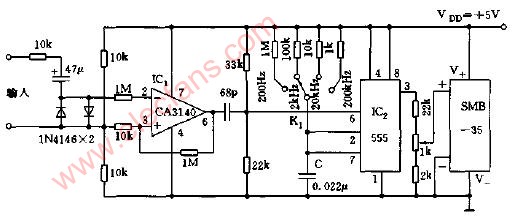

546位数显频率计数器

6位数显频率计数器

1.实验任务

利用AT89S51单片机的T0、T1的定时计数器功能,来完成对输入的信号进行频率计数,计数的频率结果通过8位动态数码管显示出来。

2010-02-02 10:57:39 1580

1580

1580

1580

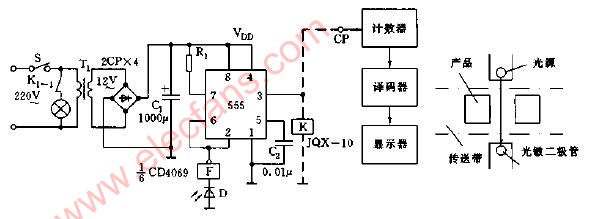

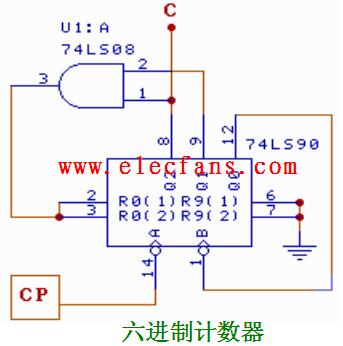

利用复位端构成的模6计数器电路

利用复位端构成的模6计数器电路

利用集成计数器的预置端和复位端可以构成任意模计数器。下图所示依次是利用74163和74192构成的

2010-01-12 13:54:31 4276

4276

4276

4276

电子发烧友App

电子发烧友App

评论