电子发烧友网站提供《数字钟加装中文语言整点报时电路及闹功能的开发利用.pdf》资料免费下载

2023-10-18 10:55:52 0

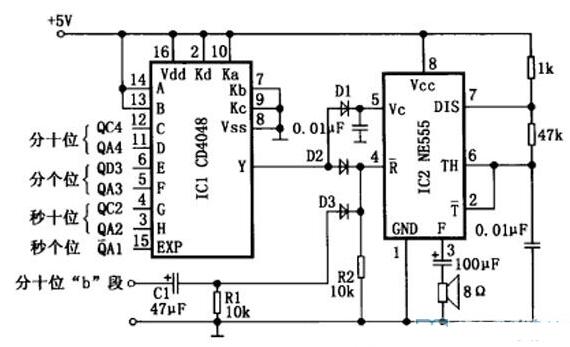

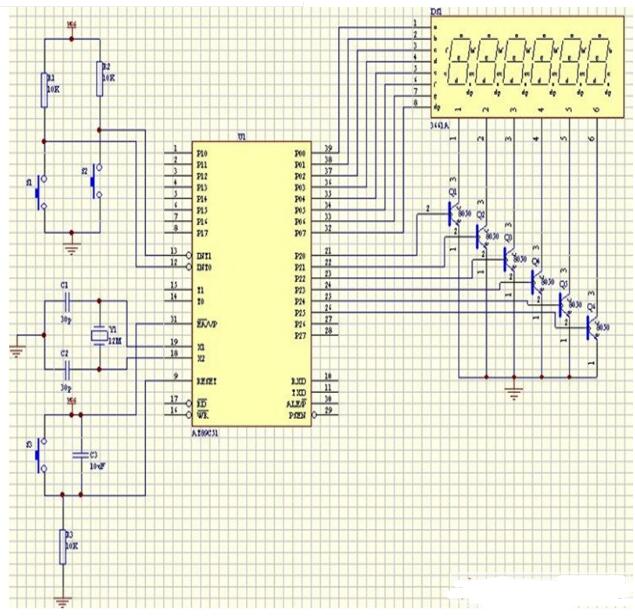

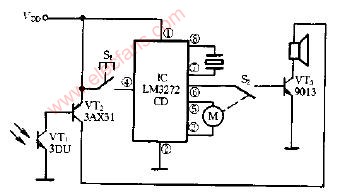

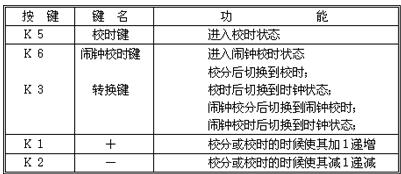

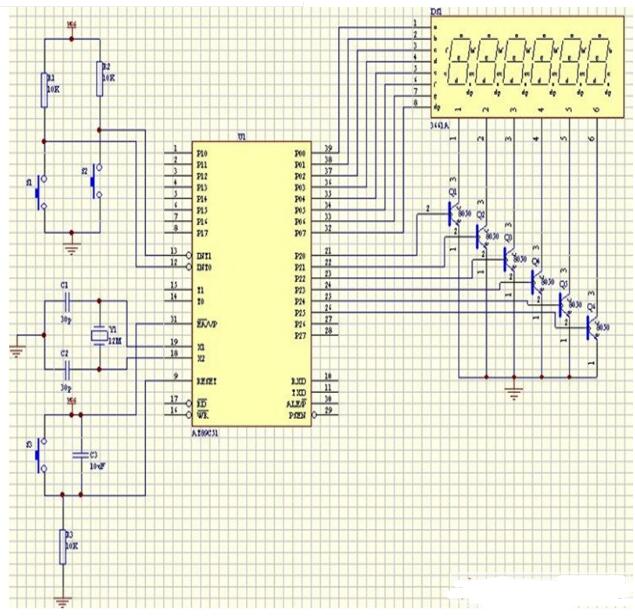

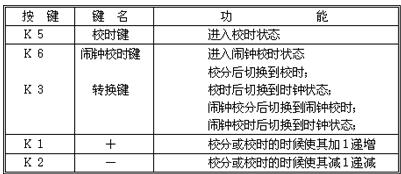

0 实现整点报时功能;使用P3端口的P3.0实现闹钟功能。其硬件原理图如图一所示。 图一 电脑数字钟硬件原理图图中按键K1,K2,K3及开关K5,K6的定义如下表所示

2009-03-14 17:03:35

基于VHDL语言中数字钟的整点报时源代码下载

2021-12-15 14:52:56 2

2 题目:创意数字钟基本要求:创意性设计;温度显示;日历显示;设置信息带记忆功能。/*题目:创意数字钟基本要求:创意性设计;温度显示;日历显示;设置信息带记忆功能。创意:闹钟 整点报时记忆:设置的闹钟会被记忆下来*/...

2021-11-16 13:21:01 13

13 简易数字钟设计一、摘要信息时代,时间观念深入人心,所以掌握数字钟的设计具有一定的时代意义,并且使用Multisim进行分立元件设计数字钟,可以大大提升个人数字电路的素养。设计思路是从上至下,先进行数字钟

2021-11-06 19:06:01 45

45 利用定时器实现数字钟设计选用芯片:AT89S52功能:能校时和校分,具有整点报时功能(四低一高)。我在设计的时候,想设计出那种四低一高的整点报时,刚开始想的时候确实费了点脑子,在网上搜也没相关的代码

2021-11-04 11:51:00 15

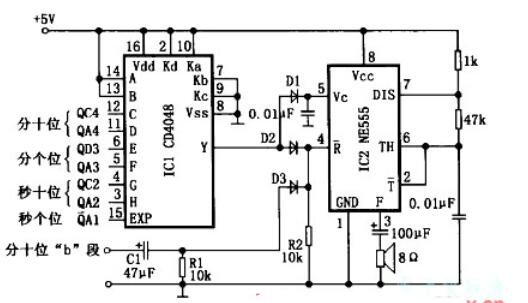

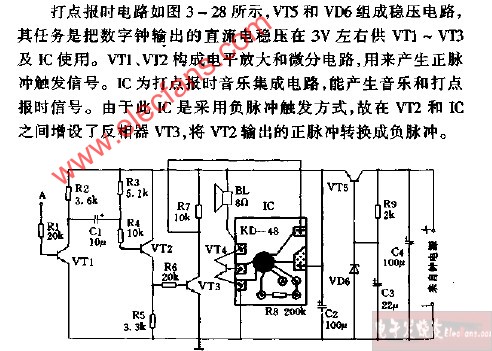

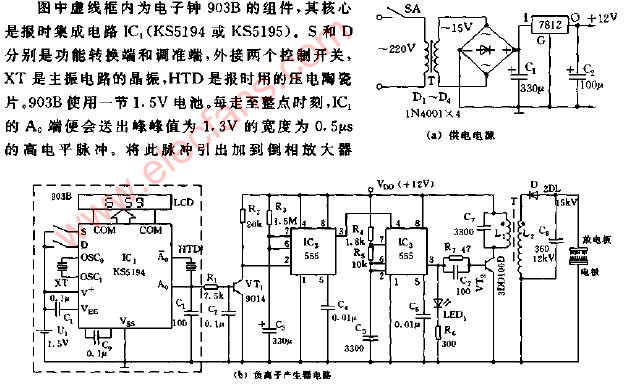

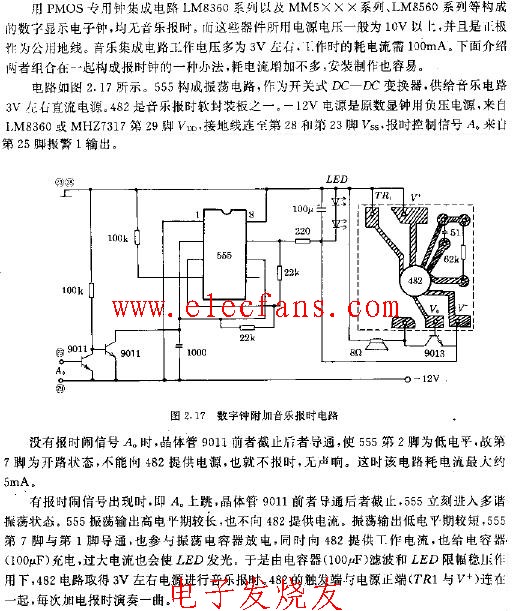

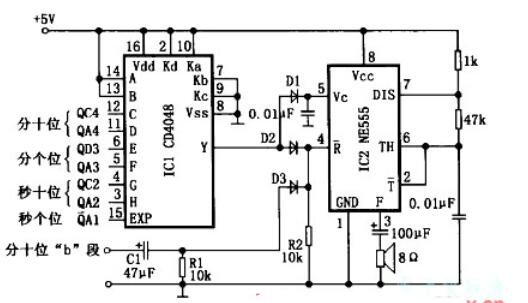

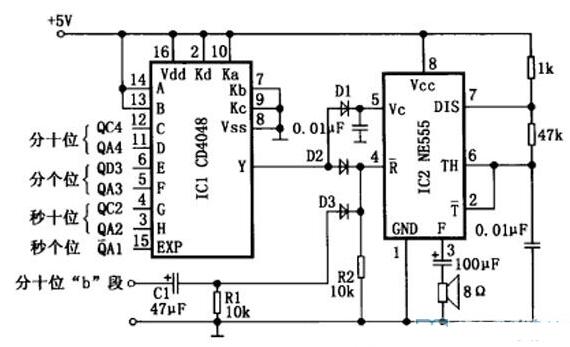

15 该电路每当数字钟走到“59分50秒”时开始报时,在秒个位显示“0、2、4、6、8”的时间鸣叫“嘟”,其叫五声,在显示“00分00秒”时鸣叫一声“嘀”。

2021-05-01 16:37:00 2365

2365

本文档的主要内容详细介绍的是数字钟的Protel工程电路原理图及PCB文件免费下载。

2021-02-01 11:08:41 55

55 本文档的主要内容详细介绍的是数字钟的PCB原理图免费下载。

2020-11-17 17:12:11 186

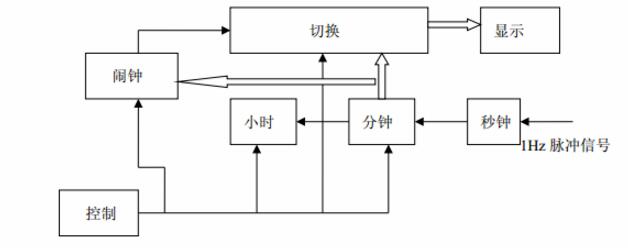

186 多功能数字钟是采用数字电路实现用数字显示时间的计时装置。主要由振荡器、分频器、计时器、译码显示及扩展电路几部分构成。具有时间显示、校时校分及闹钟设置、整点报时等扩展功能并且具有走时准确、显示直观、稳定等优点深受人们喜爱。

2020-11-05 17:35:14 23

23 本文档的主要内容详细介绍的是红外遥控数字钟的PCB原理图免费下载。

2020-09-24 17:49:24 8

8 这款电路如下图所示,该电路每当数字钟走到“59分50秒”时开始报时,在秒个位显示“0、2、4、6、8”的时间鸣叫“嘟”,其叫五声,在显示“00分00秒”时鸣叫一声“嘀”。

2020-03-23 16:36:07 4166

4166

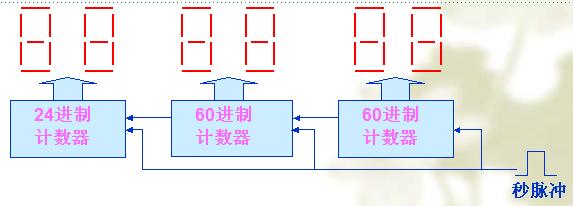

数字钟实际上是一个对标准频率进行计数的计数电路。它的计时周期是24小时,由于计数器的起始时间不可能与标准时间(如北京时间)一致所以采用校准功能和报时功能。

2019-08-29 08:00:00 29

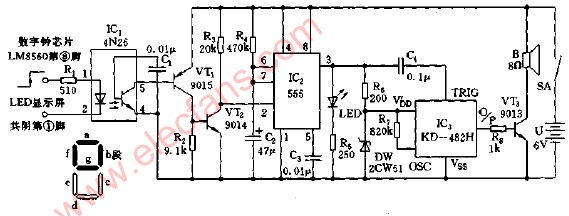

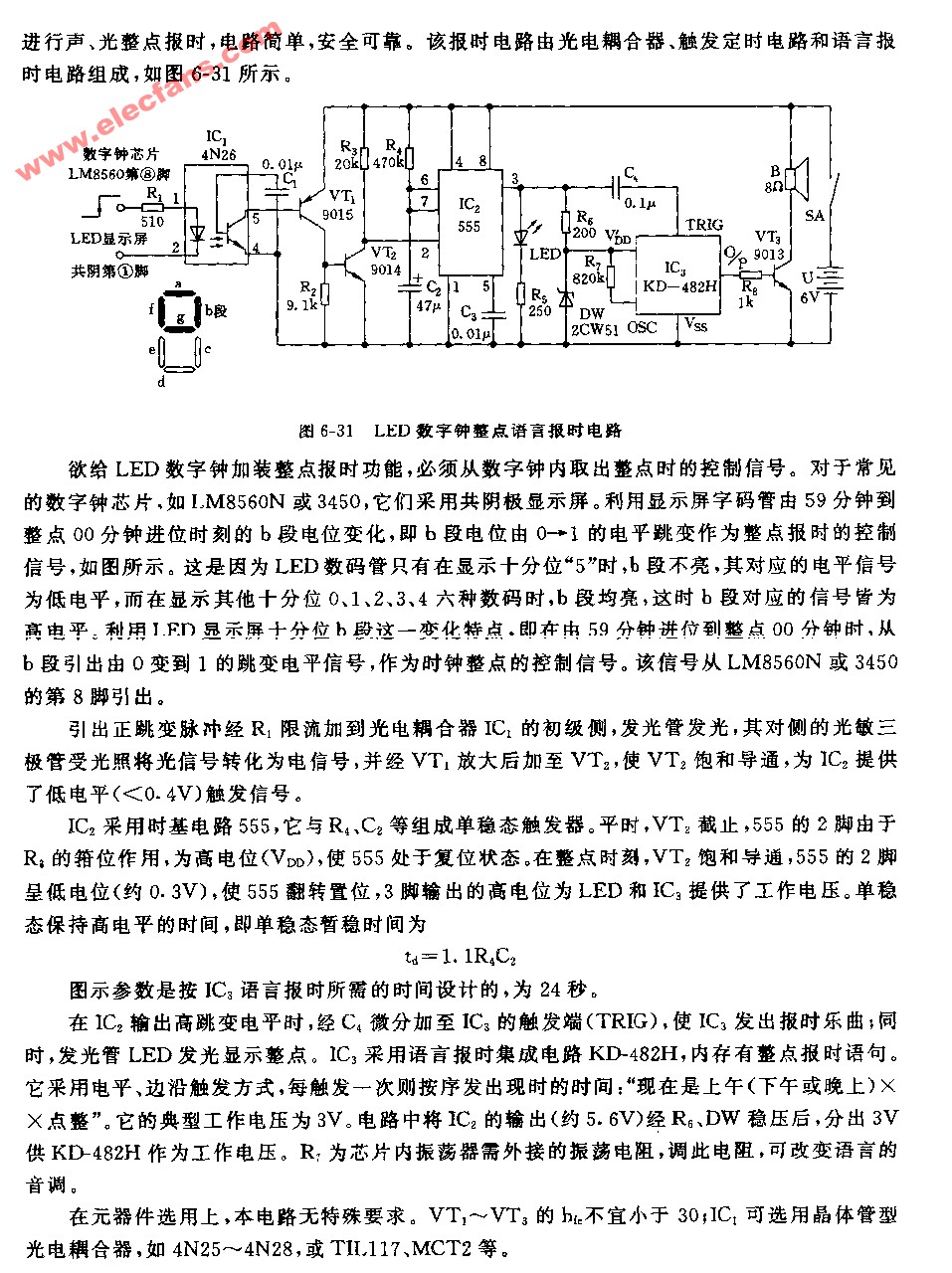

29 关键词:LED , 数字钟 , 语言报时 一般动态LED数字钟都无报时功能,这里只要增加一个简单的电路就能使它实现整点报时功能。所采用的集成电路本身具有程控静音功能,从晚上11点到凌晨5点不报时

2018-11-09 11:15:02 654

654 本文档的主要内容详细介绍的是数字钟的实验包括了电路原理图,硬件连线,程序等详细资料概述

2018-06-19 08:00:00 38

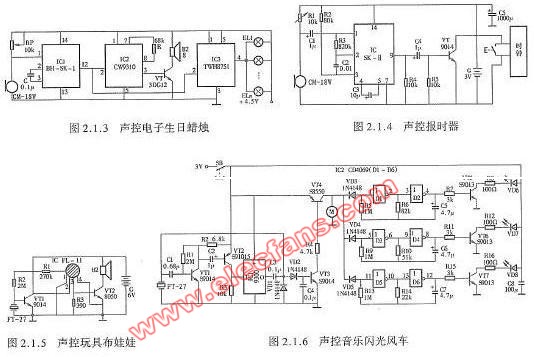

38 本文主要介绍了七款数字时钟设计电路图。数字钟是一种用数字电路技术实现时、分、秒计时的钟表。与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。

2018-01-26 11:14:30 155285

155285

本文详细介绍了五款数字钟仿真电路图。数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。

2018-01-26 10:44:56 96265

96265

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定,通常使用石英晶体振荡器电路构成数字钟。

2018-01-15 15:37:09 9768

9768

。 2、具有驱动8位8段共阴极扫描数码管的片选驱动信号输出和8段字形译码输出。编码和扫描可参考实验四。 3、扬声器在整点时有报时驱动信号产生(响声持续多长时间?)。 4、LED灯按个人口味在整点时有花样显示信号产生。 实验内容及步骤 1、根据电路特点,可在

2017-12-05 09:33:46 15

15 文中简要介绍了一种基于FPCJA的多功能数字钟设计方案。在实现数字钟计时、校时和整点报时等基本功能的基础上增加世界时钟功能,能够将北京时间快速转换为格林威治标准时。该方案采用VHDL和原理图相结合

2017-11-30 14:57:28 131

131 为使数字钟从电路设计、性能分析到设计出PCB版f即印制电路版)图的整个过程能够在计算机上自动处理完成,从而缩短设计周期、提高设计效率、减小设计风险。本系统基于EDA技术的设计方法,提出一种采用

2017-11-29 11:06:51 48

48 数字钟的所有计时都要由软件控制实现。用软件对几个按键所得信号进行相应改变,以控制时钟与闹钟的显示。通过软件对闹钟与时钟进行比较,当时钟所显示时间与闹钟一样时,要启动报时模块。 在众多的语音芯片

2017-11-29 10:35:18 58

58 快捷、便利的生活。 本文采用 AT89C51 单片机为核心构成的语音报时功能的数字钟。该系统操作简单,方便,可随时调节时间,制定时间报时。系统采用语音芯片 ISD1110和米头组成了语音录放模块;采用时钟芯片 DS1302 和 32768HZ 晶振组成了时钟模

2017-11-28 14:41:42 30

30 ,且有一个置零功能,可以组成六十进制和二十四进制的计数器。 整点报时模块电路用的是555芯片和一块CD4068芯片组成的电路,555芯片可以接成多谐振荡器,提供交变信号使蜂鸣器发出声音,而整点报时的控制可以用CD4068实现,CD4068是8输入与/与非门, 可

2017-11-28 14:24:37 37

37 该实验是利用QuartusII软件设计一个数字钟,进行试验设计和仿真调试,实现了计时,校时,校分,清零,保持和整点报时等多种基本功能,并下载到SmartSOPC实验系统中进行调试和验证。此外还添加

2017-11-28 14:18:55 30

30 数字时钟是以数字电路技术为基础来实现时、分、秒的计时装置,通常以十进制计数器和七段译码器两组芯片完成数字钟计数功能。由于功能贴近实际且实现容易,成为数字电路技术实践教学中常用实验电路之一。然而,随着

2017-11-17 12:41:02 7634

7634

在电子技术实验教学中,构建学生的电路设计理念,提高学生的电路设计能力,是教学的根本目的和核心内容。数字钟电路的设计和仿真,涉及模拟电子技术、数字电子技术等多方面知识,能够体现实验者的理论

2017-10-19 15:05:55 8

8 本次课程设计的题目是设计一个数字钟,要求具有以下功能:显示时、分、秒(如23:52:45);可实现手动或自动的对时、分进行校正;计时过程具有报时功能,当时间到达整点前10秒进行报时。本报告就是对这次

2016-10-12 17:42:49 105

105 24小时整点和半点语音报时,完整报时语音

2016-05-17 09:49:51 0

0 本方案设计的多功能数字钟采用单片机作为控制芯片,用按键输入设置,通过12864液晶屏进行输出显示,除了传统的年月日时分秒显示时间功能 之外还具有测量温度,自动背光照明,阴历节气显示,整点报时等功能,具有外观精美、走时准确的特点,同时电路和程序设计充分体现电子装置的智能化 优势。

2016-03-28 14:34:35 23

23 单片机课程设计数字钟原理图 仿真文件 实验报告

2016-01-08 11:58:18 37

37 基于multisim的 多功能数字钟电路设计

2015-11-23 11:33:05 457

457 本文以FPGA平台为基础,在QuartusⅡ开发环境下设计开发多功能数字钟。数字钟实现计时\校时\整点报时\世界时钟功能.

2012-12-18 11:51:03 32123

32123 2012-12-15 17:17:39 198

198 本设计是以 STC89C51 单片机为核心器件,应用 ISD1420,74HC573 等器件,实现命题要求。经过测试,该数字钟达到所有命题 所要求的技术指标。在此基础之上,本设计添加了语音模块,使设

2012-10-29 17:49:44 365

365 数字钟与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。数字钟的设计方法有许多种,例如可用中小规模集成电路组成电子钟.

2011-12-21 09:25:52 826

826 数字钟整点报时电路

2011-05-05 17:46:32 13214

13214

数字钟打点报时电路图

2009-07-29 08:30:20 1238

1238

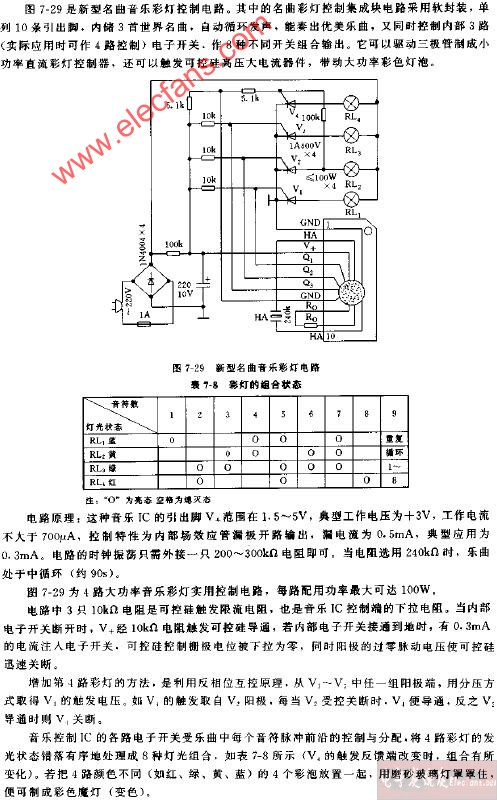

新型名曲音乐彩灯电路图

2009-06-16 15:28:40 705

705

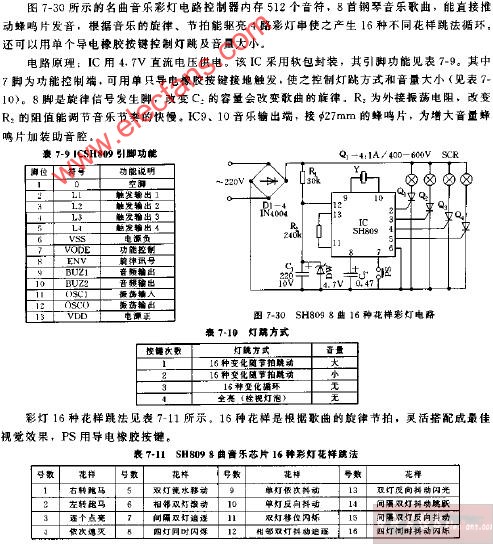

SH809名曲16种花样彩灯电路图

2009-06-16 15:12:43 1086

1086

电子钟整点定时负离子产生器电路图

2009-05-30 13:48:39 1830

1830

报时音响电路图

2009-05-23 13:23:32 379

379

LED数字钟整点语言报时电路图

2009-05-19 13:01:27 4292

4292

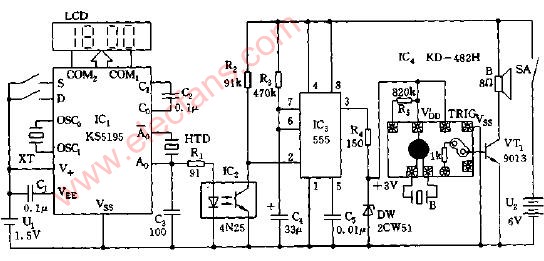

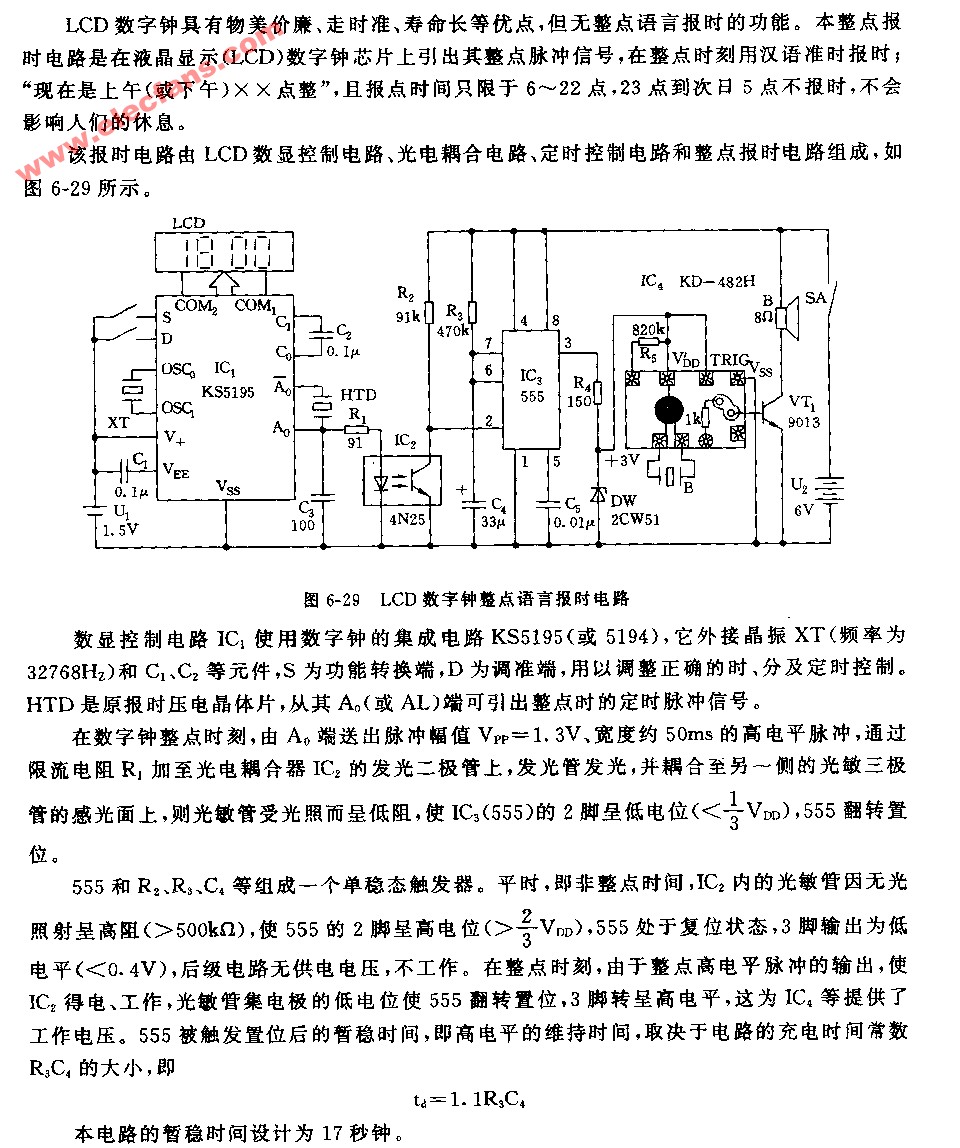

LCD数字钟整点语言报时电路图

2009-05-19 13:01:02 2836

2836

用LED数字钟做定时开关电路图

2009-05-18 11:36:17 23

23 可编程数字钟电路图

2009-05-18 11:31:01 4

4 新颖的集成电路数字钟电路图

2009-05-18 11:29:48 23

23 给石英钟增加音乐报时功能2电路图

2009-05-18 11:28:31 3

3 给石英钟增加音乐报时功能电路图

2009-05-18 11:26:22 13

13

石英钟光控报时电路图

2009-05-08 15:38:30 2251

2251

多功能数字钟的设计与实现一、实验目的 1.掌握数字钟的设计原理。 2.用微机实验平台实现数字钟。 3.分析比较微机实现的数字钟和其他方法实现的数

2009-05-03 11:38:43 470

470

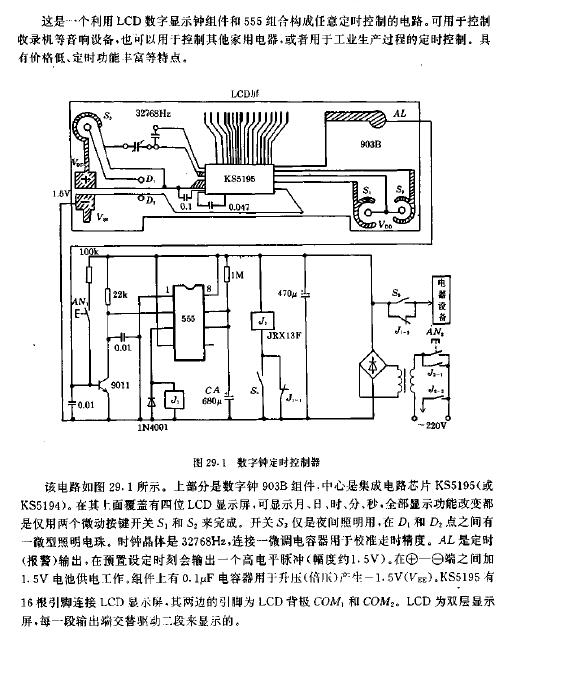

数字钟定时控制器电路图

2009-04-13 09:27:59 1254

1254

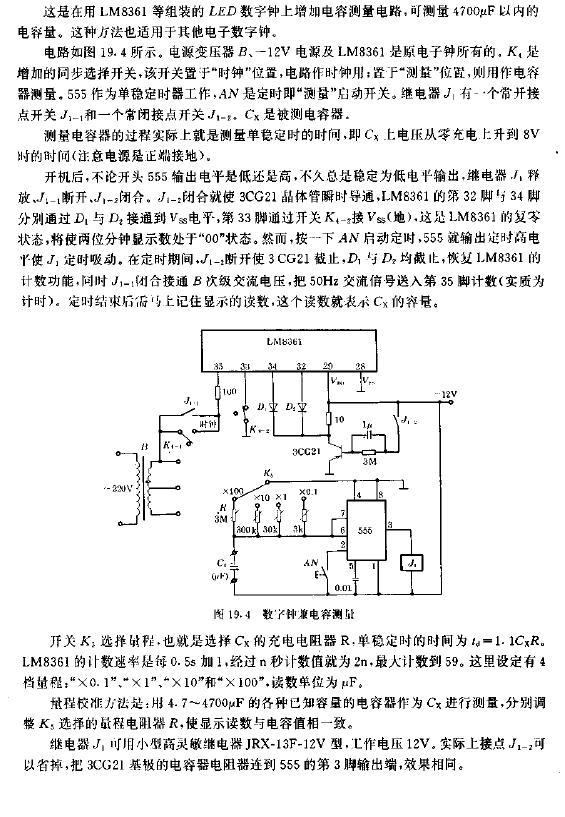

数字钟兼电容测量电路图

2009-04-11 13:54:20 889

889

电脑数字钟硬件原理图

为了节约制作硬件的开支,我们利用单片机开发机上的硬件资源,开发了电脑数字钟的软件。该数字钟由8031单片机控制,采用24小时制计时

2009-03-14 15:25:19 1973

1973

声控报时器电路图

2008-11-06 12:24:57 578

578

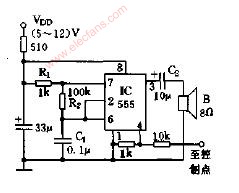

555动态显示LED整点语言报时电路

2008-10-27 09:47:38 762

762

LCD数字钟整点语音报时电路图 : 由时基芯片NE555组成.

2008-10-27 09:34:35 1541

1541

多功能数字钟, 自从它发明的那天起,就成为人类的朋友,但随着时间的推移,人们对它的功能又提出了

2008-07-19 19:10:44 577

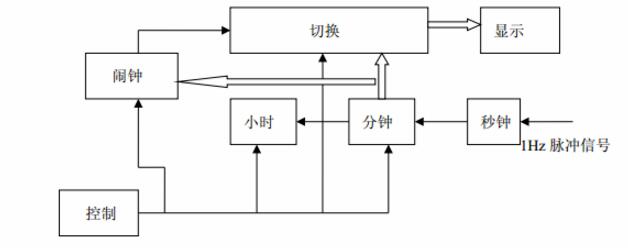

577 数字钟原理框图

数字钟系统构成1、数字钟的构成

2008-07-05 12:10:09 8688

8688

555数字钟附加音乐报时电路

2008-05-20 22:02:30 1418

1418

单片机数字钟电路图

2008-01-12 22:05:57 43

43 单片机数字钟电路图

2008-01-12 22:05:55 5

5 简易led数字钟电路图

2008-01-08 11:16:08 5370

5370 简易数字钟电路图

2008-01-08 11:14:18 3934

3934

最简单数字钟电路图

2008-01-08 11:11:56 178

178 最简单数字钟电路图

2008-01-08 11:11:56 103

103 数字钟电路图下载

2008-01-08 11:08:47 8

8

电子发烧友App

电子发烧友App

硬声App

硬声App

13

13 45

45 15

15 2365

2365

23

23 4166

4166

29

29 654

654 155285

155285

96265

96265

9768

9768

15

15 131

131 48

48 58

58 30

30 37

37 30

30 7634

7634

8

8 105

105 23

23 32123

32123 198

198 365

365 826

826 470

470 1973

1973

评论