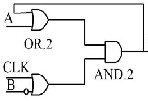

如何用jk触发器组成单脉冲发生器 单脉冲发生器是一种仅产生一个脉冲的电路,其在数字系统中得到广泛应用,例如计数器中的清零信号,脉冲电路中的触发信号等。在电路设计中,JK触发器是一种常见的抗干扰性强

2023-08-24 15:50:11 317

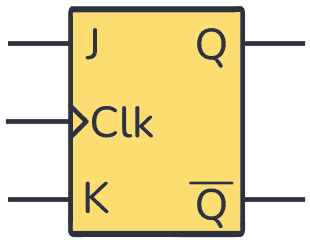

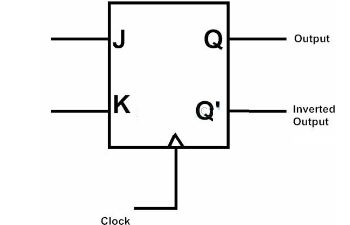

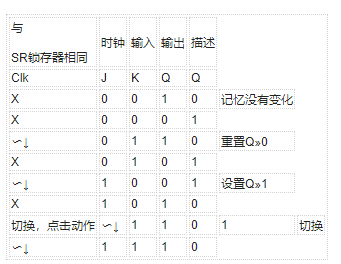

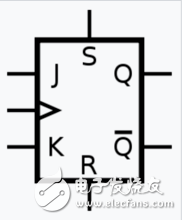

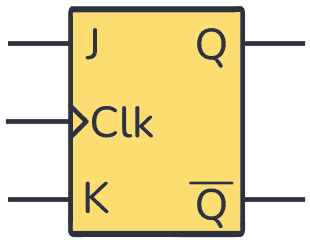

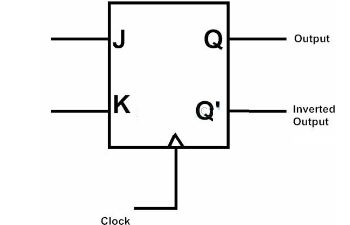

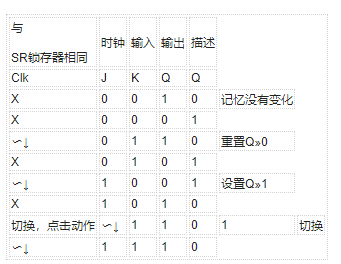

317 JK触发器是一种可以设置、重置和切换的人字拖。它可用于制造计数器、事件检测器、分频器等等。

2023-06-29 11:48:23 7207

7207

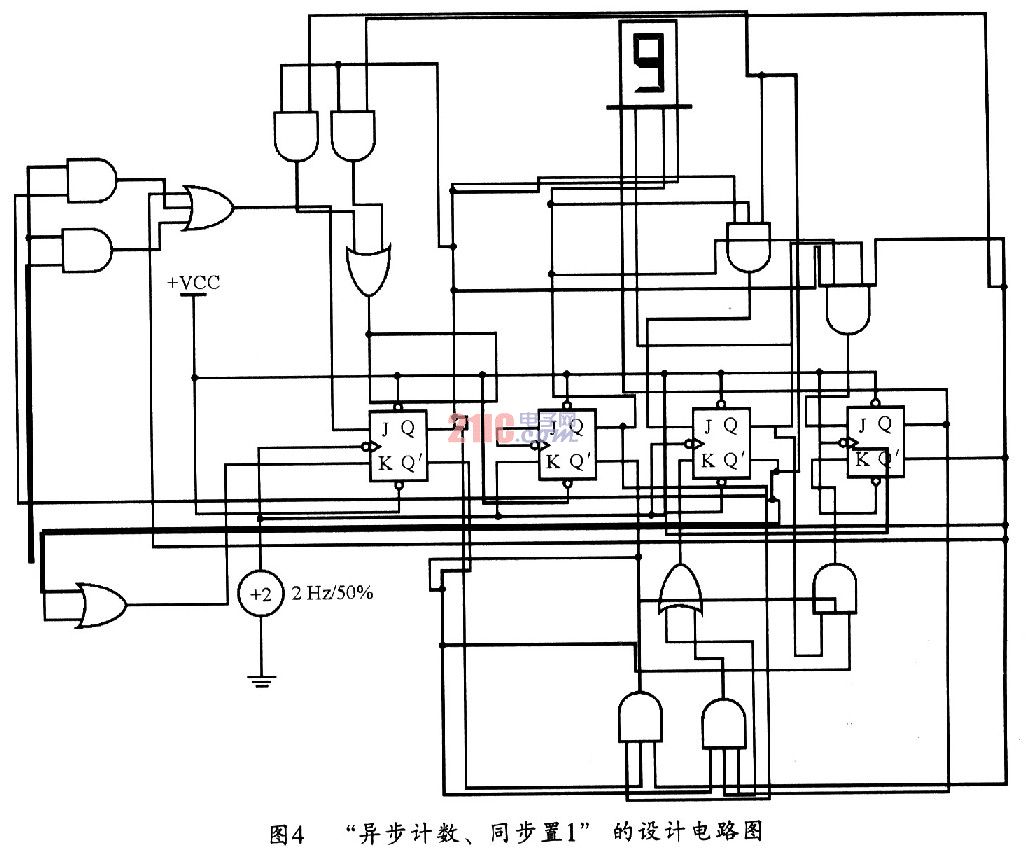

集成触发器、集成计数器及译码显示电路实验目的1. 验证基本RS、D、JK触发器的逻辑功能。2. 了解十进制加法计数器和减法计数器的工作过程。3. 了解计数、译码、显示电路的工作状态。实验原理在数字电路

2008-12-11 23:38:01

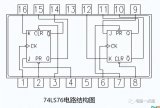

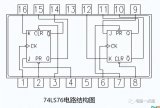

同样值得注意的是,JK 触发器可以通过施加时钟脉冲信号来改变它们的状态。请注意,此时钟信号可以是上升沿或下降沿。此外,74LS76 能够忽略无效输出。

2023-05-05 09:26:31 3551

3551

具有置位和复位功能的双 JK 触发器;上升沿触发-74HC_HCT109_Q100

2023-02-20 19:08:44 2

2 带复位功能的双 JK 触发器;下降沿触发-74HC73_Q100

2023-02-17 19:04:31 3

3 具有置位和复位功能的双 JK 触发器;下降沿触发-74HC_HCT112

2023-02-17 18:47:06 1

1 带复位功能的双 JK 触发器;下降沿触发-74HC_HCT107

2023-02-16 19:58:24 1

1 带复位功能的双 JK 触发器;下降沿触发-74HC_HCT107_Q100

2023-02-16 19:58:13 0

0 具有置位和复位功能的双 JK 触发器;正 - 边 - 触发-74HC_HCT109

2023-02-15 20:02:18 1

1 带复位功能的双 JK 触发器;下降沿触发-74HC73

2023-02-15 19:33:13 3

3 双JK触发器-HEF4027B

2023-02-15 18:41:34 1

1 双JK触发器-HEF4027B_Q100

2023-02-15 18:41:18 0

0 JK触发器也称为通用可编程触发器,因为使用其J、K输入具有预置和清除功能,它可以模仿任何其它触发器的功能。

2022-09-20 16:42:19 24691

24691

1、掌握触发器功能的测试方法。

2、掌握基本RS触发器的组成及工作原理。

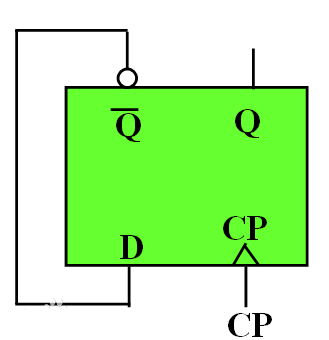

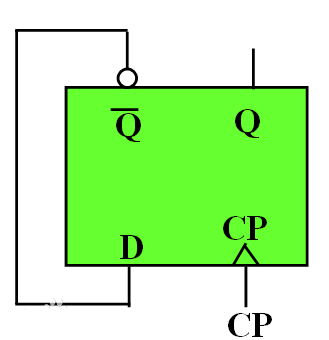

3、掌握集成JK触发器和D触发器的逻辑功能及触发方式。

4、掌握几种主要触发器之间相互转换的方法。

5、通过实验、体会CPLD芯片的高集成度和多I\O口。

2022-07-10 14:39:58 18

18 本文档的主要内容详细介绍的是JK触发器与RS触发器到底是如何构成的有什么区别

2020-05-09 08:00:00 0

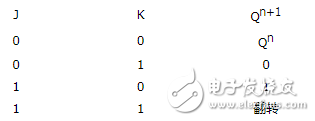

0 JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 79652

79652

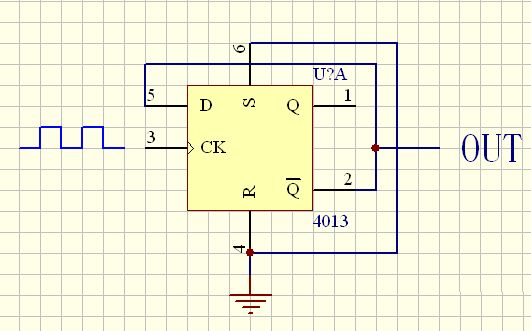

分频就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。而二分频就是通过有分频作用的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。

2019-10-08 09:05:00 21392

21392

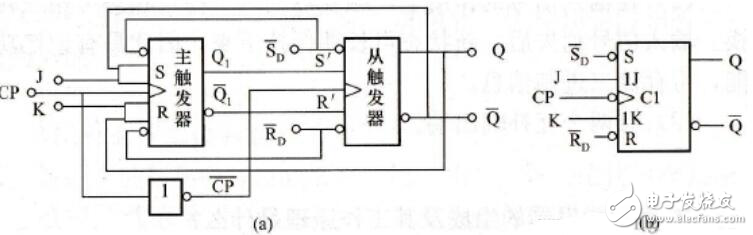

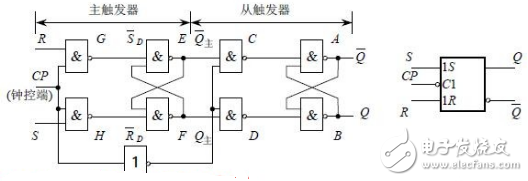

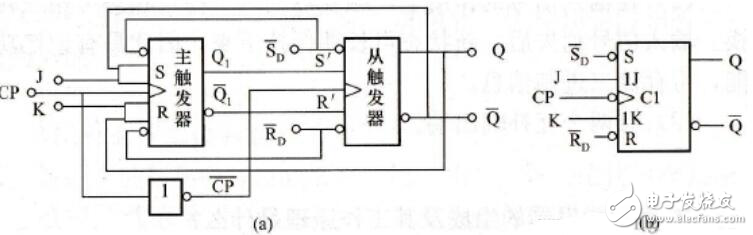

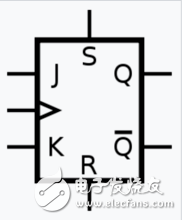

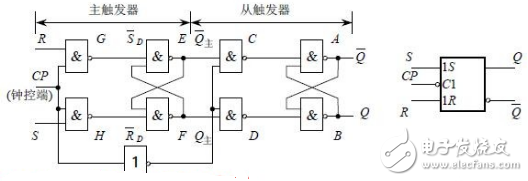

为了解决输入信号之间的约束问题,避免输入端r、s出现全1的情况,可将电路改进为主从型jk触发器,简称为jk触发器。

2019-08-05 15:49:42 37763

37763

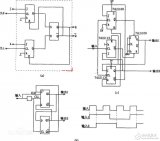

设计了一种基于源级耦合结构的正交二分频电路,由两个完全相同的源级耦合D触发器级联构成,交替工作于触发和锁存模式。

2019-07-13 11:28:37 2185

2185

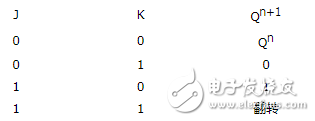

JK触发器类似于SR触发器,但当J和K输入均为低电平时,状态没有变化,JK触发器的顺序操作与前一个具有相同“设置”和“复位”输入的SR触发器完全相同。这次的不同之处在于,即使 S 和 R 都处于逻辑“1”,“JK触发器”也没有SR Latch的无效或禁止输入状态。

2019-06-26 15:56:51 4912

4912

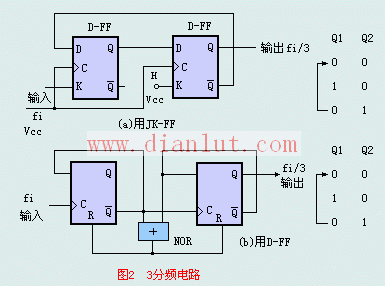

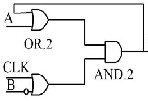

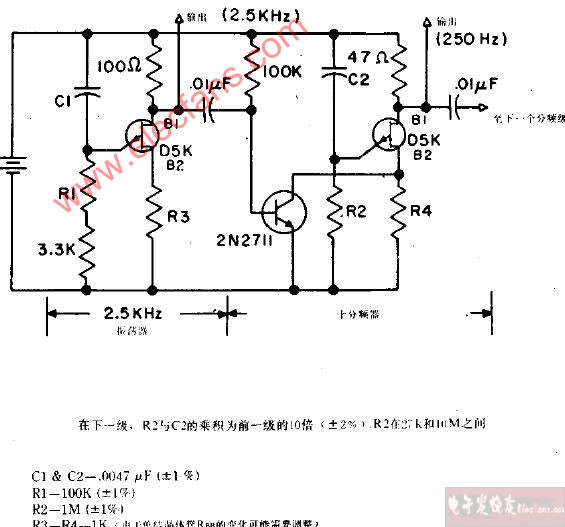

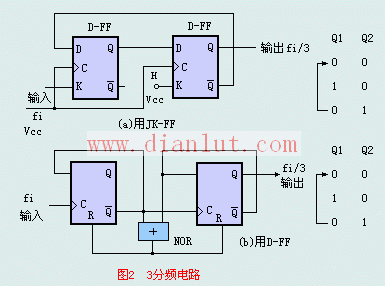

关键词:74LS109 , 74LS113 , 分频电路 如图所示为对称输出的三分频电路。在一般的利用常规计数器对数字脉冲进行奇数分频时.即使输入是对称信号,输出也得不到占空比为50%的分频输出,其

2018-09-28 09:47:01 1256

1256 三分频电路,在电路图中,在一般的利用常规计数器对数字脉冲进行奇数分频时,即使输入是对称信号, 输出也得不到占空比为50%的分频输出,其原因是内部触发器采用的是统一的上升沿(或下降沿)进行触发。

2018-08-13 11:08:34 104910

104910

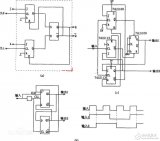

采用基于D 触发器结构的五分频器逻辑框图如图1所示。图1 由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B, 然后对时

2018-04-18 14:04:00 8105

8105

JK触发器和触发器中最基本的RS触发器结构相似,其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。当J与K同时变为1的同时,输出的值状态会反转。也就是说,原来是0的话,变成1;原来是1的话,变成0。

2018-02-08 15:06:44 40171

40171

JK触发器,英文名称为JK flip-flop,是数字电路触发器中的一种基本电路单元,具有置0、置1、翻转和保持的功能,是各集成触发器中功能最为齐全的,具有很强的通用性和无需考虑一次变化的特点,且其能较为灵活地转换成D触发器、T触发器等其他类型的触发器。

2018-02-08 14:51:32 60909

60909

K触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2018-02-08 14:36:43 48950

48950

本文开始介绍了JK触发器工作特性与边沿JK触发器的特点,其次介绍了边沿JK触发器工作原理与特点,最后介绍了集成边沿式JK触发器边沿式JK触发器设计及波形仿真图形。

2018-01-30 17:17:49 34337

34337

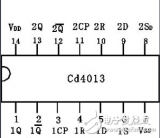

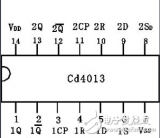

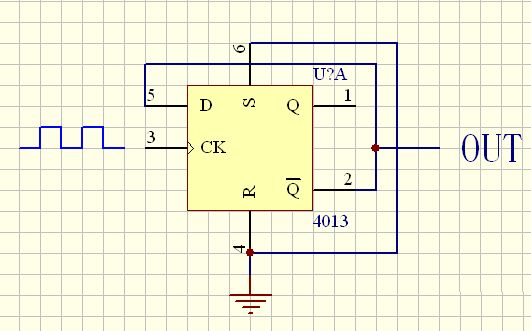

CD4013是双D触发器,在以CD4013为主组成的若干个二分频电路的基础上,加上异或门等反馈控制,即可很方便地组成N/2分频电路。

2018-01-10 14:55:08 14965

14965

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2017-12-25 17:30:03 172587

172587

JK触发器是数字电路触发器中的一种基本电路单元。本文以jk触发器为中心,主要介绍了JK触发器工作特性以及jk触发器是如何实现74ls194功能的。

2017-12-22 16:09:04 21329

21329

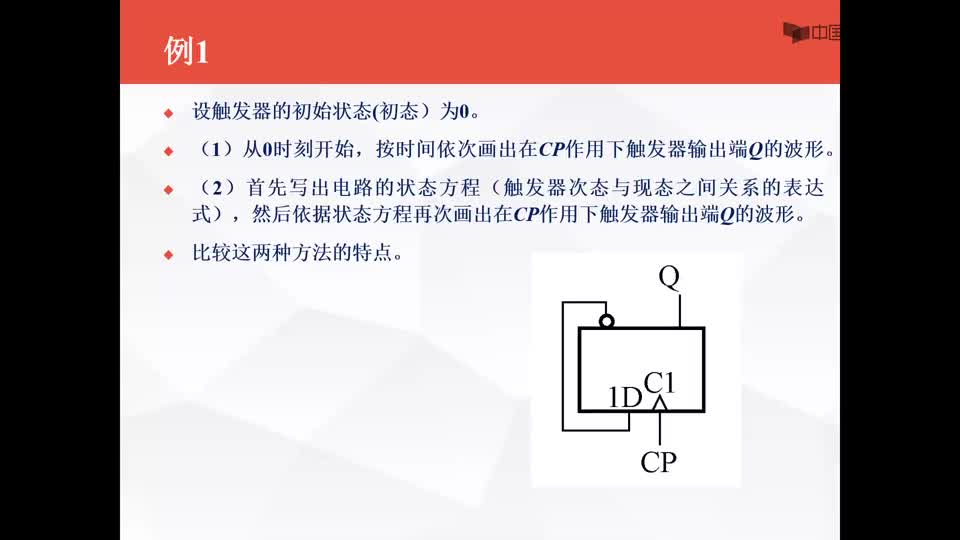

触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

2017-11-02 10:20:40 92552

92552

由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B

2011-11-25 15:16:42 29662

29662

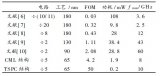

本内容介绍了采用新触发器的高速CMOS 前置分频器 ,欢迎大家下载

2011-07-26 18:05:25 37

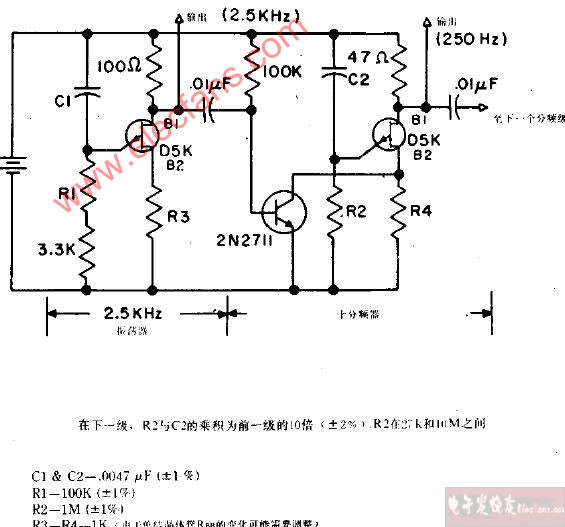

37 分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作用。尤其在中、高频部分,分频电路所起到的作用就更为明显。

2011-07-23 10:47:46 34049

34049

在电子技术中,N/2(N为奇数)分频电路有着重要的应用.对一个特定输入频率,要经N/2分频后才能得到所需要的输出,这就要求电路具有N/2的非整数倍的分频功能。CD4013是双D触发器,在以CIM013为主组成的若干个二分频电路的基础上,加上异或门等反馈控{6I,即

2011-03-11 17:05:45 338

338 上例图中A将D触发器的D端和Q相连,即可组成二分频电路,如果把三个D触发器串行相连,如图所示,则经过一

2010-09-20 03:40:48 11549

11549 1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 233

233 触发器是数字电路的基本逻辑单元之一,也是构成各种时序电路的最基本逻辑单元。

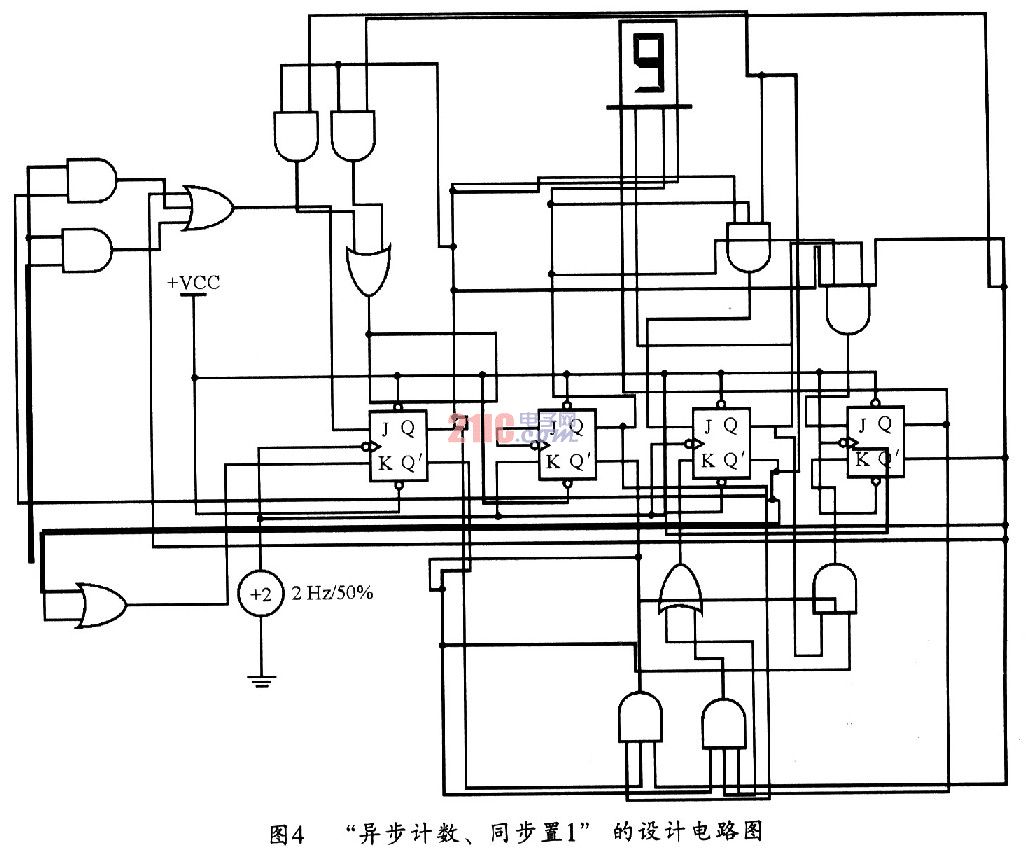

文中给出了基于JK触发器来设计十二归一计数器的设计和实现方法,并通过EWB软件进行了

2010-06-30 15:58:29 14012

14012

JK触发器工作原理详细介绍

JK触发器,采用与或非电路结构,它的工作原理为:CP为0时,触发器处于一个稳态;CP由0变1时,触发器不

2010-03-08 13:47:58 48856

48856 JK触发器原理是什么?

JK触发器是一种功能较完善,应用很广泛的双稳态触发器。图9-5(a)所示是一种典型结构的JK触发器——主从型JK触

2010-03-08 13:41:11 23241

23241 JK触发器,JK触发器是什么意思

1.主从JK触发器主从结构触发器也可以彻底解决直接控制,防止空翻。这里以性能优良、广泛使用的主从JK触发器为

2010-03-08 13:36:29 5842

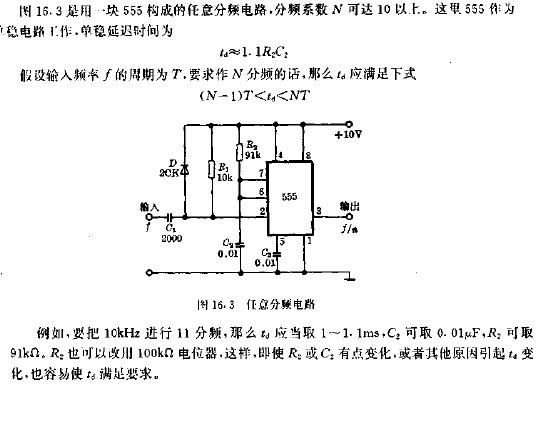

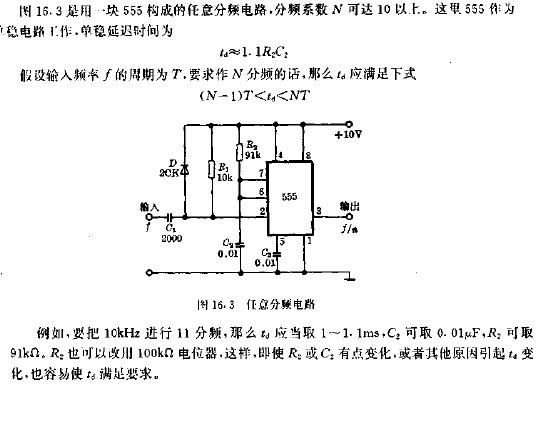

5842 10分频电路

任意分频电路图

2009-06-22 08:04:33 15267

15267

用VHDL语言实现3分频电路(占空比为2比1)

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁

2009-06-22 07:46:33 7482

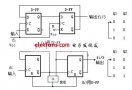

7482 用于N=2-4分频比的电路,常用双D-FF或双JK-FF器件来构成,分频比n>4的电路,则常采用计数器(如可预置计数器)来实现更为方便,一般无需再用单个FF来组合。

2009-06-22 07:43:15 6925

6925

d触发器构成2分频电路

2009-06-22 07:36:33 7322

7322

D触发器实现二分频电路(D触发器构成的2分频电路)&

2009-06-12 13:58:56 73460

73460

十分频器电路图

2009-03-29 09:57:00 6221

6221

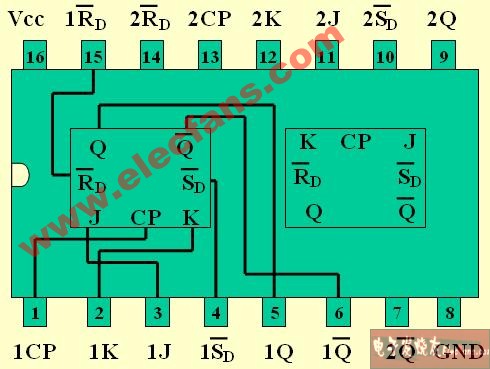

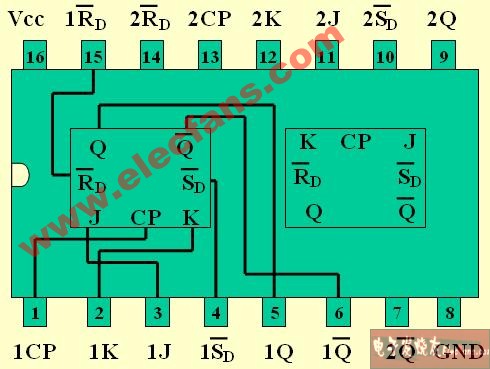

74LS112型双JK触发器芯片引脚图管脚图

2009-02-14 15:31:52 80421

80421

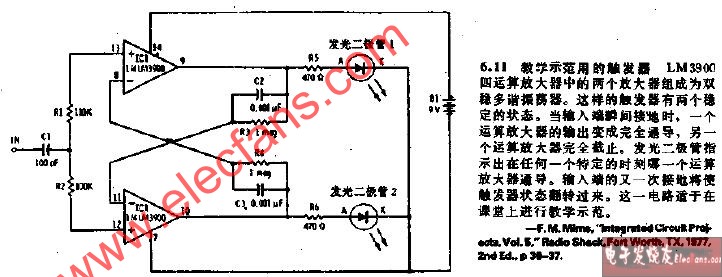

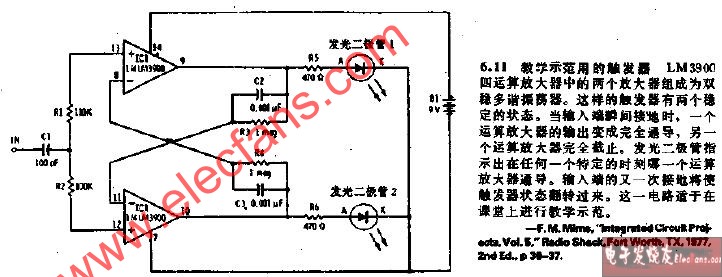

教学示范用的触发器电路

2009-01-17 14:04:09 426

426

供数字时钟使用的+5000分频器电路

2009-01-13 20:07:47 1036

1036

一、实验目的1、掌握基本RS、JK、D和T触发器的逻辑功能2、掌握集成触发器的逻辑功能及使用方法3、熟悉触发器之间相互转换的方法二、实验原理触发器具有两个稳

2008-12-19 00:40:23 48

48 下图是 用于N=二-四分频比的电路,常用双D-FF或双JK-FF器件来构成,分频比n>4的电路,则常采用计数器(如可预置计数器)来实现更为方便,一般无需再用单个FF来组合。

2008-06-29 23:31:06 21911

21911

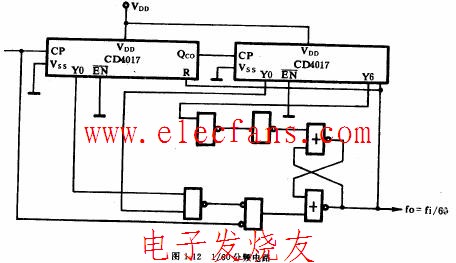

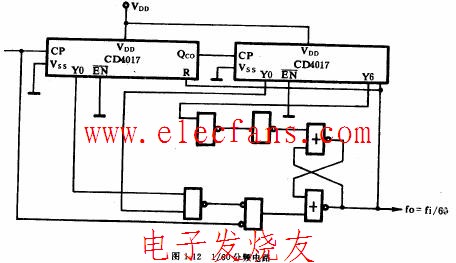

1/60分频电路

2008-06-29 22:16:51 2156

2156

主从jk触发器电路及工作原理

2008-01-21 14:00:16 15230

15230

cd4013双d触发器

CD4013双D触发器做的脉冲4分频器应用

-----------------------------. ┌─────

2008-01-09 23:48:45 4487

4487 用VHDL语言实现3分频电路

标签/分类:

众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相

2007-08-21 15:28:16 5374

5374

电子发烧友App

电子发烧友App

评论