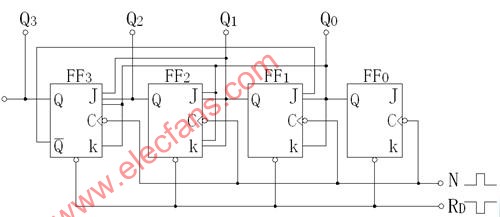

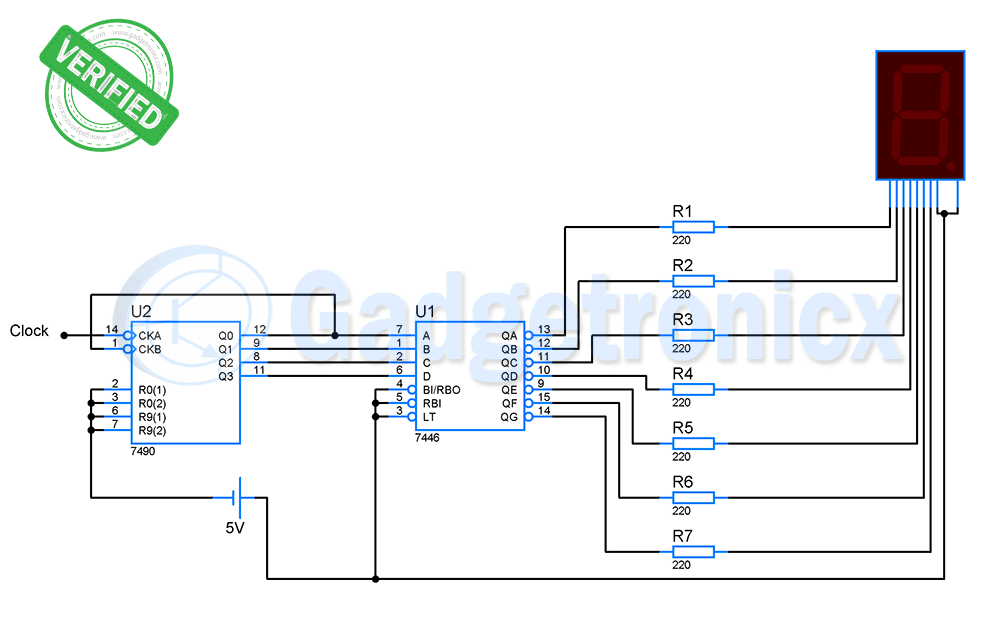

8421码同步十进制递增计数器

电子发烧友App

电子发烧友App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网>电子技术应用>电子技术>电路图>数字电路图>8421码同步十进制递增计数器

相关推荐

435

435

0

0 2

2 11019

11019

868

868

17

17 34099

34099

6

6 2650

2650 2050

2050 54071

54071

44957

44957

73133

73133

179839

179839

30273

30273

106188

106188

25181

25181

145644

145644

182091

182091

52599

52599

110315

110315

534630

534630

148134

148134

224996

224996

60783

60783

81

81 28

28 24

24 115

115 12142

12142 23684

23684 29984

29984 5522

5522 8495

8495 1940

1940

106

106 3559

3559

评论