时序逻辑电路的特点是输出信号不仅与电路的输入有关,还与电路原来的状态有关。

2023-09-17 16:22:32 836

836

时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 441

441

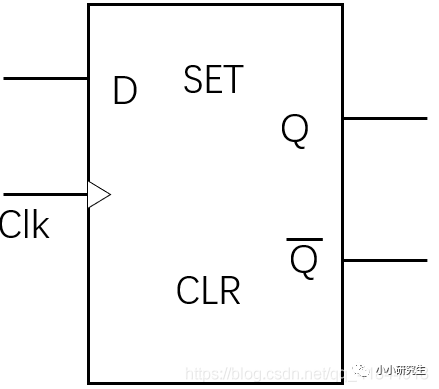

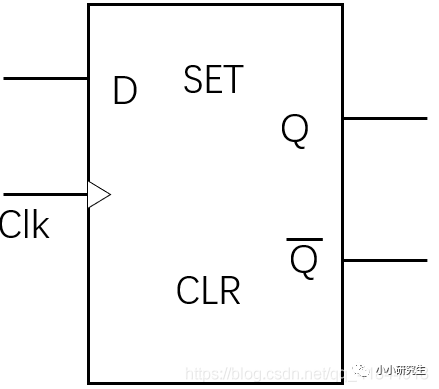

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 830

830

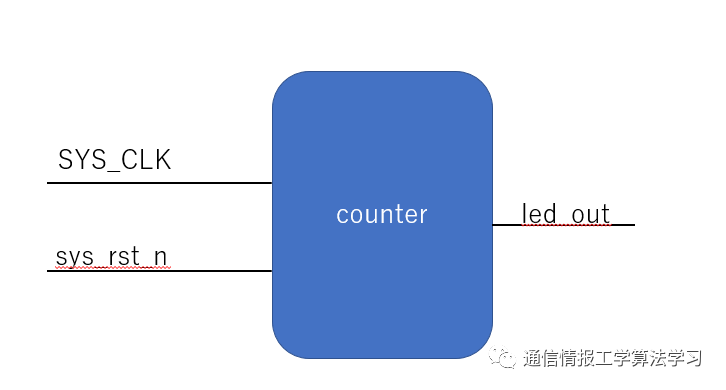

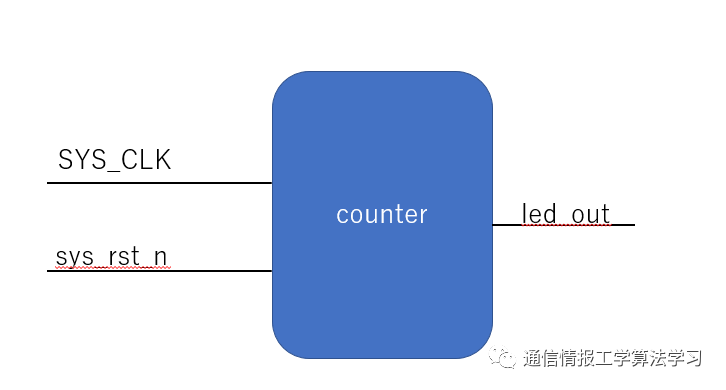

时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 680

680

前面已经学习了时序逻辑电路中的基本单元:触发器,这次就用其来整点活,实现计数器的设计,计数器可以说是任何和时序有关的设计都会用到他。

2023-05-22 16:54:50 886

886

时序逻辑电路会复杂很多,强烈推荐mooc上华中科技大学的数字电路与逻辑设计,是我看过讲得最清楚的数电课。

2023-05-14 15:11:33 1093

1093

、可编程器件设计时序逻辑电路的特点、方法;3 掌握时序逻辑电路的调试方法;4 进一步提高排除数字电路故障的能力。

2009-03-19 15:10:18

数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 258

258 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 2914

2914

时序逻辑电路的精华——计数器

2022-12-29 09:23:56 748

748 数字电路的分类

(1)按电路结构分类

组合逻辑电路

时序逻辑电路:。

(2)按集成电路规模分:小规模、中规模和大规模。

2022-12-05 14:54:47 7

7 时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。

2022-12-05 14:49:30 6

6 从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。

2022-10-10 15:39:01 681

681 时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表...

2021-11-06 10:36:00 19

19 本文来自芯社区,谢谢。1:什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统

2021-11-06 10:21:02 4

4 了解吗? (1)纯组合逻辑电路的缺点在哪? (3)纯组合逻辑电路完成不了什么功能? (2)为什么需要时钟和寄存器呢? 带着这三个疑问我们来认识一下时序逻辑电路。 二. 同步时序逻辑电路的作用 1. 时序逻辑电路对于组合逻辑的毛刺具有容忍度,

2020-12-25 14:39:28 3607

3607

1、什么是同步逻辑和异步逻辑? 同步时序逻辑电路的特点:电路中所有的触发器都是与同一个时钟或者该时钟的衍生时钟驱动,而且当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下 一个时钟脉冲

2020-11-19 15:13:15 1214

1214

本文档的主要内容详细介绍的是组合逻辑电路和时序逻辑电路的学习课件免费下载包括了:任务一 组合逻辑电路,任务二 编码器,任务三 译码器,任务四 集成触发器,任务五 寄存器,任务六 计数器。

2020-10-27 15:58:24 28

28 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入x 有无变化,状态表

2020-10-22 17:57:31 11

11 1:什么是同步逻辑和异步逻辑?(汉王)

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。答案应该与上面问题一致〔补充〕:同步时序逻辑电路的特点:各触发器的时钟端全部连接

2020-09-04 17:18:30 5

5 本文档的主要内容详细介绍的是模拟电路教程之时序逻辑电路的课件资料免费下载包括了:1 概述,2 时序逻辑电路的分析方法,3 若干常用的时序逻辑电路,4 时序逻辑电路的设计方法。

2020-06-22 08:00:00 13

13 掌握时序逻辑电路的设计方法及调试技巧,熟练掌握触发器的功能及应用,熟练掌握常用MSI时序逻辑芯片的功能及应用

2020-05-20 08:00:00 19

19 同步时序逻辑电路的特点:电路中所有的触发器都是与同一个时钟或者该时钟的衍生时钟驱动,而且当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下 一个时钟脉冲的到来,此时无论外部输入有无变化,寄存器状态都是稳定的。

2020-01-30 17:24:00 3703

3703 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 7133

7133

从整体上来看,数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。在逻辑功能方面,组合逻辑电路在任一时刻的输出信号仅与当时的输入信号有关,与信号作用前电路原来所处的状态无关;而时序逻辑电路在任一时刻的输出信号不仅与当时的输入信号有关,而且还与电路原来的状态有关。

2019-05-16 18:27:52 9048

9048

将驱动方程代入相应触发器的特性方程中,便得到该触发器的次态方程。时序逻辑电路的状态方程由各触发器次态的逻辑表达式组成。

2019-02-28 14:06:14 22685

22685 组合逻辑电路是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路不仅仅取决于当前的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-02-26 15:32:30 60005

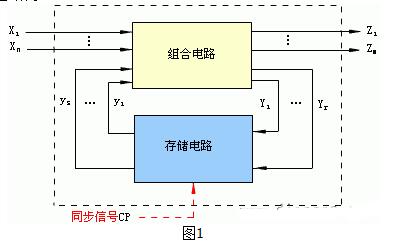

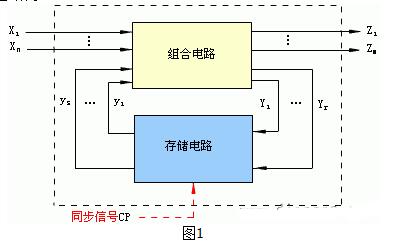

60005 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 48178

48178 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 29485

29485 本文档的主要内容详细介绍的是数字电路教程之时序逻辑电路课件的详细资料免费下载主要内容包括了:一 概述,二 时序逻辑电路的分析方法,三 若干常用的时序逻辑电路,四 时序逻辑电路的设计方法,五 时序逻辑电路中的竞争冒险现象

2018-12-28 08:00:00 9

9 本文档的主要内容详细介绍的是如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现。

2018-12-12 16:25:46 7

7 本文档的主要内容详细介绍的是数字电路基础教程之时序逻辑电路的详细资料概述。内容包括了:1.时序逻辑电路分析2.若干常用时序逻辑电路3.时序逻辑电路设计

2018-10-17 08:00:00 41

41 根据逻辑功能的不同,可把数字电路分为组合逻辑电路(Combinational Logic Circuit)和 时序逻辑电路(Sequential Logic Circuit)两大类。

2018-07-20 08:00:00 4

4 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时 钟脉冲的到来,此时无论外部输入 x有无

2018-07-06 10:00:00 2759

2759 时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑电路有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

2018-04-09 16:00:00 5279

5279

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 104785

104785

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 51593

51593

时序逻辑路是数字电路的一种,时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 19:19:25 61100

61100

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 120321

120321

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 89189

89189

逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。单一的与门、或门、与非门、或非门、非门等逻辑门不足以完成复杂的数字系统设计要求。组合逻辑电路是采用两个或两个以上基本逻辑门来实现更实用、复杂的逻辑功能。

2018-01-30 17:05:44 59977

59977

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

2018-01-30 16:24:25 35974

35974

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-29 11:28:01 9071

9071

逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。

2017-05-22 15:15:59 67979

67979

数字电子技术--时序逻辑电路

2016-12-12 22:07:22 1

1 数字电子技术-- 时序逻辑电路

2016-12-12 21:54:28 8

8 电子专业单片机相关知识学习教材资料之时序逻辑电路的分析与设计

2016-09-02 14:30:26 20

20 主要讲了时序逻辑电路的相关知识,能够方便大家学习使用

2016-02-29 14:25:53 3

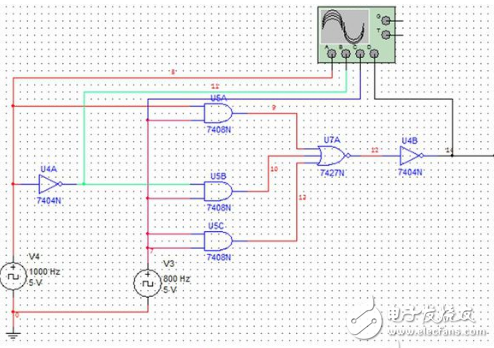

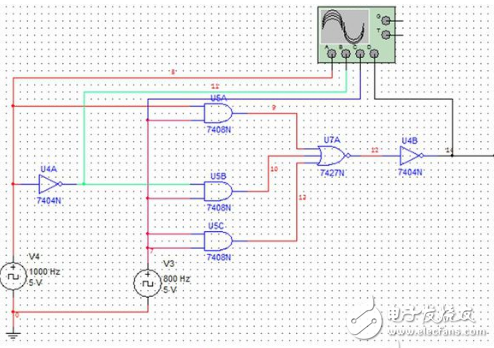

3 通过介绍Multisim软件的功能和特点,结合格雷玛计数器的设计实例,叙述了在Multisim软件平台进行时序逻辑电路的设计原理及构成方法,并利用软件对设计进行仿真。

2012-02-10 16:43:10 133

133 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

55 主要教学内容(注明:* 重点 # 难点 ): 1. 时序逻辑电路特点、分类及其功能表示方法;

2. 触发器功能及功能分类;

2010-08-18 14:52:24 46

46 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 67

67 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 23

23 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 47

47 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则与它不同,其特点是:在任意时刻电路产生的稳定输出不仅与当前时刻的输入

2010-05-30 09:46:59 43

43 摘要:文章介绍了Multisim9仿真软件在数字电子技术中时序逻辑电路中的应用,从时序逻辑电路分析、计数器、寄存器等方面介绍了Multisim9仿真软件的优点,提出了Multisim9仿真软件的

2010-05-30 08:21:04 73

73 时序逻辑电路实例解析

一、触发器 1、电位触发方式触发器

2010-04-15 13:46:25 4871

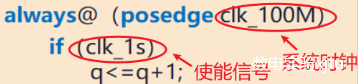

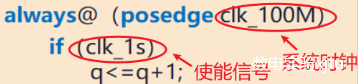

4871 Verilog HDL语言实现时序逻辑电路

在Verilog HDL语言中,时序逻辑电路使用always语句块来实现。例如,实现一个带有异步复位信号的D触发器

2010-02-08 11:46:43 4371

4371 数字逻辑电路

数字逻辑电路的用途和特点

数字电子电路中的后起之秀是数字逻辑电路。把它叫做数字电路是因为电路中传递的虽然也是脉冲,但这些脉冲是

2009-11-10 10:13:26 16998

16998 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 59

59 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 71

71 组合逻辑电路电子教案:数字逻辑电路可分为两大类: 一类叫组合逻辑电路;另一类叫时序逻辑电路。本章首先介绍组合逻辑电路的共同特点和描述方法,然后重点介绍组合逻辑电

2009-09-01 08:58:29 86

86 组合逻辑电路(简称组合电路)任意时刻的输出信号仅取决于该时刻的输入信号,与信号作用前电路原来的状态无关时序逻辑电路(简称时序电路)任意时刻的输出信号不仅取决

2009-07-15 18:45:58 62

62 时序逻辑电路分析实例

例1 分析图所示电路的逻辑功能。设起始状态是

2009-04-07 23:20:25 4247

4247

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 7731

7731

第二十七讲 同步时序逻辑电路的设计

7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步时序逻辑电路的设计方法

2009-03-30 16:31:56 3156

3156

时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 1 进一步强化EDA仿真软件的使用;2 掌握利用MSI、可编程器件设计时序逻辑电路的特点、方法;3 掌握时序逻辑电路的调试方法;4&

2009-03-18 20:06:31 47

47 实验十六 时序逻辑电路? 实验(1) 计数器?一、实验目的?⒈ 熟悉计数器的设计方法及工作原理。?⒉ 了解同步计数器与异步计数器的区别。?⒊ 应用

2008-09-24 22:17:08 3155

3155

电子发烧友App

电子发烧友App

评论