三态门的组成及工作原理

- 三态门(18568)

相关推荐

什么是三态门和OC门?

三态门和OC门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。因此,需要一种新的与非门电路来实现线与逻辑,这种门电路

2008-05-26 13:01:37

三态输出的缓冲器有哪些用途?

三态输出的缓冲器有哪些用途? 三态输出缓冲器是一种电子元件,其主要作用是将一个输入信号转换成一个可以控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信

2023-09-21 15:55:36 389

389

389

389Versal HDIO OBUFT和IOBUF三态时序影响

本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF) 的 HDIO 输出缓冲器的上电电压为 3.3 V 或 2.5 V 并且 Data(数据)控制信号与 Tristate(三态)控制信号的切换时间彼此相近,则可能会受到三态数据争用条件的影响。

2023-07-12 09:50:32 213

213

213

213

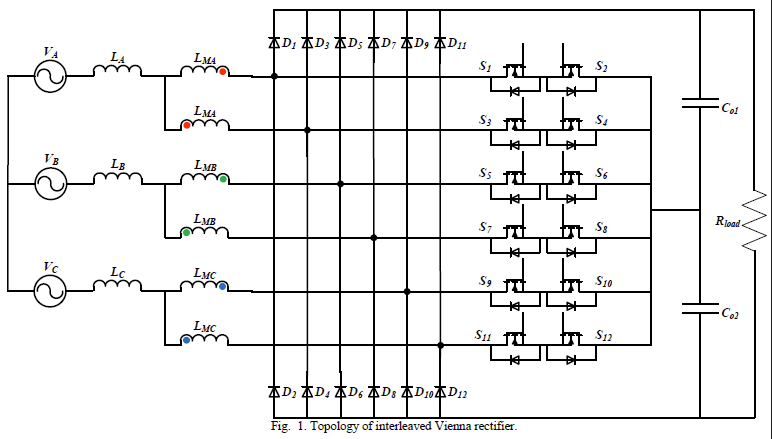

三相五电平VIENNA的工作原理

该拓扑与传统三相三电平VIENNA主要区别是每相都有一个三态开关电路。所谓三态开关中的“三态”,就是指每相都会有三种开关状态或者工作状态,同时会在桥臂端口Vx点的位置形成五种电平状态,因此也称

2023-03-23 09:26:27 1972

1972

1972

1972

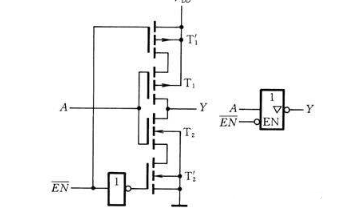

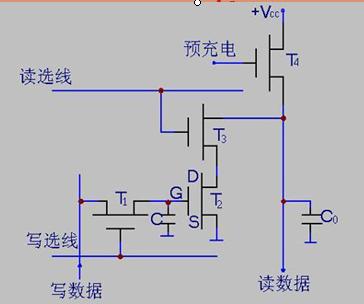

FPGA三态门的结构是怎样的呢?

由上图看出,在单相三态门中,当EN=1时,对原电路无影响,电路的输出符合原来电路的所有逻辑关系,即A可以输出到B。当EN= 0时,电路内部的所有输出与外部将处于一种关断状态。

2022-10-20 11:01:02 904

904

904

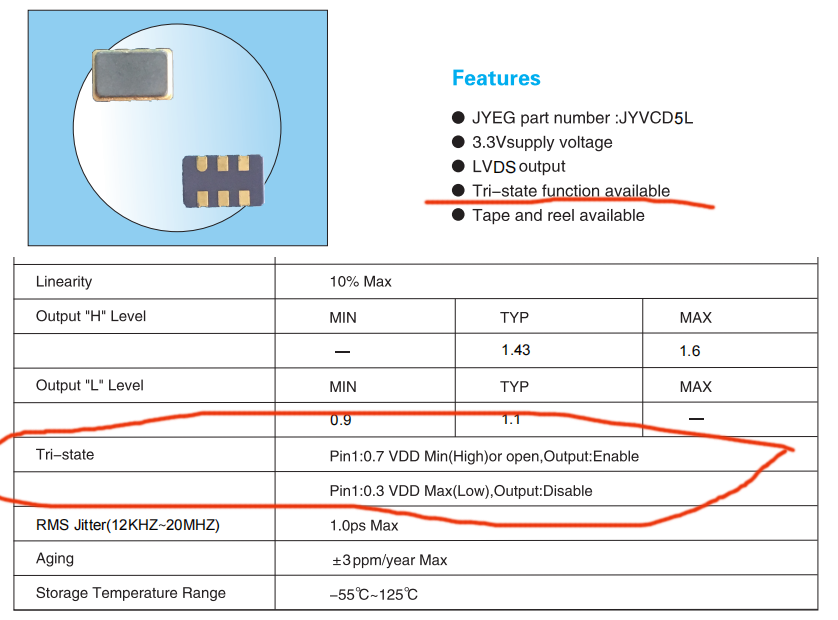

904晶体振荡器的三态功能及控制逻辑

选购石英晶体振荡器(XO)时,有些规格书(datasheet)标有三态(tri-state)控制功能,有些则没有该功能。那么,三态控制究竟是什么神秘武器?

2022-07-25 08:54:03 1828

1828

1828

1828

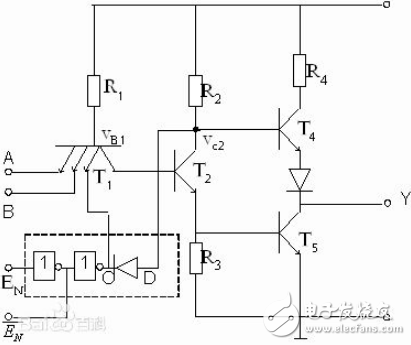

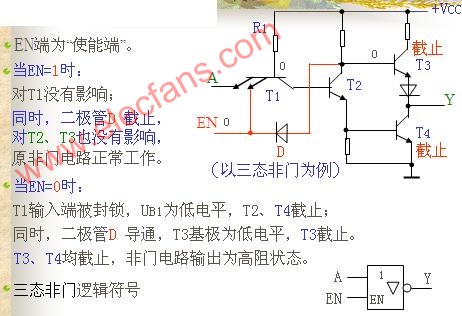

三态输出门的工作原理

三态输出门电路的输出端除了出现高、低电平外,还会出现第三种状态——高阻态,所以叫做三态输出门电路。 三态门的工作原理: 当控制端a为“1”时,b型管3导通,同时a端电平通过反向器成为低电平,让

2021-08-12 11:39:49 10760

10760

10760

10760数字电路常见术语:高阻态,三态门资料下载

电子发烧友网为你提供数字电路常见术语:高阻态,三态门资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-27 08:45:27 13

13

13

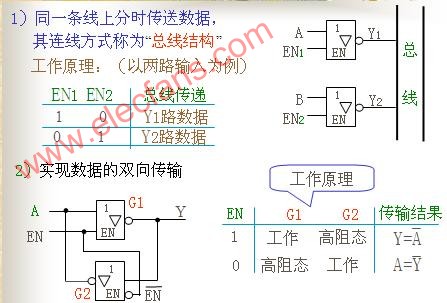

13三态门总线传输电路的工作特性及仿真研究

Multisim仿真软件进行三态总线电路工作过程波形仿真分析,用环形计数器做实验中的信号源产生所需的各个控制信号、用脉冲信号源产生各数据输入信号,用逻辑分析仪多踪同步显示各个三态门的控制信号、数据输入信号及总线输出信号波形,可直观形象地描述三态门总线传输电路的工作特性。

2020-04-18 12:50:00 6304

6304

6304

6304FPGA之三态门

三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-29 07:09:00 3339

3339

3339

3339三态门的用法及模块功能介绍

三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-21 07:05:00 7465

7465

7465

7465三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料

本文档的主要内容详细介绍的是三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料主要内容包括了:1 ModelSimSE的使用流程,2 一个Verilog计数器仿真详细流程附

2019-07-09 16:49:27 9

9

9

9三态门的作用

三态门主要是用于总线的连接,因为总线只允许同时只有一个使用者。通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

2019-03-08 16:49:37 21629

21629

21629

21629三态门输出的三种状态

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态,那么三态门输出的三种状态是什么呢?

2019-02-21 16:45:59 66152

66152

66152

66152三态缓冲器工作原理

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

2018-10-24 16:09:36 32926

32926

32926

32926传输门和三态门什么区别

本文主要介绍了传输门和三态门什么区别,三态门就是指输出有三种状态(0,1,高阻)的门。传输门就是指可以控制通路通断的门,导通时,一端的信号可以传到另一端,不导通时,一端信号不能传到另一端。两者不是

2018-04-08 15:33:49 51792

51792

51792

51792

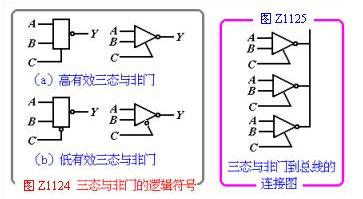

三态门有哪三态_三态门有什么特点

本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出门电路与三态门电路的图形符号与真值表。

2018-03-01 14:47:41 113066

113066

113066

113066

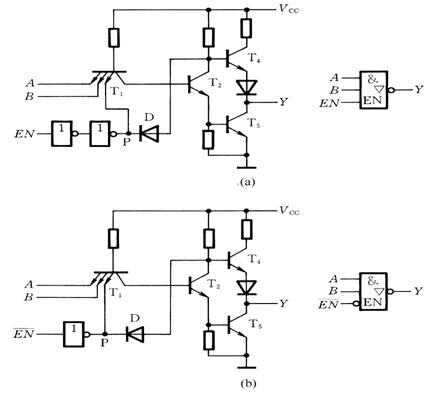

三态门逻辑电路图大全(三款三态门逻辑电路图)

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了三款三态门逻辑电路。

2018-03-01 14:03:10 69342

69342

69342

69342

高阻态实质意义和应用以及三态门的详细分析

低电平,随它后面接的东西定。三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态(门,总线,......)。

2017-12-25 11:27:11 20313

20313

20313

20313

三态门如何在FPGA中实现与仿真

三态门在数字电路上可以说是应用的非常广泛,特别是一些总线上的应用,因而,随着数字电路的发展,就避免不了用硬件描述语言在FPGA上来设计实现三态门。

2017-02-08 11:37:06 7000

7000

7000

7000三态门总线传输电路的Multisim仿真方案

基于探索仿真三态门总线传输电路的目的,采用Multisim10仿真软件对总线连接的三态门分时轮流工作时的波形进行了仿真实验测试,给出了仿真实验方案,即用Multisim仿真软件构成环形计

2013-06-08 17:58:44 48

48

48

48三态门逻辑功能的Multisim仿真方案

介绍了用Multisim仿真软件分析三态门工作过程的方法,目的是探索三态门工作波形的仿真实验技术,即用Multisim仿真软件中的字组产生器产生三态门的控制信号及输入信号,用Multisim中示

2011-05-06 15:59:38 76

76

76

76三态电路在FPGA应用设计中的分析

本文就三态电路在FPGA中的应用作了详细的说明。文章首先描述了一个调用lpm中三态电路模块的VHDL程序,这个程序会出现编译不能通过的问题。然后从这个问题出发,通过尝试三态电

2010-08-06 16:56:22 27

27

27

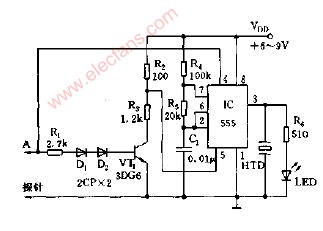

27三态门:计算机的逻辑部件

三态门:计算机的逻辑部件

常用的集成门电路器件分为两大类:CMOS和TTL。 CMOS是由单极型场效应三极管组成集成电路, TTL是晶体管-晶体管逻辑电路

2010-04-15 14:55:00 1685

1685

1685

1685集电极开路门和三态输出门的应用

集电极开路门和三态输出门的应用

一、 实训目的1.熟悉集电极开路门(OC门)和三态输出门(TSL门)的逻辑功能;2.熟悉用OC门构成线与功能;3.熟悉用TSL门

2009-04-07 23:23:53 59

59

59

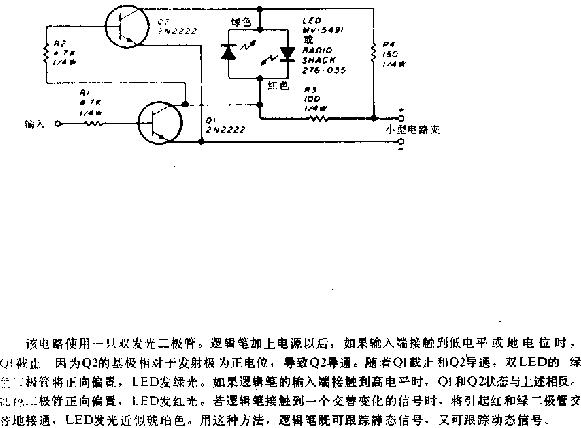

59什么是三态门? 三态逻辑与非门电路以及三态门电路

什么是三态门?

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。

2008-05-26 12:48:24 41856

41856

41856

41856

电子发烧友App

电子发烧友App

评论