4位十进制可逆计数器电路

相关推荐

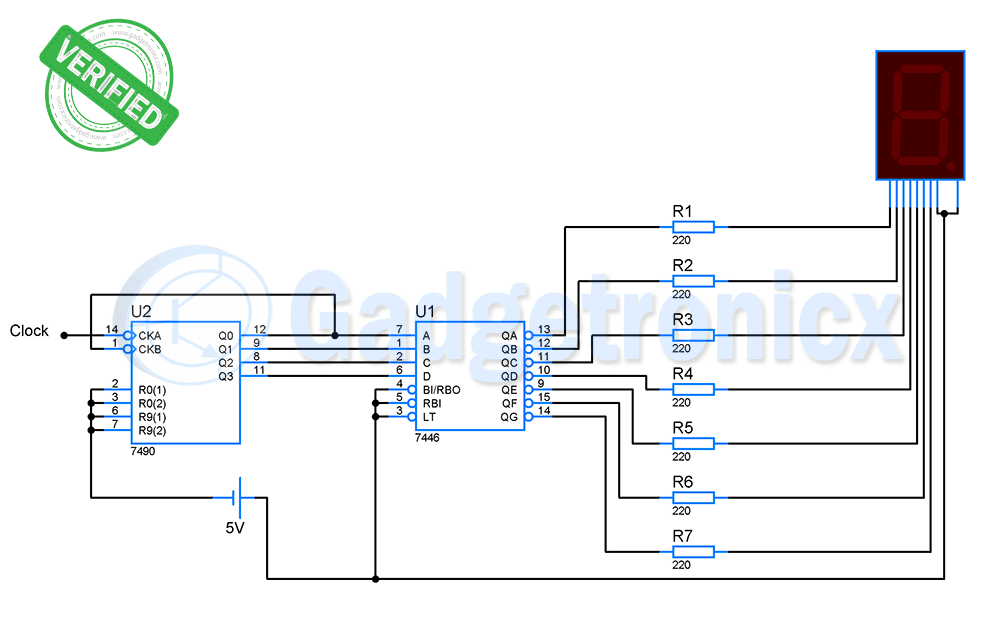

基于异步十进制计数器IC7490的电路

图所示电路是静态的0到9显示,使用能够显示7到0数字的9段。它在日常生活中有很多应用,并使用两个简单的IC的7490和7446实现。该电路基于异步十进制计数器7490(IC2)、7段显示器(D1

2023-07-05 15:51:15 435

435

435

435

带 10 个解码输出的 Johnson 十进制计数器-74HC_HCT4017_Q100

带 10 个解码输出的 Johnson 十进制计数器-74HC_HCT4017_Q100

2023-02-17 19:59:07 0

0

0

0基于FPGA的十进制计数器

本方案是一个基于 FPGA 的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA 板上实现。

2022-12-20 14:52:25 2

2

2

2十进制计数器的工作原理

二进制编码的十进制是一个串行数字计数器,可计数十位数字,它会为每个新的时钟输入重置。由于它可以通过10种独特的输出组合,因此也被称为“十进制(BCD)计数器”。十进制计数器可以计数0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 11019

11019

11019

11019

N进制计数器的实现

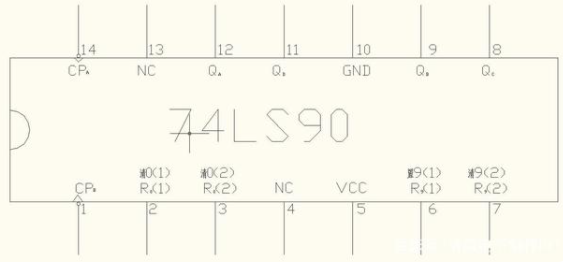

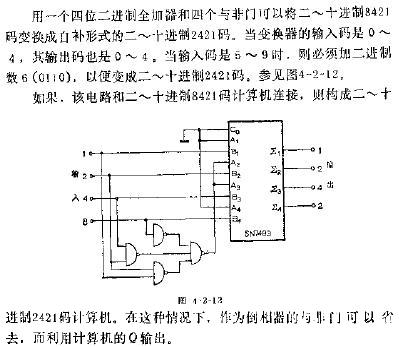

; S92 Q2 Q1 GNDT4290(T1290、74LS290、T210),是一个二-五-十进制计数器,能够进行二进制、五进制计数、通过简单联线组成十进制计数

2008-07-05 13:41:26

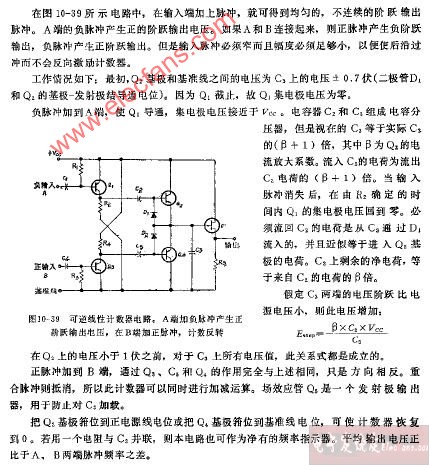

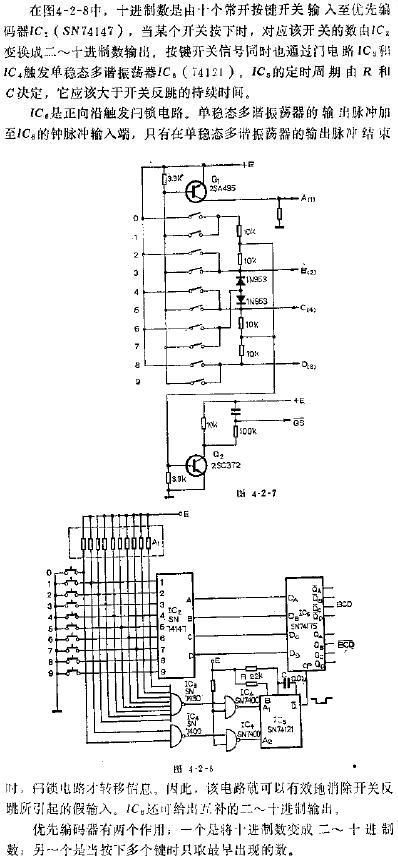

"stm32f0按键计数器程序_数字系统设计, 8个经典计数器电路方案合辑"

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按

2021-11-25 18:06:07 32

32

32

3274ls161十进制计数器电路图

74LS161为4位二进制同步加法计数器。其中 是异步清零端, 是预置数控制端,D3 D2 D1 D0是预置数输入端,CTt和CTp是计数使能端,CO是进位输出端(CO=Q3 Q0

2021-07-09 16:12:21 73502

73502

73502

73502

74LS90十进制计数器的功能电路及真值表

其中CPa和Qa构成1位二进制计数器,CPb和Qd、Qc、Qb 组成五进制计数器,将两个计数器有关端子适当组合,可以组成其他类型的计数器。R0(1)、R0(2)为两个清0端,R9(1)、 R9(2)为两 个置9端。

2021-06-21 09:39:44 34099

34099

34099

34099

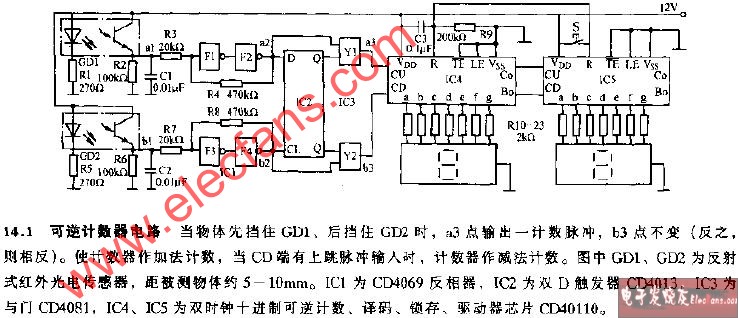

CD40110十进制加减计数器锁存器译码器驱动器的数据手册免费下载

40110 为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码输出等功能。

2019-04-30 08:00:00 6

6

6

6由TTL十进制计数器构成的分频器

关键词:TTL , 分频器 , 计数器 , 十进制 如图所示为由TTL十进制计数器构成的分频电路。在许多情况下。需要对脉冲序列进行N(N为整数)分频。例如,数字钟需要进行60分频,得到重复频率为

2018-10-03 18:46:02 2650

2650

2650

2650二进制与十进制数对照显示实验,十进制,二进制对照

CD4040组成加法计数器,手动加1计数。

2.二进制与十进制数字对照显示实验 本电路可以形象地显示0~9的二进制数。按动加1按钮AN2,计数器的输入端CP得到一个负脉冲信号,计数器进行加1

2018-09-20 18:26:41 2050

2050

2050

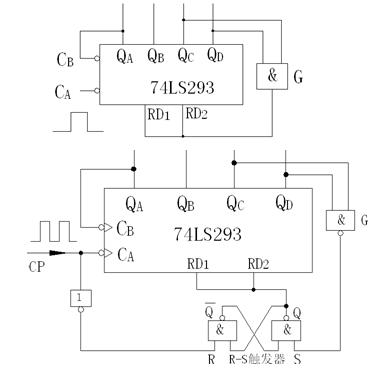

205074ls190应用电路图大全(五款74ls190不同进制计数器电路)

本文主要介绍了五款74ls190应用电路图。包括了60和100进制计数器(递增)电路,56进制递减计数器与100进制递减计数器电路和2位十进制可加减计数器电路。

2018-05-28 16:18:11 54071

54071

54071

54071

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)

本文主要介绍了五款74ls192计数器应用电路图。其中包括了74ls192电子骰子电路、74ls192计时电路、74ls192定时电路、74ls19230进制计数器电路及两位十进制计数器。

2018-05-28 10:20:01 116393

116393

116393

116393

两个74LS192级联构成两位十进制计数器

本文主要介绍了两个74LS192级联构成两位十进制计数器。以两个74LS192级联构成两位十进制计数器控制实现0.0~9.9V的切换为例。低位计数器输出Qo、Qi、Q2、Q3分别提供0.1V

2018-05-09 09:52:23 53651

53651

53651

53651

74ls163实现十进制计数器电路

本文主要介绍了74ls163实现十进制计数器电路。改变74LS163二进制计数器为十进制计数器,即用一FDS4435BZ个与非门,其两个输人取自QA和QD,输出接清零端α‘R。当第9个脉冲结束时,钣

2018-05-08 11:31:20 44957

44957

44957

44957

CD40110组成的一位数码计数器

本文主要介绍了CD40110组成的一位数码计数器。CD40110为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码输出等功能。CD40110有2个计数时钟输入端

2018-03-04 11:17:34 18394

18394

18394

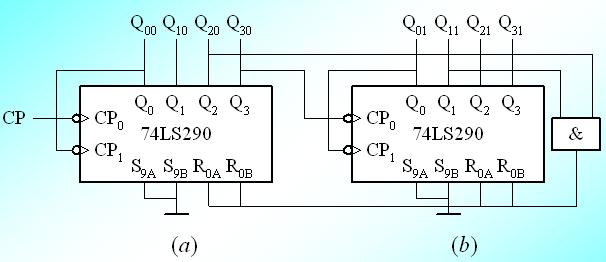

1839474ls290计数器电路大全(六种进制计数器电路)

74ls290是一个二,五,十进制计数器,本文为大家介绍由74ls290构成的各种进制计数器的电路。

2018-01-26 09:26:11 106188

106188

106188

106188

74LS290组成的十进制计数器电路图分享

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。本文为大家介绍74LS290组成的十进制计数器。

2018-01-25 14:52:47 25181

25181

25181

25181

74ls160构成24进制计数器

的CLK端,电路在计数脉冲的作用下按二进制自然序依次递增1,当个位计数到9时,输出进位信号给十位充当使能信号进位。当计数到24,这显示器个位输出0010(也就是4),显示器十位输出0010也就是2),将十位的QC、个位的QB端接一个二输入与非门,与非门输出一路送入十位计数器的清零端。

2018-01-18 15:43:05 145644

145644

145644

145644

74ls160十进制计数器

本文主要介绍了74ls160十进制计数器电路的设计与实现。74LS160是二~十进制同步可预置计数器,1脚Cr为清零端,低电平有效.2脚CP为时钟脉冲输人端,上升沿触发.3~6V脚D1一D4为数据

2018-01-18 15:14:45 182091

182091

182091

182091

74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)

本文主要介绍了74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)。74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端

2018-01-18 10:56:39 324594

324594

324594

324594

基于74LS161的60进制计数器设计方案介绍

使用两片74LS161芯片级联的形式来构成六十进制计数器,一片控制个位,为十进制;另一片控制十位,为六进制。

2018-01-17 13:58:47 52599

52599

52599

52599

74ls90设计60进制计数器

60进制计数器,由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择同步十进制计数器

2017-12-22 13:55:48 148134

148134

148134

148134

74ls160设计60进制计数器

计数器是一个用以实现计数功能的时序部件,本设计主要设备是两个74LS160同步十进制计数器,并且由200HZ,5V电源供给。作高位芯片与作低芯片位之间级联。

2017-12-21 17:23:51 224996

224996

224996

224996

基于74LS160的N进制计数器仿真设计

针对任意进制(N进制)计数器的设计目的,采用反馈复零法对基于同步十进制计数器7415160进行设计,分别采用异步清零法实现了6进制计数器和同步置数法实现7进制计数器的设计,通过应用EWB软件对所设

2017-12-21 17:08:37 60783

60783

60783

60783

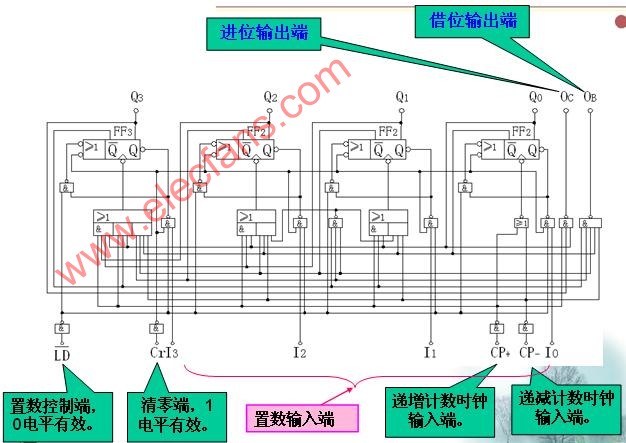

基于74LS192千进制可逆计数器的设计与研究

计数器是一个用以实现计数功能的时序部件,它主要用于时钟脉冲计数、数字系统的定时、分频和执行数字运算以及其他特定的逻辑功能,在科研、工业、农业等各个领域中具有重要的作用。本文以74LS192十进制可逆

2017-12-21 11:34:45 7718

7718

7718

7718

24进制计数器的设计

集成计数器常见的是多位二进制计数器及十进制计数器,当需要实现其它进制计数器时,通常利用现有的集成计数器进行适当的连接而构成。对于当设计要求没有限定计数器的状态编码时电路设计的灵活性问题已有文献进行

2017-11-09 16:36:16 81

81

81

81基于555定时器和Johnson计数器的CD4017十路流水灯电路的设计与制作

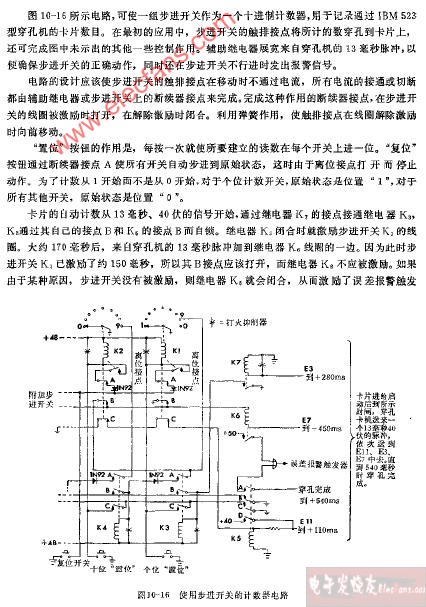

一、电路设计功能介绍 该电路主要由555构成的多谐振荡器产生脉冲提供给由4017组成的十进制移位计数器,进而控制十路LED灯,通电后,LED灯从上往下逐个点亮,直到第十个LED灯,循环往复,且移动

2017-09-07 16:29:15 58

58

58

58十进制计数器/分频器

约翰逊MC14017B是五级十进制计数器内置代码转换器。 高速运行和约翰逊spike-free输出是通过使用十进制计数器的设计。 十个解码输出通常是低,只在适当的十进制时间走高。 输出的正向变化的时钟脉冲。 这部分可用于分频应用程序以及十进制计数器或十进制译码显示应用程序。

2017-04-06 09:03:48 28

28

28

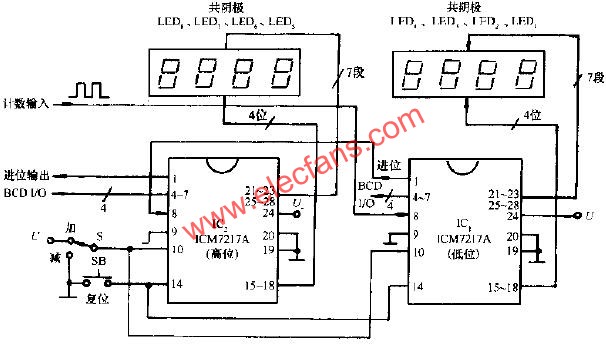

28基于8位十进抽可逆计数器电路

图中是将两片ICM7217级联后构成的8位十进抽可逆计数器电路,计数范围扩展为0~99999999.IC1是低位计数器,配LED1~LED

2010-12-10 14:12:44 2438

2438

2438

2438

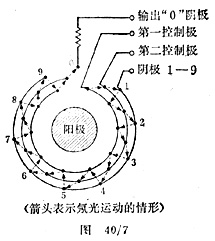

CL102十进制计数显示器的应用电路图

CL102是CMOS-LED光电组合器件,这是一种新颖的固体化数码显示器件.CL102可以完全一位数字显示的十进制计数显示器,

2010-10-20 15:19:30 2949

2949

2949

2949

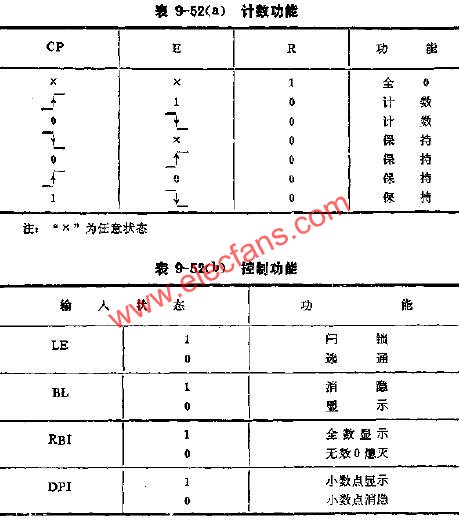

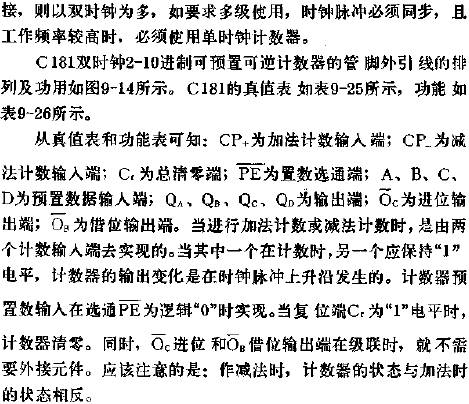

C181 2-10进制可预置可逆计数器的应用线路图

C181是双时钟2-10进制可预置可逆计数器.所谓双时钟是指计数器的加法计数时钟和减法计数时钟各有它自身的输入

2010-10-19 15:16:06 814

814

814

814

十进制计数器,十进制计数器原理是什么?

十进制计数器,十进制计数器原理是什么?

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特

2010-03-08 13:19:54 23684

23684

23684

23684十进制有权码

十进制有权码

是指表示一个十进制数位的4位基2码的每一位有确定的位权。 用得最普遍的是8421码,即4个基2码位的权从高向低分别为8、4、2和1,使用基2码

2009-10-13 17:15:44 5522

5522

5522

552224进制计数器电路

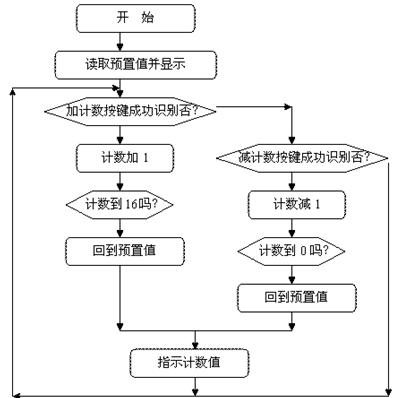

24进制计数器电路

在百进制基础上,采用反馈归零法即可组成二十四进制计数器。计数范围为0~23,24为过渡状态,当高位计数至2、低位计数至4

2009-09-16 15:50:29 19522

19522

19522

19522

十进制

十进制

好,那就让我们来看看十进制 所谓十进制就是以10为基数的计数体制,其计数规律是逢十进一。 图1.3.1展示了十进制的位号和位权之间关系的图解

2009-04-06 23:46:24 1940

1940

1940

1940

十进制计数器

十进制计数器

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特别是当二进制数的位数较多时,阅读非常困难,还

2007-06-20 13:46:05 3559

3559

3559

3559 电子发烧友App

电子发烧友App

评论