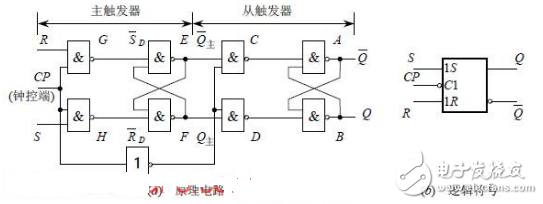

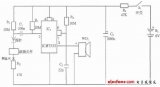

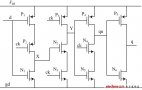

该触发器由2 个CML 结构锁存器组成, 它们构成主从型结构, 每个锁存器都要经过2 个阶段: 跟踪阶段和保持阶段。当主锁存器跟踪输入信号时, 从锁存器处于锁存保持阶段, 然后交替。其中N13 , N14 为尾电流管, 偏置电压V_bias 使N13 , N14管工作在饱和状态, 充当恒流源的作用。dp 和dn 是由输入信号d 经传输门和反相器产生的一对互补差分信号, ck_m 和ck_p 是由输入时钟信号clk 经传输门和反相器产生的一对互补时钟差分信号。主锁存器工作状态为: 当ck_m 为高电平时, N5 管导通, N6 管关闭, 此时N1 , N2 管工作在差分状态, 将输入信号dp, dn 采入。当ck_p 为高电平时,N6 管导通, N5 管关闭, 此时N3 , N4 使电路维持在锁存状态, 从锁存器工作状态恰好与主锁存器工作状态相反。设计中在触发器输出端q, qn 之间加了2 个反相器从而在q, qn 之间形成正反馈, 增强了电路的输出驱动能力。工作时, 电路的尾电流应当足够大, 有利于提高电路工作频率和输出信号的摆幅。

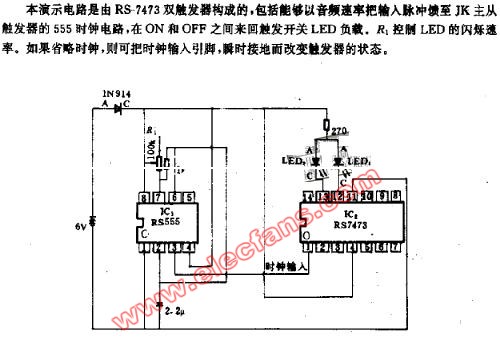

CML锁存器构成的主从式触发器电路

- 锁存器(40691)

- CML(18766)

- 触发器电路(9777)

相关推荐

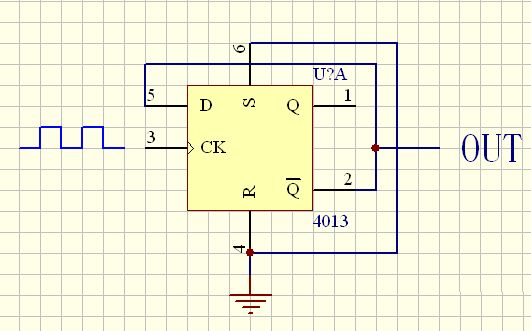

D触发器与Latch锁存器电路设计

D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 234

234

234

234

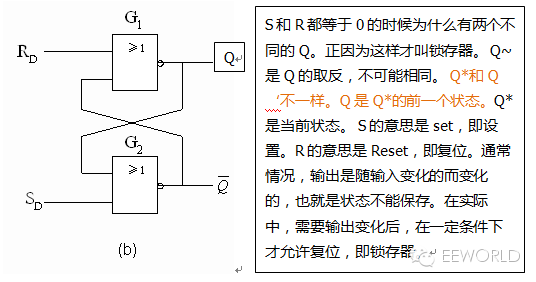

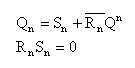

rs触发器的置位和复位指令是什么

在数字电路中,RS触发器(也称为RS锁存器)是一种基本的双稳态触发器,它可以通过特定的输入信号来实现置位(Set)和复位(Reset)操作。

2023-09-28 16:31:07 1317

1317

1317

1317rs触发器为什么不能都为1

rs触发器为什么不能都为1 RS触发器属于数字电路中的一种重要的锁存器。它由两个输入端和两个输出端组成。理论上,输入信号可以为任意值,包括1或0。但是,在实际应用中,不能让RS触发器的两个输入信号

2023-09-17 14:47:12 341

341

341

341rs触发器和rs锁存器的区别是什么

在传统的异步 RS 触发器中,当输入的 R 和 S 同时为 1 时,会引发互锁问题,输出结果是不确定的。为了避免这个问题,常常使用带有使能控制的同步触发器,如带有时钟信号的 D 触发器或 JK 触发器。这些触发器在时钟边沿上才会响应输入信号,解决了异步 RS 触发器的互锁问题。

2023-08-28 15:44:35 641

641

641

641什么是D触发器,D触发器如何工作的?

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 5258

5258

5258

5258

FPGA学习之触发器和锁存器

锁存器是构成各种时序电路的基本元件,它的特点是具有0和1两种稳定的状态,一旦状态被确定,就能自行保持,即长期存储1位的二进制码,直到有外部信号作用时才有可能改变。锁存器是一种对电平敏感的存储单元电路,它们可以在特定输入电平作用下改变状态。

2023-03-23 16:03:32 658

658

658

658

锁存器和触发器的定义和比较

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

2023-03-23 14:48:54 1357

1357

1357

1357

数字电路中的RS触发器详解

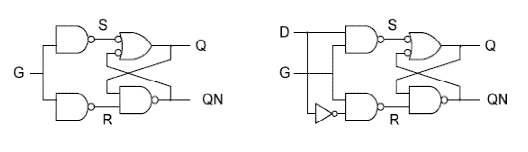

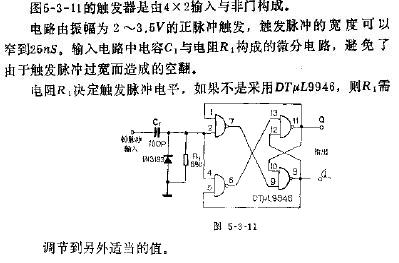

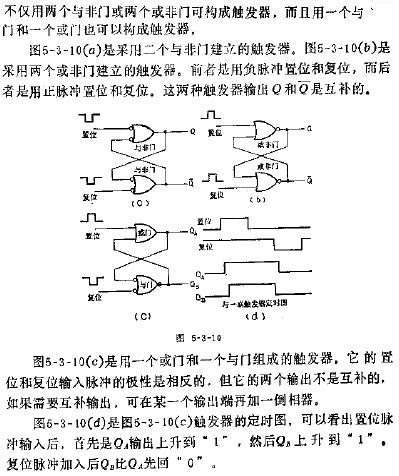

其中R、S分别是英文复位Reset和置位Set的缩写,作为最简单的一种触发器,是构成各种复杂触发器的基础。RS触发器的逻辑电路图如下图所示。

2023-02-08 09:19:45 2572

2572

2572

2572一文详细区分寄存器、锁存器和触发器

你有没有遇到过这样奇怪的事:你一直以为自己知道某件事,但当你试着向别人解释它时,你才发现自己的论述中存在漏洞和逻辑上的差异?这就是我最近所遇到的情况,当时有人问我锁存器和触发器之间的区别,以及为什么它们都与寄存器有关。

2023-01-30 15:21:15 2073

2073

2073

2073解读从CMOS到触发器 锁存器常见结构与锁存器应用

主要内容: ·双稳态器件 ·锁存器常见结构 ·锁存器的应用 ·触发器 ·触发器的建立时间和保持时间 1、双稳态器件 ** 双稳态器件**是指稳定状态有两种,一种是0,一种是1的器件;双稳态器件

2023-01-28 09:28:00 2426

2426

2426

2426

锁存器、触发器、寄存器的关联与区别及其相应的verilog描述

1:锁存器、触发器、寄存器的关联与区别 首先应该明确锁存器和触发器是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合逻辑电路的特性。 锁存

2022-12-19 12:25:01 3721

3721

3721

3721浅谈四种入门触发器

来源:罗姆半导体社区 触发器的电路图由逻辑门组合而成,其结构均由R-S锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时钟频率之间的相互影响。 在R-S锁存器的前面加一个由

2022-11-29 17:35:40 1584

1584

1584

1584rs触发器电路图与rs触发器内部电路图

rs触发器电路图与rs触发器内部电路图 rs触发器电路图 主从RS触发器电路图: 主从触发器由两级触发器构成,其中一级接收输入信号,其状态直接由输入信号决定,称为主触发器,还有一级的输入与主触发器

2022-10-19 19:16:03 16964

16964

16964

16964

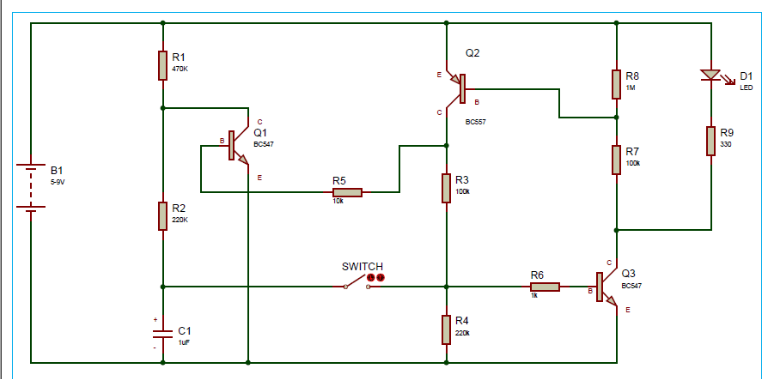

如何制作一个软锁存电路

电路中,电路只能被锁存到一种状态,并且可以改变需要移除电源的状态。通常移位寄存器和触发器用于锁存电路,就像我们在Clap-on-Clap-off 电路中使用的一样。

2022-08-25 16:32:47 2779

2779

2779

2779

FDCE/FDPE/FDRE/FDSE触发器简介

每个 Slice 有 8 个 FF 。四个可以配置为 D 型触发器或电平敏感锁存器,另外四个只能配置为 D 型触发器,但是需要记得是:当原来的四个 FF 配置为锁存器时,不能使用这四个 FF 。

2022-03-15 11:59:34 7158

7158

7158

7158基本RS触发器实验

新课第五章 触发器5.1 概述1、触发器具有“记忆”功能,它是构成时序逻辑电路的基本单元。本章首先介绍基本RS触发器的组成原理、特点和逻辑功能。然后引出能够防止“空翻”现象的主从触发器和边沿触发器。同时,较详细地讨论RS触发器、JK触发器、D触发器、T触发器、T'触发器的逻辑功能及其描述方法。

2009-04-02 11:58:41

8位CPU设计(1) 门电路和锁存器、触发器

这是一个系列文章,从最简单的门电路介绍,从基础的锁存器、触发器、编码器、译码器等一系列数字逻辑电路开始,最终构造一个简易版的CPU实物

2021-11-06 09:20:58 16

16

16

16锁存器与寄存器有哪些区别

首先应该明确锁存器和触发器也是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合电路的特性。 组合电路就是一个真值表,一个函数,一组输入对应

2021-08-12 10:26:12 3567

3567

3567

3567锁存器与触发器的区别

,锁存器有两个输入,一个是有效信号EN,一个是输入数据信号DATA_IN,有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 2)触发器 触发器(Flip-Flop,简写为FF)也叫双稳态门,又称双稳态触发器,是一种可以在两种

2020-11-29 11:02:11 20662

20662

20662

20662FPGA的设计中为什么避免使用锁存器

文章都对锁存器有个误解,我们后面会详细说明。 这篇文章,我们包含如下内容: ①锁存器、触发器和寄存器的原理和区别,为什么锁存器不好? ② 什么样的代码会产生锁存器? ③ 为什么锁存器依然存在于FPGA中? 锁存器、触发器和寄存器的原理和区别,为什么锁存器

2020-11-16 11:42:00 7206

7206

7206

7206

JK触发器逻辑符号_jk触发器的特性方程

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 79652

79652

79652

79652

如何操作基本类型的锁存器和触发器

锁存器(有时也称为S/R锁存器)是最小的存储器块。它们可以使用两个NOR逻辑门(S和R为高电平有效)或两个NAND门(输入为低电平有效)构建,并用于构建更复杂的锁存器和触发器。

2019-07-30 11:23:28 5658

5658

5658

5658

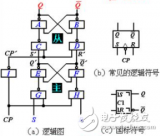

d触发器逻辑电路及符号

CP=1时,门。。打开,门。。被封锁,从触发器保持原来状态不变,D信号进入主触发器。但是要特别注意,这时主触发器只跟随而不锁存,即。。跟随D变化,D怎么变。。也随之怎么变。

2019-07-15 08:57:32 42337

42337

42337

42337

D型触发器电路真值表和计数器数的据锁存器摘要

D型触发器是一个改进的置位复位触发器,增加了一个反相器,由此可见以防止S和R输入处于相同的逻辑电平,此状态将强制两个输出都处于逻辑“1”,超越反馈锁存动作,无论哪个输入先进入逻辑电平“1”都将失去控制,而另一个仍处于逻辑“0”的输入控制锁存器的结果状态。

2019-06-26 15:36:28 14537

14537

14537

14537

锁存器Lacth & 触发器Flip-flop就是实现储存功能的两种逻辑单元电路

触发器按逻辑功能分类有D触发器、JK触发器、T触发器和SR触发器。它们的功能可用特性表、特性方程和状态图来描述。触发器的电路结构与逻辑功能没有必然联系。例如JK触发器既有主从结构也有维持阻塞或利用传输延迟结构。每一种逻辑功能的触发器都可以通过增加门电路和适当的外部连线转换为其它功能的触发器。

2019-04-12 14:04:18 7875

7875

7875

7875

数字电路教程之触发器课件的详细资料说明

本文档的主要内容详细介绍的是数字电路教程之触发器课件的详细资料说明主要内容包括了:一 SR锁存器,二 电平触发的触发器,三 脉冲触发的触发器,四 边沿触发的触发器,五 触发器的逻辑功能及其描述方法

2018-12-28 08:00:00 17

17

17

17锁存器Latch和触发器Flip-flop有何区别

本文首先介绍了锁存器Latch结构和锁存器latch的优缺点,其次介绍了触发器Flip-flop的结构与优缺点,最后介绍了锁存器Latch和触发器Flip-flop两者之间的区别。

2018-04-18 14:10:10 128942

128942

128942

128942

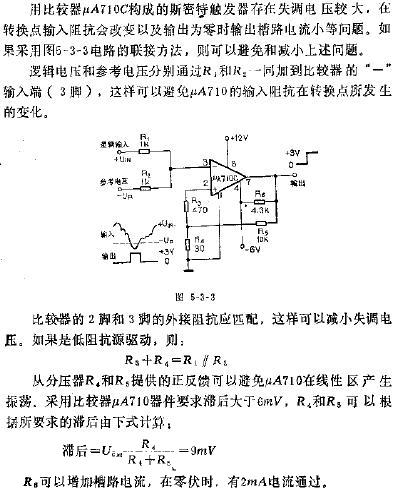

什么是单稳态触发器_单稳态触发器特点以及构成

本文开始介绍了什么是单稳态触发器以及单稳态触发器的电路组成,其次阐述了单稳态触发器特点、门电路构成的单稳态触发器、D触发器构成的单稳态触发器,最后详细的阐述了时基电路构成的单稳态触发器。

2018-03-27 09:24:23 68948

68948

68948

68948

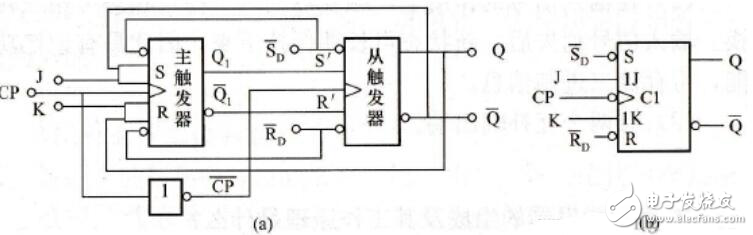

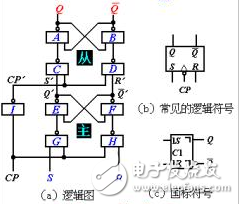

主从sr触发器基本原理分析

主从触发器的工作分两步进行。第一步,当CP由0跳变到1及CP=1期间,主触发器接收输入信号激励,状态发生变化;而主从sr触发器基本原理分析由1变为0,主从sr触发器基本原理分析=0,从触发器被封

2018-02-08 14:07:03 58179

58179

58179

58179

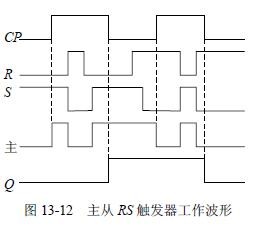

主从rs触发器特性表及特性方程

主从触发器由两级触发器构成,其中一级接收输入信号,其状态直接由输入信号决定,称为主触发器,还有一级的输入与主触发器的输出连接,其状态由主触发器的状态决定,称为从触发器。

2018-02-08 13:49:43 48291

48291

48291

48291

主从rs触发器波形图介绍

主从触发器由主触发器和从触发器组成,时钟信号CP经由非门,变成CP’控制从触发器。当CP=1时,CP‘=0,主触发器动作,从触发器被封锁;当CP=0时,CP’=1,主触发器被封锁,从触发器动作。

2018-02-08 13:40:39 19198

19198

19198

19198

d锁存器与sr锁存器的区别

锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。

2018-01-31 14:48:13 28618

28618

28618

28618

jk触发器是什么原理_jk触发器特性表和状态转换图

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2017-12-25 17:30:03 172587

172587

172587

172587

锁存器和触发器的区别

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2017-11-02 09:24:41 92855

92855

92855

92855

锁存器的主要作用有哪些?

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。典型的锁存器逻辑电路是 D 触发器电路。 PS:锁存信号(即对LE赋高电平时Data端的输入信号)。锁存,就是把信号暂存以维持某种电平状态。

2017-10-30 14:35:53 58733

58733

58733

58733

什么是触发器?锁存器和触发器的区别?

触发器的功能:

① 完成比约束更复杂的数据约束:触发器可以实现比约束更为复杂的数据约束

② 检查所做的SQL是否允许:触发器可以检查SQL所做的操作是否被允许。例如:在产品库存表里,如果

2017-08-19 12:05:00 41369

41369

41369

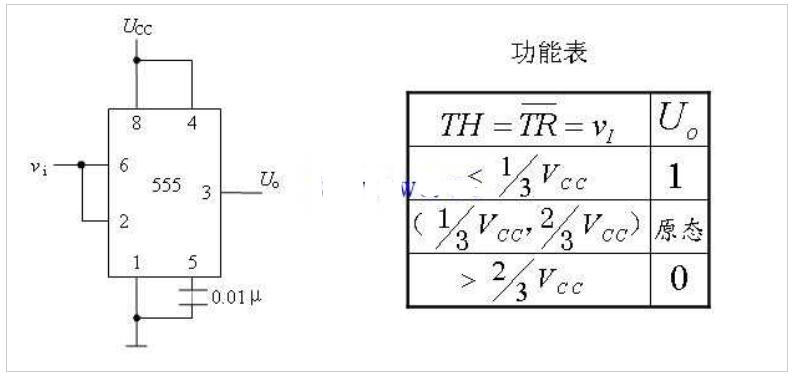

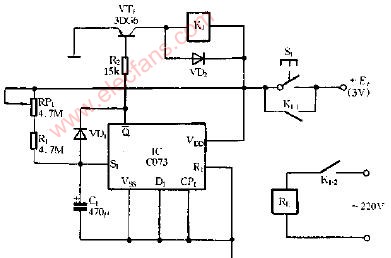

41369555定时器构成的单稳态触发器为基础的测试电路

555定时器构成的单稳态触发器为基础的测试电路根据双向导电元件的导电原理,利用555 定时器构成的单稳态触发器的触发反应,驱动蜂鸣器发声,显示测试结果。

2012-06-09 16:43:28 16200

16200

16200

16200

触发器与时序逻辑电路

一、基本要求1、理解R-S触发器、J-K触发器和D触发器的逻辑功能;2、掌握触发器构成的时序电路的分析,并了解其设计方法;3、理解计数器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57

57

57主从触发器(master-slave flip-flop)基

图13-11(a)所示为主从RS触发器原理电路。它是由两个高电平触发方式的同步RS触发器构成。其中门E、F、G、H构成主触发器,时钟信号为CP,输出为Q、

2010-08-19 09:09:10 5980

5980

5980

5980

锁存器和触发器原理

1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 233

233

233

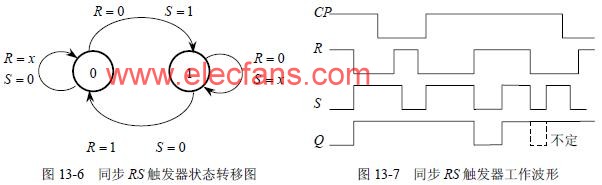

233同步RS触发器原理

由与非门构成的同步RS触发器如图13-5(a)所示,其逻辑符号如图13-5(b)所示。图中门A和B构成基本触发器,门C和E构成触发引导电路。由图13-5(a)可见,基本触发器的输

2010-08-18 09:00:00 14775

14775

14775

14775

主从触发器,主从触发器的原理和特点有哪些?

主从触发器,主从触发器的原理和特点有哪些?

1.电路组成和符号 主从RS触发器电路和逻辑符号如图Z1406所示。其中A、

2010-03-08 14:06:10 11423

11423

11423

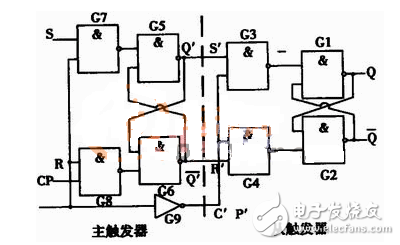

11423JK触发器原理是什么?

JK触发器原理是什么?

JK触发器是一种功能较完善,应用很广泛的双稳态触发器。图9-5(a)所示是一种典型结构的JK触发器——主从型JK触

2010-03-08 13:41:11 23241

23241

23241

23241JK触发器,JK触发器是什么意思

JK触发器,JK触发器是什么意思

1.主从JK触发器主从结构触发器也可以彻底解决直接控制,防止空翻。这里以性能优良、广泛使用的主从JK触发器为

2010-03-08 13:36:29 5842

5842

5842

5842RS触发器的芯片介绍

74LS71 与输入R—S主从触发器(带预置和清除端)

74279、74LS279、74HC279 四/R—/S锁存器双嵌位输入,图腾柱输出。

2008-01-22 12:45:32 26171

26171

26171

26171 电子发烧友App

电子发烧友App

评论