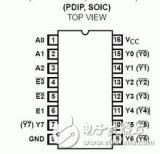

1、利用74LS138实现函数F=ABC+ABC2、利用74LS153构成一个全方位数码管组成实验电路,验证74LS48的逻辑功能3、利用74LS153构成一位全加速,要求列出其真值表,写出逻辑

2011-05-06 23:58:32

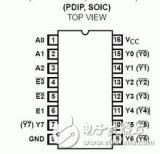

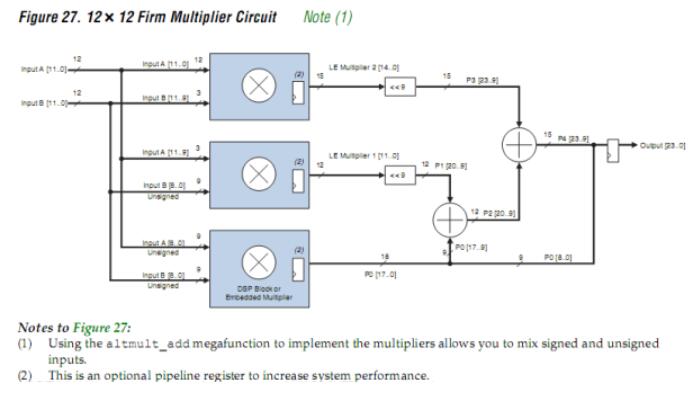

两个N位二进制数x、y的乘积用简单的方法计算就是利用移位操作来实现。

2023-06-21 09:01:57 259

259

例题:利用74LS138实现逻辑函数式Y的逻辑功能。

2023-03-23 14:38:04 8270

8270

8位同步二进制递减计数器-74HC40103

2023-03-03 19:49:59 0

0 可预置同步4位二进制计数器;同步复位-74HC_HCT163

2023-02-21 18:35:57 0

0 7级二进制纹波计数器-74HC4024_Q100

2023-02-21 18:29:31 0

0 双4位同步二进制计数器-74HC_HCT4520

2023-02-17 19:22:25 1

1 双4位同步二进制计数器-74HC_HCT4520_Q100

2023-02-17 19:22:15 0

0 可预置同步4位二进制计数器;异步复位-74HC161

2023-02-16 21:10:17 1

1 可预置同步4位二进制计数器;异步复位-74HC161_Q100

2023-02-16 21:10:00 1

1 双 4 位二进制纹波计数器-74LV393

2023-02-16 21:08:21 0

0 双 4 位二进制纹波计数器-74LV393_Q100

2023-02-16 21:08:11 0

0 可预置同步4位二进制计数器;同步复位-74LVC163

2023-02-16 20:48:19 0

0 可预置同步 4 位二进制向上/向下计数器-74HC_HCT193

2023-02-15 19:40:01 0

0 可预置同步 4 位二进制向上/向下计数器-74HC191

2023-02-15 19:39:04 0

0 可预置同步4位二进制计数器;异步复位-74LVC161

2023-02-15 19:23:09 0

0 双 4 位二进制纹波计数器-74HC_HCT393_Q100

2023-02-15 19:05:13 0

0 双 4 位二进制纹波计数器-74HC_HCT393

2023-02-15 18:58:50 0

0 74LS138译码器实现流水灯的控制。

2022-10-12 09:30:57 3614

3614 将二进制数视为元胞自动机可能有助于数字二进制计数器的设计和实现吗?

2022-07-28 11:47:10 840

840

基于8051的Proteus仿真-74LS138译码器应用

2022-05-11 17:30:25 42

42 位,52位尾数位。尾数:M是一个二进制小数,因为是二进制,所以科学计数法中这个值范围是:1≤M尾数:M是一个二进制小数,因为是二进制,所以科学计数法中这个值范围是:1≤MIEEE754对有效数字M和指数E,还有一些特别规定。1≤M<2,也就是说,M可以写成1.xxxxxx的形式,其

2021-11-26 11:21:06 50

50 P1.2、P1.1、P1.0。)把译码输出端口Y7Y0连接到L7L0八位LED电平指示输入端口,验证74LS138的逻辑译码功能。二、仿真图三、代码C语言实现:在这里插入代码片```#include

2021-11-12 14:21:00 26

26 时序逻辑方式设计的16位乘法器,乘法通过逐向移位加原理来实现,从被乘数的最低位开始,若为1,则乘数左移与上一次和相加;若为0,左移后以全零相加,直至被乘数的最高位。从而实现乘法的移位运算。

2021-06-01 09:43:56 26

26 硬件乘法器的实现本质是“移位相加”。对于二进制,乘数和被乘数的每一位非0即1,相当于乘数中的每一位分别和被乘数的每一个体位进行与运算,并产生其相应的乘积位。这些局部乘积左移一位与上次的和相加。即从

2021-02-18 16:34:45 8901

8901

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。乘法器不仅作为

2021-02-18 15:08:01 22932

22932

本文档的主要内容详细介绍的是4位二进制并行加法器的程序和工程文件免费下载。

2020-09-30 16:41:00 26

26 乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。

2019-11-28 07:06:00 2848

2848 二进制加法器是半加器和全加法器形式的运算电路,用于将两个二进制数字加在一起.

2019-06-22 10:56:38 23032

23032

VerilogHDL语言实现的两位阵列乘法器和传统的 Booth编码乘法器进行了性能比较,得出用这种混合压缩的器乘法器要比传统的4-2压缩器构成的乘法器速度提高了10%,硬件资源占用减少了1%。

2018-12-19 13:30:25 10152

10152

本文主要介绍了74ls160和74ls161区别。74ls161为四位二进制,74ls160 为2-10进制;且都为同步可预置计数器。74ls161 是4位二进制同步计数器(直接清除),74ls160 是4位十进制同步计数器(直接清除)。

2018-05-08 10:23:35 113147

113147

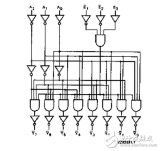

本文主要介绍了五款74ls138的应用电路图。其中包括了74ls138全加器电路、74ls138抢答器电路、74ls138实现逻辑函数、74ls138全减器电路以及与74LS20组合的三人表决器电路。

2018-05-04 10:31:55 87718

87718

二进制数据压缩算法二进制是计算技术中广泛采用的一种数制。二进制数据是用0和1两个数码来表示的数。它的基数为2,进位规则是“逢二进一”,借位规则是“借一当二”,由18世纪德国数理哲学大师莱布尼兹发现。当前的计算机系统使用的基本上是二进制系统

2018-02-28 09:31:06 18768

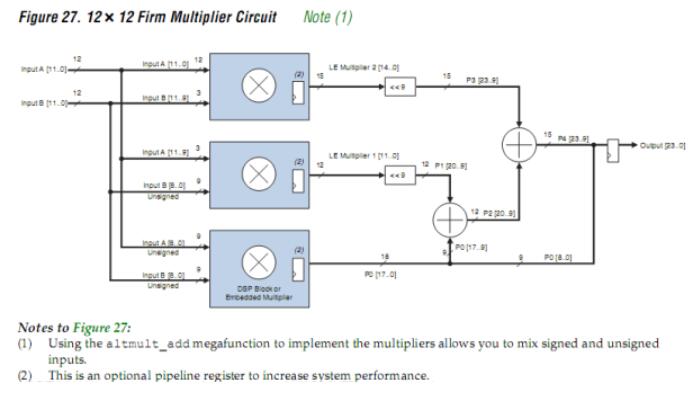

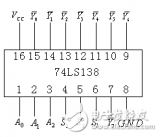

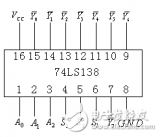

18768 74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为

2017-12-04 15:48:10 761680

761680

74LS138的单片机I/O口扩展 将2片74LS138芯片采用如上图所示的连接方式,来实现对AT89C51芯片I/O口的扩展。其中,使能端G1选择高电平,G2b选择低电

2017-11-29 19:21:48 6001

6001

基于VHDL的EDA实验---3位二进制计数器

2017-11-08 17:45:53 1

1 乘法器,求模运算部分利用Barrett约减运算,用硬件描述语言进行FPGA设计与实现,避免了除法运算。对于192位的操作数,完成Barrett模乘需要约186个时钟周期,计算速率可以达到269.17 Mb/s。

2017-11-08 15:18:19 32

32 74LS138 为3 线-8线译码器,共有 54LS138和 74LS138 两种线路结构型式。54LS138为军用,74LS138为民用。他的工作原理是一下四点。这里还给大家分享74LS138中文资料pdf完整版免费下载。

2017-11-03 15:14:08 58542

58542

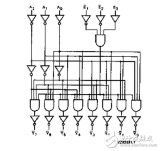

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

2017-10-31 17:15:35 218929

218929

用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理为:当一个选通端

2017-10-31 15:53:34 137363

137363

74hc138的逻辑功能和74ls138是一样的。74hc138是高速CMOS芯片,工作电源电压为2V - 6V,输出端驱动电流为正负25mA。74ls138是TTL芯片,工作电源电压为5V,输出驱动电流高电平-400微安,低电平8mA。从电源电压和驱动电流选的74hc138。

2017-10-31 11:19:57 40311

40311

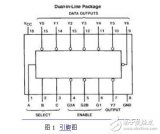

74LS138为3线-8线译码器,共有54/74S138和54/74LS138两种线路结构型式,其74LS138工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

2017-10-31 11:12:02 46

46 一个自己写的八位数的乘法器

2016-12-01 15:45:23 15

15 74LS138英文手册,感兴趣的小伙伴们可以瞧一瞧。

2016-11-22 14:35:13 14

14 74LS138 datashee—英版数据手册,感兴趣的可以看看哦。

2016-08-29 18:14:35 7

7 74LS138介绍,关于138译码器的引脚,内部结构以及其工作时的情况

2016-04-29 17:14:45 28

28 二进制加法程序【汇编版】二进制加法程序【汇编版】二进制加法程序【汇编版】二进制加法程序【汇编版】

2015-12-29 11:02:06 3

3 实验目的 1、熟悉Xilinx的ISE 软件的使用和设计流程; 2、掌握Modelsim仿真软件的使用方法; 3、用乘法运算符实现一个16*16 乘法器模块; 4、用IP核实现一个16*16 乘法器模块; 5、用例化语

2011-05-20 17:00:14 66

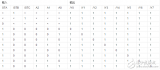

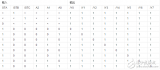

66 本资料有74ls138真值表_74ls138功能表。

2011-03-20 14:25:55 69

69 74LS138的逻辑功能

三个译码输入端(又称地址输入端)A2、A1、A0,八个译码输出端 ,以及三个控制端(又称使能端) 、 、 。

、 , 是译码器的控制输入端,当

2010-08-26 16:18:52 173

173 变跨导乘法器

这种乘法器现在已经成为一种工业上的标准方法,是应用极为广泛的优质乘法器。

2010-05-18 16:00:55 999

999

1/4平方乘法器

这种乘法器是根据数学关系设计而成的,因此称为1/4平方乘法电路,或称1/4平方乘法器。其

2010-05-18 14:08:10 1652

1652

乘法器的基本概念

乘法器是一种完成两个互不相关的模拟信号相乘作用的电子器件。理想乘法器的输出特性方程可由下式表示:

UO

2010-05-18 14:03:59 12929

12929

本的二进制加法/减法器,本的二进制加法/减法器原理

两个二进制数字Ai,Bi和一个进位输入Ci相加,产生一个和输出Si,以及一个进位输

2010-04-13 11:11:55 5077

5077 二进制电平,什么是二进制电平

在二进制数字通信系统中,每个码元或每个符号只能是“1”和“0”两个状态之一。若将每个码元可能取的状态增

2010-03-17 16:51:58 2144

2144 什么是二进制计数器,二进制计数器原理是什么?

计数器是数字系统中用得较多的基本逻辑器件。它不仅能记录输入时钟脉冲的个数,还可以实现

2010-03-08 13:16:34 29984

29984 二进制数的运算规则 二进制数之间可以执行算术运算和逻辑运算,其规则简单,容易实现。 (1) 加法运算规则 0 + 0 = 0 例如:

2009-10-13 16:24:15 21600

21600 二进制编码和二进制数据

二进制编码是计算机内使用最多的码制,它只使用两个基本符号"0"和"1",并且通过由这两个符号组成的

2009-10-13 16:22:51 4179

4179 本文在设计实现乘法器时,采用了4-2 和5-2 混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占用率;经Xilinx ISE 和Quartus II 两种集成开发环境下的综合仿真测试,与用Verilog

2009-09-17 11:13:21 27

27 12位二进制计数器

2009-09-16 15:56:08 5906

5906

74ls138译码器内部电路逻辑图功能表简单应用

74HC138:74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:

2009-07-13 12:02:52 47612

47612

二进制

二进制与十进制的区别在于数码的个数和进位规律有很大的区别,顾名思义,二进制的计数规律为逢二进一,是以2为基数的计数体制。10这个数在二进

2009-04-06 23:48:01 6966

6966

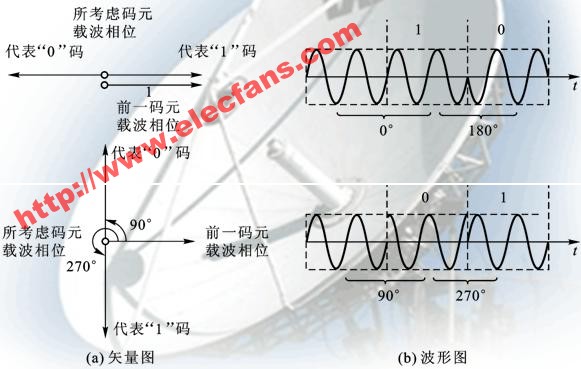

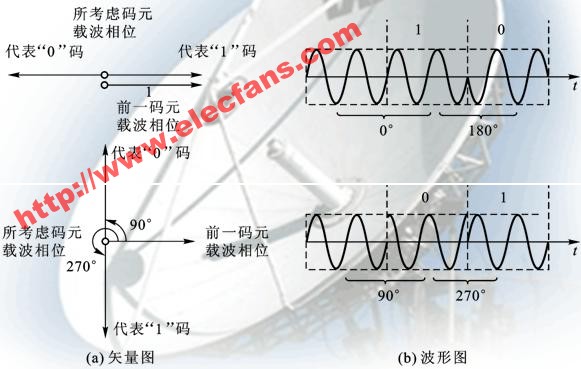

二进制相对调相(二进制差分调相2DPSK)的工作原理

2008-10-21 13:01:35 2932

2932

二进制绝对调相工作原理:二进制绝对调相(二相绝对调相)利用载波不同 位的绝对值来传递数字信息。(2BPSK)

2008-10-21 13:00:43 4898

4898

54/742854 位 x4 位并行二进制乘法器(OC,产生低位积)简要说明:54/74285 为集电极开路的 4 位 x4 位并行二进制乘法器,其主要电特性的典型值如下(具体厂家有可能不是完

2008-03-15 13:07:39 52

52 54/742844 位 x4 位并行二进制乘法器(OC,产生高位积)简要说明:54/74284 为集电极开路的 4 位 x4 位并行二进制乘法器,其主要电特性的典型值如下(具体厂家有可能不是完

2008-03-15 13:07:07 43

43 74LS274中文资料:

54/742744 位 x4 位并行二进制乘法器(3S)简要说明:54/74S274 为 4 位 x4 位并行二进制乘法器,其主要电特性的典型值如下(具体厂家有可能不是完

2008-03-15 09:17:25 48

48 74LS261中文资料:54/742612 位 x4 位并行二进制乘法器(锁存器输出)简要说明:54/74LS261 为 2 位 x4 位并行二进制乘法器,其主要电特性的典型值如下(具体厂家有可能

2008-03-15 09:14:51 40

40 74LS138中文资料

2007-12-17 22:36:13 2369

2369 74ls138引脚图

2007-12-17 22:33:25 171927

171927

4位二进制同步计数器74LS161引脚图及功能表

4位二进制同步计数器74LS161

2007-11-22 12:51:59 50388

50388

电子发烧友App

电子发烧友App

评论