关于74hc138组成16线译码器你知道多少?74hc138组成16线译码器应该怎么做呢?本文主要为你详解关于74hc138组成16线译码器过程。

74hc138介绍

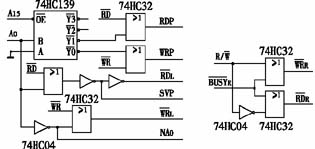

74hc138是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。74HC138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在 高性能存贮器系统中,用这种译码器可以提高译码系统的效率。将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个 低电平输出。两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。在解调器应用中,赋能输入端可用作数据输入端。

74hc138功能特性

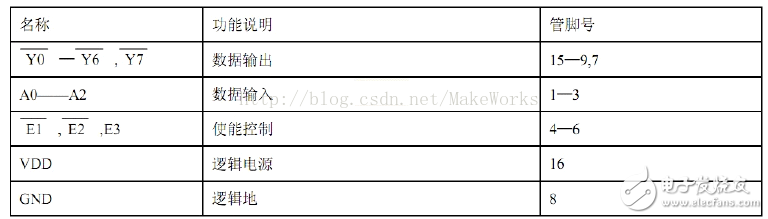

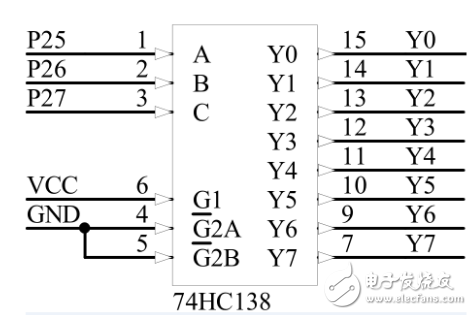

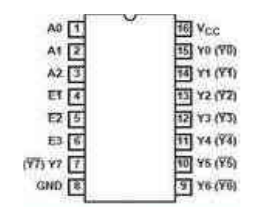

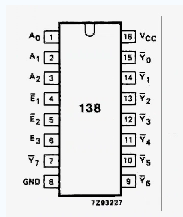

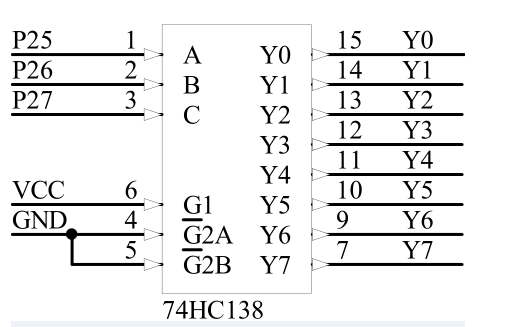

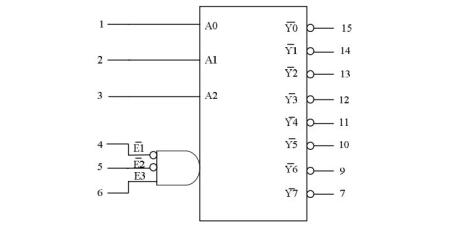

74HC138管脚说明

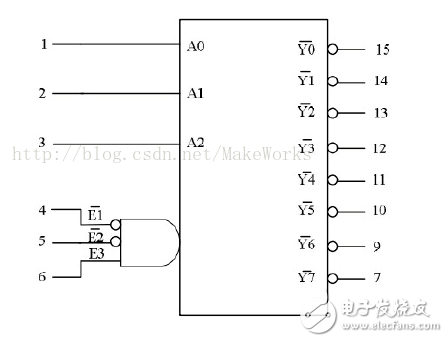

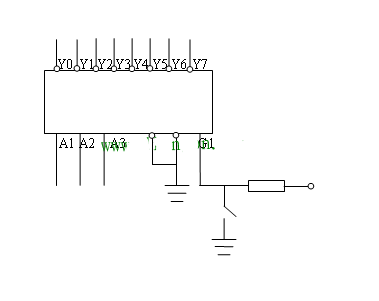

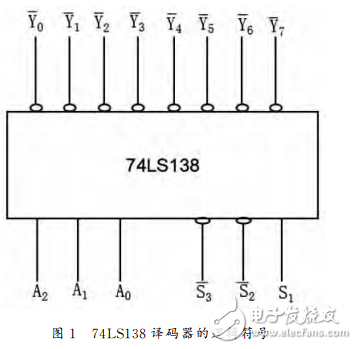

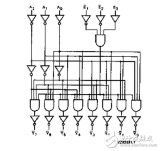

74HC138逻辑图

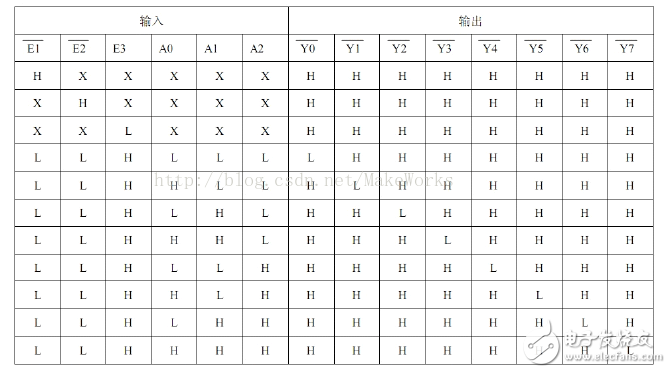

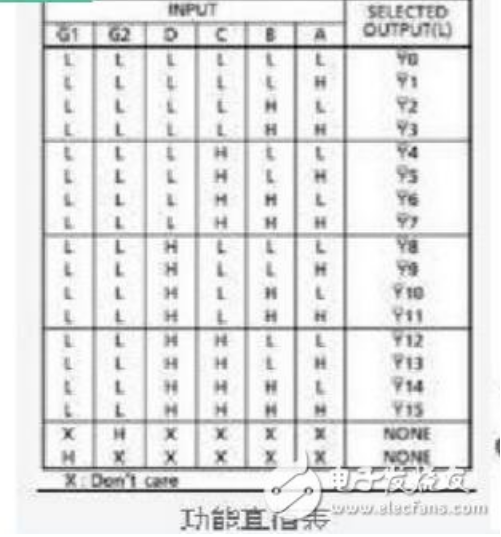

74HC138真值表

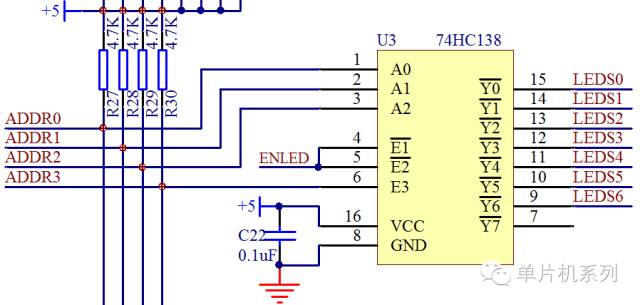

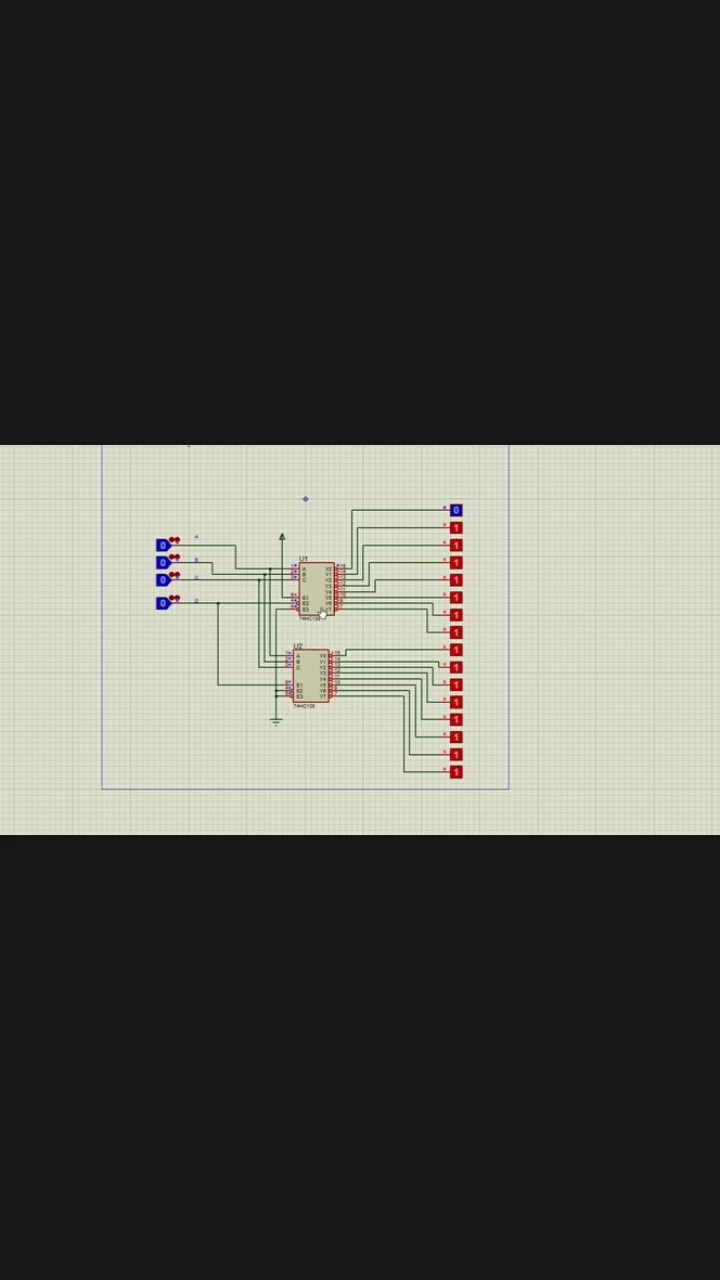

74hc138组成16线译码器的做法介绍

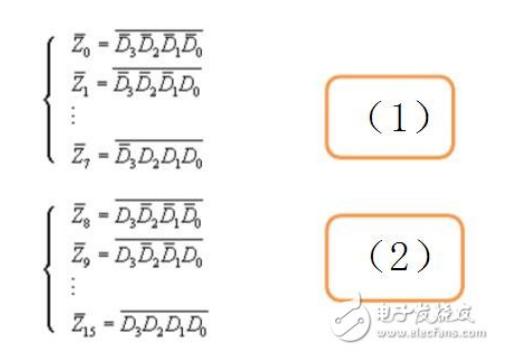

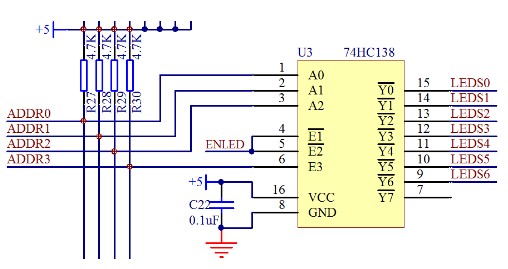

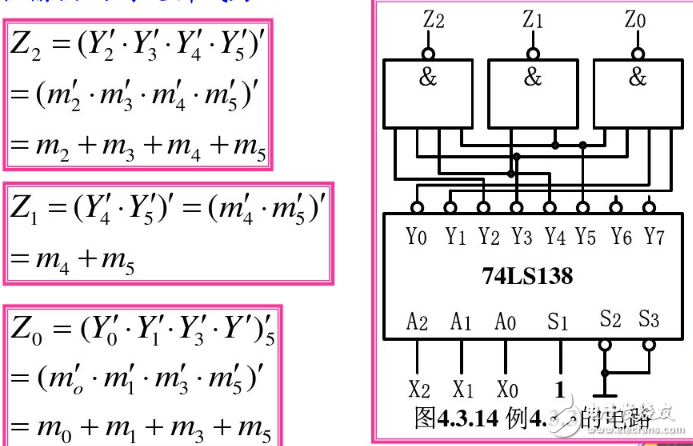

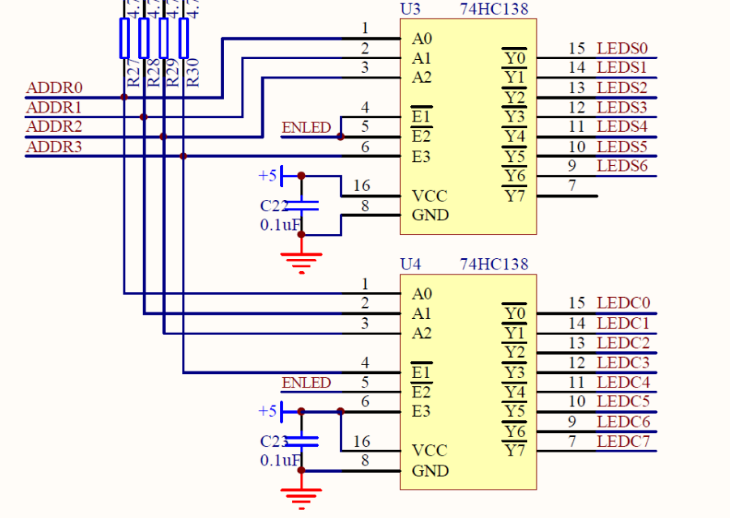

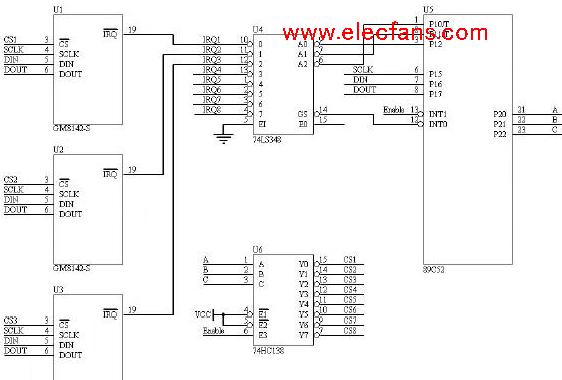

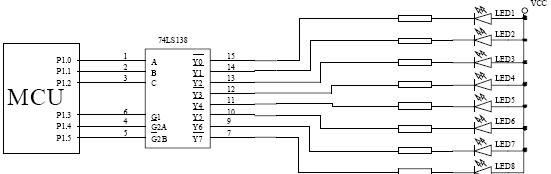

利用×138(1)的控制端S1’、S2’与×138(2)的控制电路S1相连,接入四位输入D0、D1、D2、D3的最高为A3可以完成译码器的扩展。取第(1)片74HC138的和作为它的第四个地址输入端(在同一个时间令),取第(2)片的作为它的第四个地址输入端(在同一个时间令),取两片的,并将第(1)片的和接至,将第(2)片的接至,如图2-3所示,于是得到两片74HC138的输出分别为

上图表明时第(1)片74HC138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。而式(2)表明时,第(2)片74HC138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

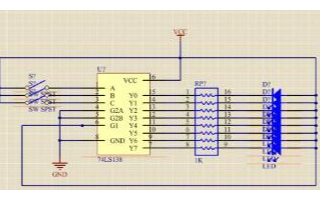

用两片74HC138组合成4/16译码器

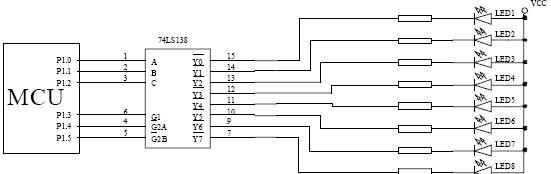

数据字节顺序,D3 D2 D1 D0,通过真值表,我们可以发现,用两片74LS138组合成4/16译码器原理关键在于D3

当D3 = 0时,(1)被选中,使能,(2)未被选中,全部输出H,也即Y8~Y15全部为H,D0~D2控制Y0~Y7的低电平输出位。1号是16位数据的低字节,2号是16位数据的高字节。高字节默认为0XFF,低字节由1号控制,显示Y0-Y7;

当D3 = 1时,(2)被选中,使能,(1)未被选中,全部输出H,也即Y0~Y7全部为H,D0~D2控制Y8~Y15的低电平输出位。1号是16位数据的低字节,2号是16位数据的高字节。低字节默认为0XFF,高字节由2号控制,显示Y8-Y15。

引脚说明

12:Gnd电源地(ground (0 V))

18-19:使能输入端(enable inputs (active LOW))

20-23地址输入端(address inputs)

24:VCC电源正(positive supply voltage)

地址/全能输入对应输出表

功能真值表注意:

H = 高电平(HIGH voltage level)

L = 低电平(LOW voltage level)

X = 任意电平(don’t care)

只要控制端G1、G2任意一个为高电平,A、B、C、D任意电平输入都无效

结语

关于74hc138组成16线译码器做法还有很多,本文只是选取一个以作代表,其它方法在本文中就不再赘述了,希望通过本文能让你对74hc138组成16线译码器有更深次的理解,如有不足之处欢迎指正。

电子发烧友App

电子发烧友App

评论