IC数据和时钟时钟线缓冲电路

- 缓冲电路(19719)

相关推荐

fpga跨时钟域通信时,慢时钟如何读取快时钟发送过来的数据?

时,由于时钟频率不同,所以可能会产生元件的不稳定情况,导致传输数据的错误。此时我们需要采取一些特殊的措施,来保证跨时钟域传输的正确性。 FPGA跨时钟域通信的基本实现方法是通过FPGA内部专门的逻辑元件进行数据传输。发送方用一个逻辑电路

2023-10-18 15:23:51 154

154

154

154时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步?

时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 53

53

53

53采用FPGA的高速时钟数据恢复电路的实现

的控制核心。但利用中低端FPGA还没有可以达到100MHz以上的时钟数据恢复电路。由于上面的原因,许多利用FPGA实现的高速通信系统中必须使用额外的专用时钟数据恢复IC,这样不仅增加了成本,而且裸露

2009-10-24 08:38:08

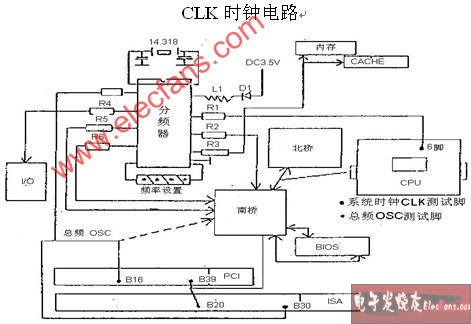

时钟电路有哪几种 时钟电路的工作原理及过程

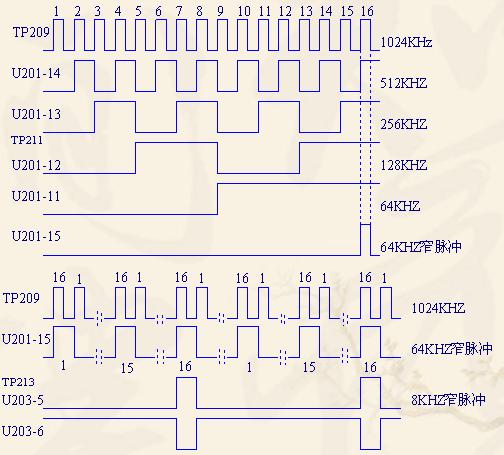

时钟分频电路通过将输入的高频时钟信号分频,生成较低频率的时钟信号。它通常基于计数器和逻辑门实现,用于将高频时钟信号分解成系统所需的各种频率。

2023-09-14 14:53:57 1076

1076

1076

1076如何抑制时钟电路产生的电磁辐射?

如何抑制时钟电路产生的电磁辐射? 在现代电子工业中,时钟电路是不可或缺的,尤其是在数字电路中,时钟电路起着控制数据流动的作用。然而,在时钟电路运行时,它会产生电磁辐射,这会对周围的设备和人体健康造成

2023-09-12 17:06:49 166

166

166

166时钟电路里的电容有什么用 时钟电路和晶振电路区别

时钟电路是一种用于产生稳定、可靠的时间基准信号的电路。它在电子系统中起着非常重要的作用,用于同步和定时系统的各种操作。时钟信号主要用于控制数据传输、指令执行、操作序列和各种时序事件。

2023-08-14 16:02:58 852

852

852

852时钟电路是晶振电路吗 时钟电路布局走线设计方法

时钟电路用于产生稳定的时钟信号,常见于数字系统、微处理器、微控制器、通信设备等。时钟信号用于同步各个电子元件的操作和数据传输,确保系统的正常运行。

2023-08-03 14:46:04 531

531

531

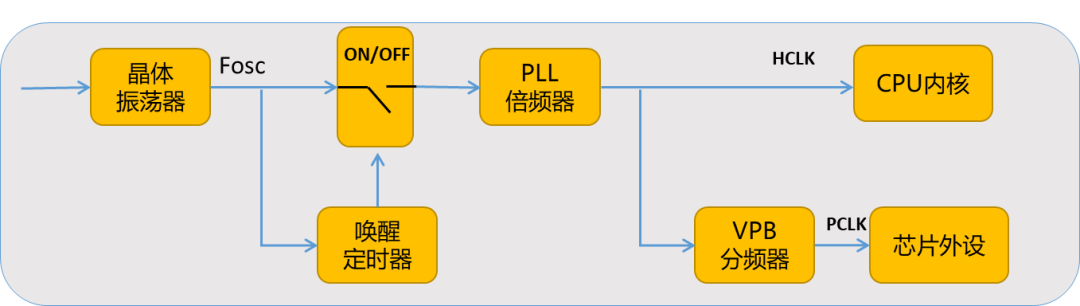

531STM32有几个时钟源 STM32系统时钟专题讲解

在数字电路中时钟是整个电路的心脏,电路的的一举一动都是根据时钟节拍下进行的,随着信息量逐渐提高,对硬件信息处理能力提出了更大的需求,时钟作为数字硬件的关键成员,其性能需要我们关注,尤其在高速电路

2023-07-27 16:12:47 779

779

779

779

为什么需要时钟门控?时钟门控终极指南

时钟门控(Clock Gating)** 是一种在数字IC设计中某些部分不需要时关闭时钟的技术。这里的“部分”可以是单个寄存器、模块、子系统甚至整个SoC。

2023-06-29 15:58:13 559

559

559

559

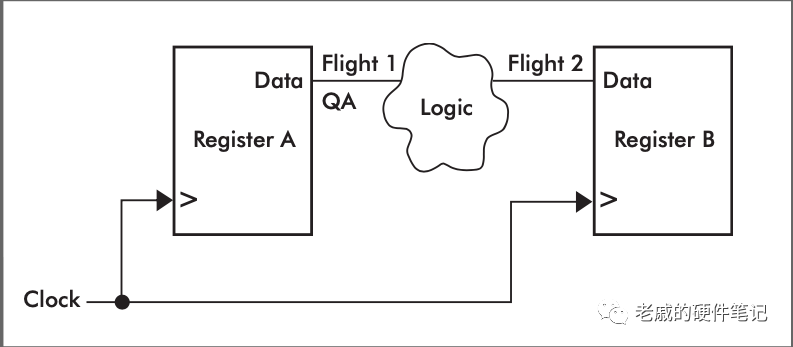

时钟同步的总线电路方案

高速数字电路模块通常以 同步 (synchronous)电路的形式实现,它们由一个或者多个时钟驱动(触发)。对于 单一时钟(域) 的同步电路而言,只要输入和时钟的关系满足 建立(setup)时间

2023-06-23 17:53:00 449

449

449

449

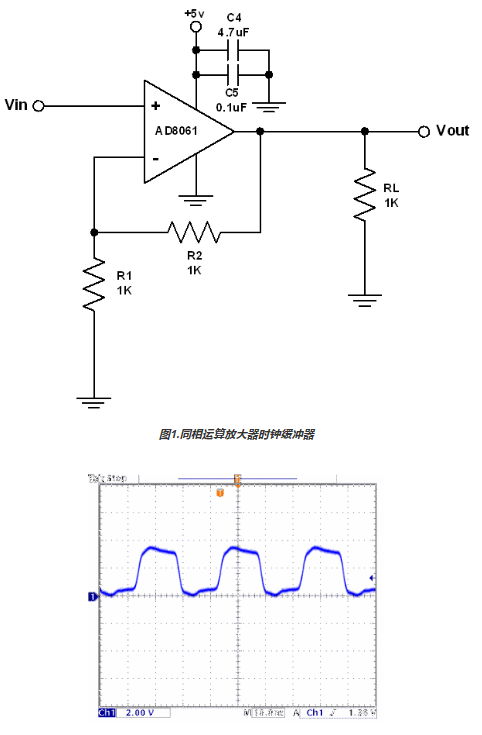

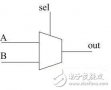

廉价的高速放大器提供灵活的时钟缓冲器

在消费电子应用中,与典型的时钟缓冲应用相比,其频率往往较低,要求也更低,廉价的高速运算放大器(~100 MHz带宽)可以为传统时钟缓冲器提供有吸引力的替代方案。高速放大器可能比传统时钟缓冲器便宜,但它们可以适应各种设计配置。

2023-06-17 17:29:14 423

423

423

423

高性能时钟缓冲器HMC7043介绍

HMC7043是一种高性能时钟缓冲器,用于为具有并行或串行(JESD204B型)接口的高速数据转换器分配超低相位噪声参考。

2023-05-31 10:47:57 844

844

844

844使用DS314xx时钟同步IC,具有1Hz输入时钟

本应用笔记介绍了ADI公司的DS314xx时钟同步IC如何进行现场升级,以接受并锁定至1Hz输入时钟信号。它还描述了在少数情况下需要1Hz时钟监控功能和系统软件支持。有了这些元件,使用DS314xx器件构建的系统就可以与1Hz和更高速输入时钟的任意组合实现符合标准的时钟同步行为。

2023-03-08 15:22:00 508

508

508

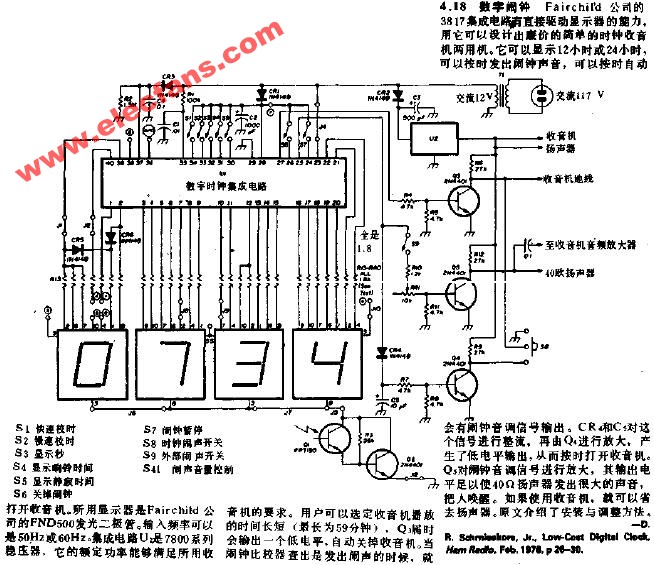

508时钟电路的原理及应用

时钟电路是一种电路,它可以产生定期的时钟信号,用于控制电子设备的运行。

它的特点是可以产生定期的时钟信号,可以控制电子设备的运行,可以提高电子设备的精度和可靠性。时钟电路的应用非常广泛,它可

2023-02-20 18:16:38 4798

4798

4798

4798使用DS314xx时钟同步IC具有1Hz输入时钟

Maxim的DS314xx系列时钟同步IC是功能强大、灵活的电信系统同步定时解决方案。这些器件最初设计用于锁定2kHz至750MHz的输入时钟频率,该频率范围可满足大多数电信系统的需求。然而,有时

2023-01-29 19:05:34 522

522

522

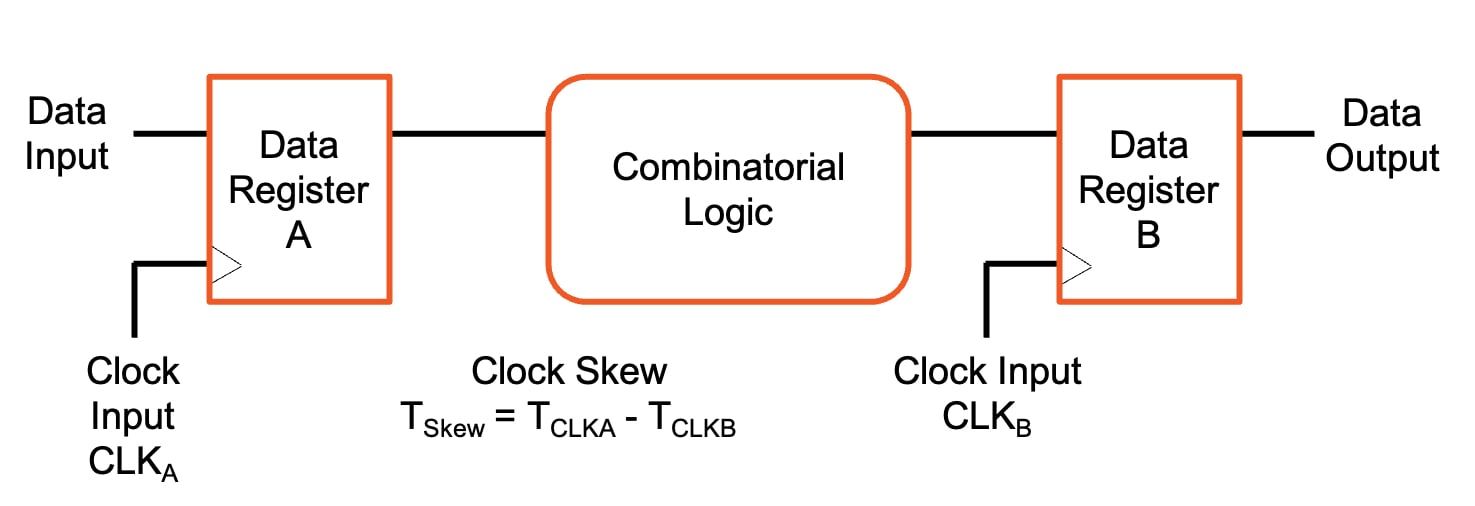

522什么是时钟偏斜?了解时钟分配网络中的时钟偏斜

通过了解同步电路、时钟传输和时钟分配网络,了解时钟偏斜、它是什么及其对现代系统的影响。 现代数字电子产品设计的最大挑战之一是满足时序限制的能力。保持可预测且组织良好的逻辑操作流的一种方法是在数字电路

2023-01-27 10:05:00 1359

1359

1359

1359

verilog的时钟分频与时钟使能

时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源时钟同相,但

2023-01-05 14:00:07 645

645

645

645Verilog电路设计之单bit跨时钟域同步和异步FIFO

FIFO用于为匹配读写速度而设置的数据缓冲buffer,当读写时钟异步时,就是异步FIFO。多bit的数据信号,并不是直接从写时钟域同步到读时钟域的。

2023-01-01 16:48:00 764

764

764

764什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

的扇出型缓冲器,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时钟缓冲器还兼具有时钟分配,格式转换和电平转换的功能。 对于需要多路时钟信号的电子系统来说,时钟源加时钟缓冲器的方案可以有效降低系统成本,简化电路设计,为系统多个组件提供多路参

2022-10-18 18:36:54 14073

14073

14073

14073

xilinx的FPGA时钟结构

HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1305

1305

1305

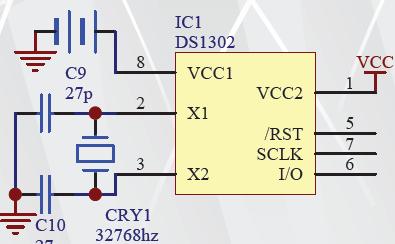

1305一个带有COB的1Hz时钟发生器电路

这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43:50 1598

1598

1598

1598

使用IDT时钟缓冲器提升应用设计

IDT 还提供另一个更简单的 CMOS 缓冲器系列,即5PB11xx系列,由五个时钟扇出缓冲器成员组成,其中最后两位数字代表输出数量。这些缓冲器是非常高性能、低抖动、低偏移和传播延迟、非常低功耗的直接 CMOS 扇出缓冲器。

2022-05-05 15:41:13 1262

1262

1262

1262

一文看懂时钟是怎么恢复的?

对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2022-02-11 15:05:26 8

8

8

851单片机时钟电路图怎么设计?这7个时钟汇聚了所有

01在MCS-51单片机片内有一个高增益的反相放大器,反相放大器的输入端为XTAL1,输出端为XTAL2,由该放大器构成的振荡电路和时钟电路一起构成了单片机的时钟方式。根据硬件电路的不同,单片机

2021-11-05 11:06:03 12

12

12

12什么是门控时钟 门控时钟降低功耗的原理

clock) 是通过在时钟路径上增加逻辑门对时钟进行控制,使电路的部分逻辑在不需要工作时停止时钟树的翻转,而并不影响原本的逻辑状态。在ASIC和FPGA设计中都存在门控时钟的概念(前者应用更广)。 典型的门控时钟逻辑如下图所示: 二、门控时钟降低功耗

2021-09-23 16:44:47 11329

11329

11329

11329

ADN2816:连续速率10 Mb/s至675 Mb/s时钟和数据恢复IC数据表

ADN2816:连续速率10 Mb/s至675 Mb/s时钟和数据恢复IC数据表

2021-05-25 09:45:45 2

2

2

2ADN2815:连续速率10 Mb/s至1.25 Gb/s时钟和数据恢复IC数据表

ADN2815:连续速率10 Mb/s至1.25 Gb/s时钟和数据恢复IC数据表

2021-05-09 14:39:25 6

6

6

6关于时钟线/数据线/地址线上串联电阻及其作用资料下载

电子发烧友网为你提供关于时钟线/数据线/地址线上串联电阻及其作用资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-13 08:54:32 26

26

26

26Xilinx 7系列中FPGA架构丰富的时钟资源介绍

是最佳的,然后通过使用适当的I/O和时钟缓冲器来访问这些时钟路由资源。该章节包括: 时钟缓冲选择考虑 时钟输入管脚 1.时钟缓冲器选择考虑 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求

2021-03-22 10:16:18 4063

4063

4063

4063

FPGA设计小技巧(时钟/性能/编程)

时钟篇 选用全局时钟缓冲区(BUFG)作为时钟输入信号,BUFG是最稳定的时钟输入源,可以避免误差。 只用一个时钟沿来寄存数据,使用时钟的两个沿是不可靠的,如果时钟沿“漂移”,就会导致时序错误

2020-12-11 10:26:44 1257

1257

1257

1257FPGA的设计中的时钟使能电路

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 4370

4370

4370

4370

在PCB设计中如何避免时钟偏斜

在 PCB 设计中,您希望时钟信号迅速到达其集成电路( IC )的目的地。但是,一种称为时钟偏斜的现象会导致时钟信号早晚到达某些 IC 。当然,这会导致各个 IC 的数据完整性不一致。 什么是时钟

2020-09-16 22:59:02 1793

1793

1793

1793ICS854105AGLFT LVCMOS LVTTL到LVDS时钟扇出缓冲区的数据手册

854105是一种低歪斜、高性能的1到4 LVCMOS/LVTTL到LVDS时钟扇出缓冲区。利用低压差分信号(LVDS),854105提供了一种低功耗、低噪声的解决方案,用于将时钟信号分布在100Ω的受控阻抗上。854105接受LVCMOS/LVTTL输入电平,并将其转换为LVDS输出电平。

2019-07-22 08:00:00 3

3

3

3关于PowerPC和Dallas的时钟芯片接口设计的方法和电路浅析

。同时在许多系统中都需要实时时钟,而应用最广泛的当数的时钟芯片。摩托罗拉的系列地址线和数据线是独立的,而的时钟芯片的地址线和数据线是复用的。本文以和为例,给出接口的设计方法和电路。因为用来实现,进步增加了通用性。

2018-12-15 09:42:54 1751

1751

1751

1751通过使用展频IC解决EMI时钟问题

的话,磁珠的阻抗又有限制,屏蔽对时钟的效果也不好。所以这时候,我们就建议客户使用我们的展频IC对主芯片的晶振进行调制。下图为加了展频后的测试数据:从近场看:(上图为客户没加展频IC之前近场探的波形

2018-11-06 14:53:48 646

646

646

646基于高速CMOS时钟的数据恢复电路设计与仿真

、16相频锁相环电路;采用电流逻辑模式前端电路构成的复用CDR环路;滤除亚稳态时钟的采样超前、滞后鉴相器;选择时钟与相位插值的控制时钟电路,以及基于折半、顺序查询算法的数字滤波电路。并对时钟进行数模混合仿真检测,测试结果表明:电路对于2.5 GB/s的差分输入数据,可快速高

2018-04-09 11:04:02 2

2

2

2基于MPC92433的高频时钟电路及串口IC接口模式的设计

提出一种高频时钟电路的设计方案。利用一款先进的可编程时钟合成器MPC92433,基于FPCJA的控制,实现4对LVDS信号输出。系统经过测试,输出时钟信号频率达到1 CHz,可以广泛应用到各种数字电路

2017-11-28 14:41:49 1

1

1

1基于FPGA的高精度同步时钟系统设计

介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议模块、发送缓冲、接收缓冲以及系统打时标等功能都在FPGA中

2017-11-17 15:57:18 5781

5781

5781

5781

时钟是怎么恢复的?

对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2017-11-16 01:01:29 20403

20403

20403

20403

单片机时钟电路

什么是时钟电路 时钟电路就是产生像时钟一样准确运动的振荡电路。任何工作都按时间顺序。用于产生这个时间的电路就是时钟电路。时钟电路一般由晶体振荡器、晶震控制芯片和电容组成。时钟电路应用十分广泛,如电脑

2017-10-16 16:45:22 26355

26355

26355

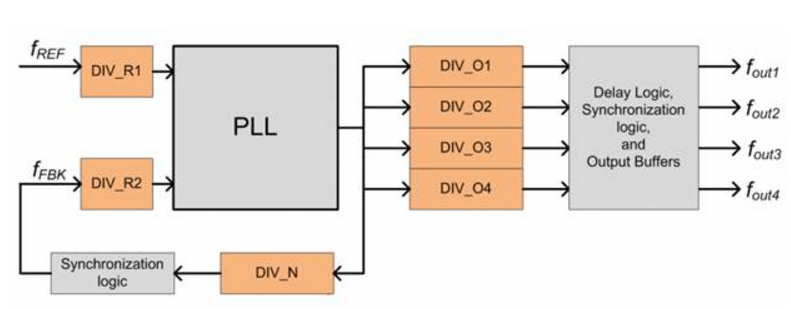

26355如何满足高性能时钟IC需求

时钟设备设计使用I2C可编程小数锁相环(PLL),可满足高性能时序需求,这样可以产生零PPM(百万分之一)合成误差的频率。高性能时钟IC具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统的子系统,例如处理器、FPGA、数据转换器等。

2017-08-30 11:04:04 4124

4124

4124

4124

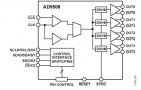

ADI发布新款时钟缓冲器和分频器IC AD9508

ADI最近发布了一款时钟缓冲器和分频器IC(集成电路)AD9508,该电路结合了高速、极低抖动(12 kHz至20 MHz频段为41 fs)及可选分频功能。

2013-02-21 11:31:00 3847

3847

3847

3847

ADI推出业界最低抖动RF时钟IC AD9525

Analog Devices, Inc. (NASDAQ: ADI) 全球领先的高性能信号处理解决方案供应商,最近推出一款具有业界最低抖动特性的 RF 时钟 IC(射频时钟集成电路)AD9525

2012-11-02 10:16:53 1087

1087

1087

1087Astro工具解决ASIC设计时钟偏斜和干扰分析

随着系统时钟频率的提高,时钟偏斜和干扰开始成为IC工程师重点考虑的问题。增大时序电路的时钟频率,减小时序电路的容差能提升未来的系统性能。低偏斜时钟缓冲器和锁相环时钟驱

2012-07-23 15:18:36 1908

1908

1908

1908

德州仪器推出超低噪声底限及附加抖动时钟缓冲器

日前,德州仪器 (TI) 宣布推出 2 款最新通用时钟缓冲器系列,进一步壮大其高性能时钟缓冲器产品阵营。CDCLVC1310 LVCMOS 时钟缓冲器可在晶振模式下实现 –169 dBc/Hz 的业界领先相位噪声

2012-04-05 08:47:28 1025

1025

1025

1025Silicon Labs扩展其PCIe时钟发生器和时钟缓冲器产品组合

Silicon Laboratories (芯科实验室有限公司)日前宣布扩展其PCI Express(PCIe)时钟发生器和时钟缓冲器产品组合。

2012-02-02 09:31:56 1356

1356

1356

1356DS314xx时钟同步IC升级工作于1Hz输入时钟

本应用笔记介绍如何对Maxim的DS314xx时钟同步IC进行现场升级,使其接受并锁定至1Hz输入时钟信号。文章探讨了少数情况下对1Hz时钟监测功能及系统软件支持的需求

2011-08-22 18:26:52 1565

1565

1565

1565Silicon新增100多款时钟IC产品

Silicon Laboratories (芯科实验室有限公司, Nasdaq: SLAB)今天宣布对时钟IC产品组合进行重要扩展,新增添了100多款时钟发生器和时钟分配器产品。

2011-05-18 09:36:59 851

851

851

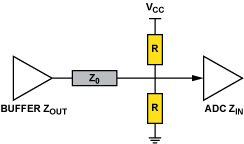

851高速转换器时钟分配器件的端接

使用时钟分配器件1或者扇出缓冲器为 ADC 和 DAC 提供时钟 时,需要考虑印刷电路板上的走线和输出端接,这是信号衰减 的两个主要来源。 时钟走线与信号摆幅 PCB 上的走线类似于低通滤

2011-03-30 15:56:14 25

25

25

25用allegro使二条时钟线等长的设计置

为了使二个SDRAM的时钟线等长,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通

2010-06-21 11:57:52 1192

1192

1192

1192

安森美时钟管理产品系列增加新的时钟和数据驱动IC

安森美时钟管理产品系列增加新的时钟和数据驱动IC

应用于绿色电子产品的首要高性能、高能效硅方案供应商安森美半导体(宣布扩充公司的时钟驱动器系列,推出NB7L

2010-02-01 13:42:09 822

822

822

822TI推出正弦至正弦波时钟缓冲器

TI推出正弦至正弦波时钟缓冲器

日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦波时钟缓冲器系列产品中的首款

2009-11-30 10:53:51 777

777

777

777基于FPGA的高速时钟数据恢复电路的实现

基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 3352

3352

3352

3352

转换器时钟技术向高速数据时钟发展

无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖

2009-07-06 18:37:55 409

409

409

409

利用Maxim时钟IC实现主备时钟卡冗余,Implement

利用Maxim时钟IC实现主备时钟卡冗余,Implement Master-Slave Timing-Card Redundancy Using Maxim Timing ICs

Abstract: Telecom equipment with SONET/SDH or Synchr

2009-06-27 23:35:58 693

693

693

693

电子发烧友App

电子发烧友App

评论