TOP7 麦克风阵列信号采集系统的设计

作为传统的语音拾取工具,单个孤立麦克风在噪声处理、声源定位和跟踪,语音提取和分离等方面存在不足,严重影响了语音通信质量。如果使用多个麦克风组成阵列,在时频域的基础上增加一个空间域,对来自空间不同方向的信号进行实时处理,就可以弥补上述不足。现在已有的麦克风阵列采集处理系统中,大多采用4路麦克风阵列,这类系统虽然在一定程度上能解决语音增强、噪音抑制、声源定位和回声抵消等问题,但由于4个麦克风个数较少,只能组成一字线阵,十字阵等几种特定的阵列形状,三维空间的方向及距离判断有较大的误差。设计的16通道麦克风采集系统能够组成麦克风面阵,弥补了上述不足,较好地解决了三维空间信号位置判断的问题。

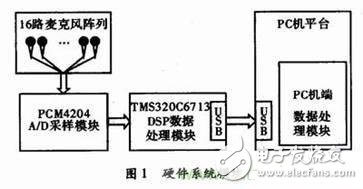

一、硬件系统设计

该硬件系统主要包括16路麦克风构成的阵列、A/D采样模块、DSP数据处理模块、PC机,如图1所示。

1.1 麦克风阵列

该系统中,麦克风阵列选用声望公司的MPA416传声器。MPA416传声器的灵敏度可达50 mV/Pa;拥有低本底噪声;频率响应范围20 Hz~20 kHz;当其用于阵列时,MPA416的相位差能控制在3°~5°,能满足系统对精确度和稳定性的要求。

1.2 A/D采样模块

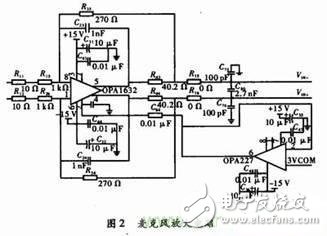

A/D采样模块由4片PCM4204以及其外围电路组成。PCM4204内置了4个同步采样通道,支持音频串口和DSD数据口。音频串口模式时,输出24 位线性PCM码,有主、被动两种工作模式,支持左、右对齐,I2S和TDM数据格式,动态范围为118 dB,最高采样频率216 kHz。系统选用1片PCM4204采用主动工作模式,其余3片PCM4204采用被动工作模式。通过音频串口将外部采集的模拟声音信号转化为24位 I2S格式数字信号。由于前端麦克风阵列的输出信号不是差分信号,而PCM4204要求输入信号为差分信号,同时要求输入差分信号幅值在-0.3~- 0.3+VccV之间,因此其每路信号的前端都应有一个缓冲电路,用来将所接收的麦克风信号转换为差分信号并对幅值进行调整。缓冲电路主要由 OPA1632和OPA22组成,OPA1632和OPA227是高精度、音频差分放大器,缓冲电路如图2所示。

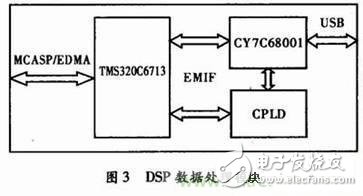

1.3 DSP数据处理模块

设计中数据处理模块选择TI公司浮点DSP芯片TMS320C6713作为模块核心。TMS320C6713为高性能32位浮点DSP,适用于专业音频信号处理,其主频可达300 MHz,处理速度高达2 400 MIPS/1 800 MFLOPS。其内部采用改进的哈佛结构;具有256 kB的片内存储空间;丰富的外设包括两个多通道缓冲串口(McBSP)、两个多通道音频串口(McASP)、SPI和I2C等;增强的直接存储器访问 (EDMA)控制器,可控制16个独立通道完成不受CPU干预的数据传输;32 bit的外部存储器接口(EMIF),能与SRAM、ERPOM、Flash、SBSRAM和SDRAM无缝连接。DSP数据处理模块框图如图3所示。 其中,TMS320C6713通过McASP与前端的A/D采样模块相连,并利用EDMA数据传输速度快、传输量大,且不占用CPU时钟周期的特点,将采集数据转存至TMS320C6713的片内存储空间。TMS320C6713外接CPLD控制EMIF接口,通过对EMIF接口上CE3空间的控制,控制 USB芯片CY7C680 01,完成TMS320C6713与PC机平台间的USB数据传输。

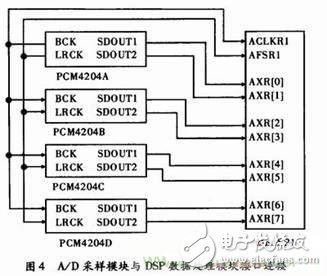

1.4 A/D采样模块与DSP数据处理模块接口设计

4片PCM4204芯片与TMS320C6713的McASP1相连接,其连接示意图如图4所示。

图4中,PCM4204 A采用主动工作模式,PCM4204B、PCM4204C和PCM4204D采用被动工作模式。系统采用I2S数据格式,PCM4204A的SDOUT1 输出的是1和2通道的数据,SDOUT2输出的是3和4通道的数据;PCM4204B的SDOUT1输出的是5和6通道的数据,SDOUT2输出的是7和 8通道的数据;PCM4204C的SDOUT1输出的是9和10通道的数据,SDOUT2输出的是11和12通道的数据;PCM4204D的SDOUT1 输出的是13和14通道的数据,SDOUT2输出的是15和16通道的数据。

通过配置芯片引脚S/M、FMT2、FMT1、FMT0、FS2、FS1和:FS0对PCM4204进行设置。

1.5 DSP数据处理模块USB接口设计

TMS320C6713通过EMIF的CE3存储空间可以外扩USB2.0接口,因此在对外扩USB进行读/写访问前,需要通过EMIF的 CE3控制寄存器CE3C-TL来配置CE3空间存储器接口的类型、存储器宽度及读写时序。CY7C68001采用并行异步存储器接口通过可编程逻辑芯片 CPLD与TMS320C6713相连,其原理框图如图5所示。

CY7C68001除了存储器接口外,还有1个中断信号![]() 和4个状态信号

和4个状态信号![]() 。中断信号 采用TMS320C6713的外部中断EXT_INT6。TMS320C6713使用CY7C68001作为从设备。在这种模式下,DSP可以像读/写普通FIFO一样对CY7C68001内部的FIFO进行读/写。PC主机发出命令的同时也由CY7C68001 的引脚提供中断触发信号给DSP的EXT_INT6。其上升沿被检测到后,DSP就进入相应中断服务程序,开始处理USB的传输。DSP通过 EA[4:2]连接FIFOA[2:0]对CY7C68001内部FIFO或命令口进行选择。读/写数据通过ED[15:0]与FIFO[15:0]连接进行。FIFO和命令口的选择和地址分配如表1所示。

。中断信号 采用TMS320C6713的外部中断EXT_INT6。TMS320C6713使用CY7C68001作为从设备。在这种模式下,DSP可以像读/写普通FIFO一样对CY7C68001内部的FIFO进行读/写。PC主机发出命令的同时也由CY7C68001 的引脚提供中断触发信号给DSP的EXT_INT6。其上升沿被检测到后,DSP就进入相应中断服务程序,开始处理USB的传输。DSP通过 EA[4:2]连接FIFOA[2:0]对CY7C68001内部FIFO或命令口进行选择。读/写数据通过ED[15:0]与FIFO[15:0]连接进行。FIFO和命令口的选择和地址分配如表1所示。

经实验验证,USB异步传输速率可达3 Mbit•s-1,满足系统需求。

1.6 PC机平台

DSP数据处理模块通过USB接口与PC机相连,通过CY7C68001芯片,将前端采集的数据传输到PC机,方便对数据的进一步处理。

二、 程序设计

2.1 McASP接口程序设计

定义了4个寄存器组:全局寄存器组globalRegs、发送寄存器组xmtRegs、接收寄存器组mvRegs和串行化器控制寄存器组 srctlRegs。通过这4个寄存器组,对McASP1的PFUNC,PDIR,SRCTL,RFMT,AFSRCTL,ACLKRCTL及 AHCLKRCTL等寄存器进行设置。各寄存器组所包含的主要寄存器情况如表2所示。

依据PCM4204的I2S数据格式,将接收帧同步信号的宽度定为32 bit,接收延迟设置为1个delay;AXR[0]~AXR[7]设置为接收模式。

2.2 EDMA传输程序设计

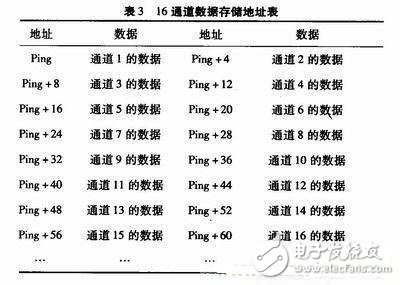

为保证数据的完整性,选用Ping-Pong模式对EDMA传输进行配置,Ping缓存存放如表3所示,Pong缓存与Ping缓存结构相同。

依据Ping、Pong缓存数据格式,对EDMA接收进行配置,即对:EDMA的opt,src,cnt,dst,idx,及rld寄存器分别进行设置。通过opt寄存器设置数据长度为32 bit,源数据和目的数据为一维方式,源地址固定,目的地址采用索引,启用帧同步等。源地址和目的地址分别写入src,dst寄存器。cnt寄存器主要用于配置帧计数和单元计数。由于采用I2S的数据格式,所以1帧数据只包含2个单元数据。通过配置idex及rld寄存器,目的数据可以按照设定的索引方式存储。

2.3 DSP端OSB接口程序设计

首先,通过调用用户的初始化函数,使能外部中断并初始化USB寄存器。之后,程序通过数据传输函数,完成DSP与PC机的数据传输。

USB初始化程序配置如下:

(1)使能外部中断6(EXT_INT6)。

(2)加载USB描述表,并进行自举检测,如自举不成功,则重新自举,直到端点0收到设置包为止。

(3)配置USB为异步从FIFO(Asynchronous SlaveFIFO)模式,采用内部48 MHz时钟源。

(4)读取FNADDR寄存器,判断USB工作状态。

(5)依据USB工作状态,配置EP2、EP4、EP6、EP8,并设置一次传送的Byte长度。设置EP2、EP4为BULK OUT,EP6、EP8为BULK IN,其缓冲大小分别为2×512 Byte。

在数据传输过程中,PC端通过EP2向DSP发送读数据命令,DSP通过外部中断收到读命令后,使用EP6发送已采集好的数据。在声音数据采集系统中,每路麦克风以96 kHz进行24位采样,按照ping-pong方式进行存储。在传输过程中还需进行判断,当采集数据存储在ping缓存时,发送pong缓存中的数据,当采集数据存储在pong缓存时,发送ping缓存的数据。由于TMS320C6713通过EMIF的CE3存储空间可以外扩USB2.0接口,需对 EMIF接口的CE3寄存器进行配置,将USB接口设为16位异步存储接口,设定读/写的建立时间(Setup)、促发时间(Strobe)、保持时间,使其满足CY7C68001的读/写时序要求。

2.4 PC机平台应用程序设计

PC端接口程序采用VC++6.0编写,首先调用OpenDriver()打开USB接口设备,获得设备的句柄hDevice,之后调用 Sx2SendVendorReq()函数向外设发出命令,读取USB配置,最后调用Sx2BulkdataTrans()进行数据传输,通过调用 CFile类将接收到的数据存放在文本文件中。程序使用多线程技术,使得应用程序将USB数据传输在后台进行处理,应用程序前台还可进行其他操作。

电子发烧友App

电子发烧友App

评论