摘要: 针对目前2 × 1 Gbit /s 网络LED 显示屏控制器带宽偏低的不足,提出了一种基于10 Gbit /s 以太网IEEE 802. 3an 标准,采用双绞线作为传输媒质,传输距离达到100 m 的超高清LED 显示屏单卡网线控制系统的设计方案。音视频采用HDMI 1. 4a /DVI 双输入,通讯采用10 GbE LAN/WAN PHY,信息处理采用了具有XAUI /SGMII 接口的中高档现场可编程门阵列( FPGA) ,屏体显示分配采用了千兆网矩阵分流技术,从而实现单卡控制的LED 显示屏4K2K、3D 显示和音频同步播放。

引言

目前,多家公司相继推出4K2K( 物理分辨率3840 × 2160 或4096 × 2160) 高端显卡、超高清电视、裸眼3D 电视和投影机。无论是水平方向还是垂直方向,4K2K 规格都是现有主流全高清显示设备1920 × 1080p 分辨率的2 倍,总像素数量达到了800万以上,是全高清的4 倍。而在LED 全彩显示领域,尤其在舞台背景屏和广场广告屏的应用中,因其具有无限拼接特点,超过4K2K 的高档LED 显示屏和3DLED 显示屏早已问世。然而,当前市场主流LED 显示屏控制系统近距离主要为DVI 输入双口千兆网模式,远距离为单通道1 - 3. 125Gbit /s 光纤通讯模式,8 位色阶输入时单板支持的最大分辨率仅能达到1280 × 1024( 60 Hz,无压缩) 。若要支持超高分辨率显示或30 位色阶以上输出,必须采用多卡或多控制器系统,并搭配昂贵的视频分割拼接器才能实现。显然,当前的LED 显示屏控制系统,尤其是沿用多年无变化的近距离双口千兆网控制系统,已滞后于视频和通信技术的发展,满足不了市场和用户的更高需求。为此,在研制前一代双口千兆网LED 控制器的基础上,设计了一种HDMI /DVI 双输入超高清LED 显示屏单卡网线控制系统,大幅度提升了传统LED 显示屏控制器的带宽、功能和性价比。

1 总体设计

超高清LED 显示屏单卡网线控制系统包括发送和接收两部分,图1 所示为发送器控制逻辑设计,包括HDMI 输入口、DVI 输入口、USB 接口、ADV7619、CP2102、FPGA、DDR、FLASH、PCIe 插口、外设和高速通讯逻辑。

图1 发送器逻辑设计示意图

图2 所示为接收器控制逻辑设计,包括高速通讯逻辑、FPGA、3 × 4 口1Gbit /s PHY、12 × 集成RJ45插座、DDR、FLASH、音频输出和外部设备,其中高速通讯逻辑和发送器完全相同。

图2 接收器逻辑设计示意图。

2 模块设计

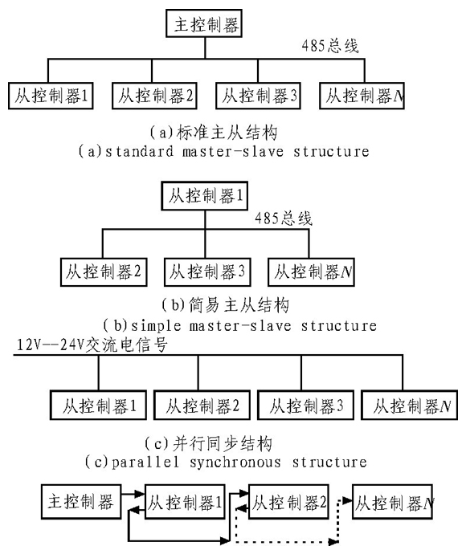

提高双口千兆网LED 控制器性能关键有3 点,一是输入支持HDMI 1. 4a; 二是实现高带宽通讯; 三是多路接收分配输出。

2. 1 发送器

2. 1. 1 音视频输入

音视频输入解码芯片采用HDMI /DVI 双输入ADV7619 芯片代替传统方案中的单视频DVI 芯片。

ADV7619 是AMD 公司的一款高质量多路复用高清多媒体接口( HDMI○R) 接收器,内部逻辑设计见参考文献[1].ADV7619 TMDS 时钟频率最高达297MHz,支持HDMI 1. 4a 规范规定的所有强制性和附加3D 电视格式,包括36 位色深1920 × 1080p 高清电视、4k × 2k( 3840 × 2160 @ 24 Hz /25 Hz /30Hz 以及4096 × 2160@ 24 Hz) 超高清和3D 电影视频播放,支持数字摄像机的色彩空间sYCC601、Adobe RGB 和Adobe YCC601,支持HBR 和DSD S /PDIF 多种数字音频格式。ADV7619 的音视频解码直接输出到FPGA.

2. 1. 2 高速通讯逻辑

超高分辨率LED 显示屏单卡控制系统10 Gbit /s 高速通信的构建基于10 Gbit /s 以太网技术,尤其是10 Gbit /s 以太网物理接口的发展。10 Gbit /s 以太网IEEE 802. 3an 定义了基于双绞线作为媒质的10 Gbit /s以太网标准,传输距离至少100 m.

图3 所示为近距离10 Gbit /s 网线通讯部分的逻辑设计,包括FPGA、10GBASE-T PHY、RJ45 插座和10GbE( 10 Gigabit Ethernet) 变压器Transformer,FPGA 和10GBASE-T PHY 的数据通道采用10GE 连接单元接口XAUI ( 10 Gbit /s Ethernet AttachmentUnit Interface) ,具有4 路3. 125 Gbit /s 高速并行通道。

图3 10Gbit /s 网线通讯部分的逻辑设计示意图。

1) 支持100 m 网线传输方案的关键器件是10GBASE-T PHY.其一可采用Aquantia 公司40 nmCMOS 工艺21 mm 400-pin BGA 封装的AQ1103 单口100 / 1000 /10GBASE-T PHY,其内部逻辑设计见文献[2 ].AQ1103 是一个单端口低功耗( 4 W)10G/1G/100M 全适应PHY,符合IEEE○R802. 30-2008 标准并执行所有的物理层功能,它采用一种创新的单片设计架构,适合低功耗单端口、多端口网卡和交换机应用。其二可采用Solarflare 公司推出的10GBASE-T 单口PHY 10Xpress SFT9001.SFT9001具有XAUI、XFI、SGMII ( serial gigabit mediaindependent interface) 、MAC 和MDI 界面,完全遵守10GbE 标准( IEEE 8020-3an0-2006 ) .AQ1103 和图4 Altera 带XAUI FPGA 10GbE 参考设计SFT9001 都具有以下特点:

a) 低功耗,4 ~ 6 W/100 m;b) 6A 类网线传输超过100 m 时,误码率小于10 - 10 ~ 10 - 12 ;c) 三速率自动连接,支持10G/1G/100M 网;d) 先进的电缆诊断,可轻松连接调试;e) 局域网唤醒支持( WOL) ;f) 高性能的XAUI 接口,易和FPGA 对接;g) 全规格性能,传输距离支持6A 类线100 m以上,6类线可达55 m,CAT5e 线可达45 m;h) 传统RJ45 铜缆,提供10GBASE-T 传输,无SFP + 光纤模式的高成本和复杂性。

2) 10 Gbit /s 网络变压器

10 Gbit /s 网络变压器可采用上海元册科技的30FB0-10GANL 和***盟登科技的UC0-3074SG,两款结构外形相同,24 脚标准封装。30FB0-10GANL技术资料见文献[3]。

3) RJ45

RJ45 插座采用内部带变压器和LED 指示灯的集成RJ45。

2. 1. 3 FPGA 信息处理

大规模可编程芯片FPGA 是超高分辨率LED显示屏控制系统设计的核心,所有信息,包括高清音视频接收、缓存、转换、输出、控制信号嵌入、状态显示、DDR、FLASH 和外部设备管理等均由FPGA 进行处理。与传统的LED 显示屏控制系统设计比较,其最大不同在于10 Gbit /s 通讯。目前Altera、Xilinx、Lattice 等主流FPGA 制造商都能提供用于10GbE 通讯的FPGA 芯片,例如,Altera 的Stratix V( GX、GS 和GT) 、Stratix IV ( GX 和GT) 、Cyclone IVGX( F23 和更大器件) ,Stratix II GX、Arria 系列和HardCopy IV GX ASIC 器件都带有内置收发器,为XAUI 接口的实现提供专用模式。XAUI 收发器模块提供156. 25 MHz 输入参考时钟和并行接口,带有4 通道时钟数据恢复( CDR) 接收器和4 通道收发器阵列以及交流耦合差分接口和差分PCML 驱动电路。收发器模块嵌入了专用速率匹配和时钟补偿FIFO 缓冲,还采用了1∶ 16串化器/解串器( SerDes) 、16∶ 20变速箱、8B /10B 编码和字对齐功能,所有这些功能都由专用XAUI 状态机进行控制。每组四通道还内置了通道对齐电路,以减小XAUI 接口从XAUI源到宿的偏移。收发器可提供500% 的预加重和高达17 dB 的均衡,以补偿高频损耗。Altera 的以上器件均符合所有的IEEE 802. 3ae 规范,包括没有预加重时小于0. 35 单位间隔( UI) 的抖动发生和最大峰峰值大于0. 60 UI 的抖动容限。收发器模块符合IEEE 802. 3 正弦抖动容限模板要求。万兆以太网3. 1250-Gbit /s × 4 通道单向数据传送速率符合IEEE 802. 3ae XAUI 对物理层器件和上层器件链接的定义。

图4 所示为带XAUI 接口,并集成了物理编码子层PCS ( physical coding sublayer) 、万兆以太网MAC、物理媒体附属子层PMA ( Physical MediumAttachment) 的FPGA 内部逻辑结构图,它通过XAUI接口和各种10GbE PHY 器件( 例如AQ1103) 相连。

当然,FPGA 也可以通过XGM II 320-b @ 312. 5Mbit /s 并行总线接口和10GbE PHY 器件相连,但I /O 数太多,不建议采用。FPGA 设备的配置和与系统数据的接口采用Avalon 总线,对10GbE PHY 的管理采用I2C 总线。至于FPGA 内部的万兆以太网MAC,因LED 显示屏本身不是局域网终端,属于点对点高速通讯,与传统LED 千兆网控制系统一样,无需遵从万兆以太网协议,可不采用,而大大简化设计。FPGA 具体的软件设计可从网上参考或下载Altera 公司的万兆以太网用户手册。

图4 Altera 带XAUI FPGA 10GbE 参考设计

2. 1. 4 CP2102

通过计算机远程配置和控制LED 显示屏是必备功能,本设计采用Silicon Labs 公司的USB 转UART 桥接芯片CP2102[5]代替传统的RS0-232 口实现PC 和FPGA 通讯。CP2102 包含USB2. 0 全速功能控制器、USB 收发器、振荡器和带有全部调制解调器控制信号的异步串行数据总线( UART) ,可通过USB 供电。CP2102 工作时作为一个虚拟COM口使用,且满足RS0-232 总线的波特率要求。

2. 1. 5 其他

1) DDR

存储器采用高速双倍速率同步动态随机存储器DDRII 代替传统LED 控制器的SDRAM 存储器,用于缓存超高清视频数据流。例如采用两片ISSI 公司的IS43DR32800A 8M × 32 256Mbit 芯片,或三星的2M x 32Bit x 4 Banks K4D553235F-GC2A、K4D553235F-GC25.

2) FLASH 存储器

FLASH 存储器用于存储FPGA 程序和屏体控制参数,如时间程控亮度表、亮度色度校正系数等。

3) 外部设备

外部设备包括DCDC 电源、时钟、晶振、LED 指示灯、电源、ESD 保护电路、位开关、PCIe 插口等辅助电路,其中PCIe 通讯是原传统双口千兆网LED控制系统所不具备的。

2. 2 接收分配器

超高分辨率LED 显示屏控制系统设计接收分配器的逻辑设计框图见图2.可以看出,其高速通讯逻辑、FPGA、存储器和外设与发送器的硬件设计基本相同,不同之处在于到LED 屏体的1 Gbit /s 网络输出集成和音频输出模块。

2. 2. 1 LED 视频输出

LED 视频输出是实现LED 显示的重要部分。

考虑到成本和与原屏体控制器的兼容因素,本方案采用1 Gbit /s 带宽的千兆网分区通讯模式,10 ~ 12个千兆网链路矩阵,支持10 Gbit /s 总带宽并行数据输出,足以满足4K2K 全高清信号显示。

千兆网PHY 阵列由3 个4 口PHY 构成,例如Marvell 公司的88E1240[6] 具有4 个SGMII 接口,Broadcom 公司的BCM5466( 256p BGA 封装) [7]具有4 × SGMII 或4 × RGMII ( Reduced Gigabit MediaIndependent Interface) 接口。SGMII 是1. 25 Gbit /s的千兆网高速差分串行接口( 无时钟双向4 线) ,RGMII 的数据速率是250 MHz( 含125 MHz 时钟双向12 线) 。如FPGA I /O 口足够用,还可采用RGMII 模式。从简化设计考虑,采用了SGMII 接口,这在FPGA 很容易实现,例如Altera 的Stratix○R V,Stratix IV,Stratix III,Arria○R V,和Arria II GX 系列均提供了1 Gbit /s( 可上升到1. 4 Gbit /s) 的带动态相位调整( DPA) 电路的源同步差分I /O 信号,支持LVDS、LVPECL、3. 3 V PCML 和HyperTransportTM 差分电气标准。DPA 电路支持多种串行/解串行( SerDes) 因子,包括8X 和10X 模式。每个通道都有各自的DPA 电路,为每个通道提供独立的数据对齐功能。

由于源同步时钟方案的高速接口可达到1. 25Gbit /s 传送速率,时钟至通道和通道至通道偏移的容限大大缩小。为了保持在允许的偏移内,设计者必需使用精确的印刷电路板( PCB) 设计技术,因为走线长度最细微的不匹配都可能导致错误的数据传送。其他诸如抖动、温度和电压变化等影响让这个问题更加复杂,简单的静态相位调整技术不是非常有效。Altera 在上述器件中集成了动态相位调整电路( DPA) 和专用源同步电路的快速锁相环( PLL) 。

动态相位调整器DPA 使用快速PLL 生成的8 个相移时钟中的1 个,选择最接近输入数据中部的时钟相位来采样数据和对齐数据。这种对齐是连续进行的,能够补偿时钟和数据信号之间实时时序变动导致的动态变化,有效消除了由时钟或数据偏移引发的信号对齐问题,大大简化了PCB 设计[8]。

可采用Lattice 的ECP40-30 芯片,它具有4 个可达6 Gbit /s 的SerDes,18 个1. 25 Gbit /s.( 带CDR) 差分I /O, 484P BGA 封装。

2. 2. 2 音频输出

音频输出模块将来自FPGA 解码后的音频信号进行处理后输出到功放,以实现高保真的音响播放,所采用的技术和器件可参考其他文献。

3 结束语

超高清LED 显示屏单卡网线控制系统采用了支持HDMI1. 4a 的HDMI /DVI 双输入解码芯片、10GBASE-T PHY 和多个高速SerDes 串口的中高档FPGA 芯片,从而实现了单卡控制的4K2K 超高分辨率显示、高色阶显示、3D 显示和高保真音频同步播放,是性价比很高的LED 和液晶拼接墙控制器换代产品,尤其适用于超高清多媒体播放。超高清LED 显示屏单卡网线控制系统的不足之处是仅适用于100 m 近距离传输,若超过100 m,需外挂光纤转换器或研制开发10 Gbit /s 单卡光纤控制系统。

电子发烧友App

电子发烧友App

评论