1 前言

随着网络规模的持续膨胀和新型网络应用需求的不断增长,目前基于IPv4技术的因特网在可扩展性、IP地址空间、安全、服务质量控制、移动性、运营管理和盈利模式等诸多方面面临着挑战,尤其是地址空间匮乏、可扩展性差等缺陷严重制约了因特网的发展,需要探索新的技术来解决这些问题

以太网是当前最基本、最流行的局域网组网技术,为了适应各种新开展的业务如流视频等,其速率也在不断提高

2 网络接口功能分析

千兆以太网原先是作为一种交换技术设计的,采用光纤作为上行链路,用于楼宇之间的连接,之后在服务器的连接和骨干网中,千兆以太网获得了广泛应用

基于千兆以太网的发展现状和良好的应用前景,当前国内外研制各种核心路由器和高性能交换机的公司不再满足于能够提供低密度(单接口、双接口等)千兆以太网线路接口卡模块,纷纷推出或开始研制高密度(四接口、八接口等)的线路接口卡模块,高密度千兆以太网线路接口卡的研究正在成为一个热点

1).多种数据包的分类处理:本文研究的十接口千兆线路接口卡兼容IPv4、IPv6双协议栈,需要实现三种二层协议封装格式的拆封与封装处理、两种三层协议的查表处理和一种MPLS协议的处理,在高速环境下实现多种协议的正确处理是一个难点;

2).帧重组合路加速功能的实现:需要实现以太网帧的重组、十接口数据合路调度与加速三种功能,这是千兆线路接口卡满足线速处理功能的关键;

3). 十接口数据合路调度功能的实现:需要研究一种具有良好扩展性和时延性能的调度算法,实现高速环境下十接口数据合路调度的功能

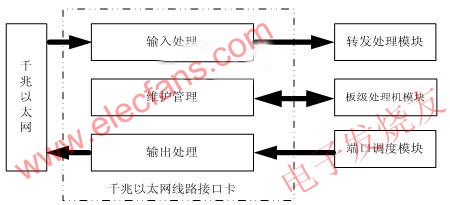

从功能角度来看

图1 千兆以太网线路接口卡功能示意图

3 硬件设计与实现

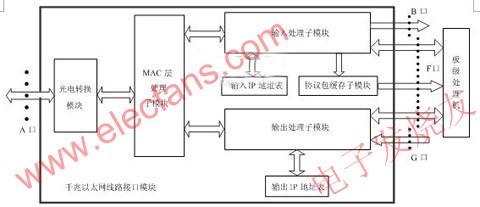

经过对十接口千兆以太网线路接口卡功能和性能需求进行认真分析,按照功能清晰、接口简单、实现容易的原则,设计了其实现方案,并按照设计方案对千兆以太网线路接口卡进行了子模块划分,共分为光电转换子模块、MAC层处理子模块、输入处理子模块、输出处理子模块、输入IP地址***模块、输出IP地址***模块和协议报文缓存子模块等七个子模块

图 2 十接口千兆以太网线路接口卡模块结构图

其中MAC层处理子模块是千兆线路接口卡设计的核心,选用PMC-Sierra公司的PM3388芯片为MAC层处理芯片, PM3388芯片是目前市场上唯一支持十接口的千兆以太网控制器,其功能特性如下:

十路千兆以太网控制器(同时完成PHY层和MAC层功能);

通过内部十个SERDES接口直接与光电转换模块相连

从网络上接收8B/10B格式码流

每个接口提供多播地址过滤及8个单播地址过滤;

提供标准的IEEE 802.3 以太网帧格式完整性检验

内部提供224K字节接收FIFO和64K发送FIFO,可在十路接口上灵活配置;

提供SATURN标准的PL4(POS-PHY Level 4)标准16位LVDS总线接口,速率可达700Mbps;

提供标准IEEE 1149.1 JTAG测试端口;

提供微处理器接口;

提供线路侧环回和系统侧环回的系统级调试功能;

提供丰富的配置及统计寄存器

PM3388工作流程包括接收处理和发送处理两部分

如果该以太网帧无误

为了保证PL4接口达到十路1Gbps的速率,PM3388的参考时钟引脚接160MHz时钟晶振,输入输出接口的采样时钟通过将该时钟倍频获得320MHz时钟,输入输出数据分别在时钟双沿采样,可以获得640Mbps的数据数率,总带宽达10.24Gbps,可以满足0丢包率性能对带宽的要求

此外,输入处理FPGA是千兆以太网线路接口卡模块设计的重点之一,主要的功能是将各种标准的MAC帧数据格式转换为网络层统一的数据格式,为网络层处理屏蔽掉底层物理接口

输入处理FPGA采用Altera公司Stratix GX系列的EP1SGX25F芯片,该芯片具有25660个逻辑单元,16个高速收发器通道,39个源同步IO和总数为1944576比特的RAM,可以满足实现输出处理功能对资源的要求

输入处理子模块主要完成输入处理和配置统计两大功能:第一、接收MAC层处理子模块发送过来的数据片,完成MAC帧重组和十路数据合路处理,再根据MAC帧封装的三层协议类型实现数据包的分类处理,按照不同的处理要求把数据包分别送B接口、F接口或者同时送两个接口

4 系统调试

FPGA的调试包括输入FPGA和输出FPGA两部分,主要检查FPGA的焊接、时钟和程序下载等是否正确,调试方法是用VHDL编写一个计数器的程序,用JTAG下载到FPGA中,利用SignalTap软件和指示灯测试FPGA是否工作正常

PM3388芯片是千兆线路接口卡完成MAC层控制功能的芯片,其调试是整个千兆线路接口卡调试的重点

PM3388芯片寄存器配置的调试过程为:首先往一个可读写寄存器(选择地址为0x6的寄存器)中写入一个数,再读出来比较是否正确,如果不正确,通过SignalTap软件分别抓输出FPGA与PM3388芯片的微处理机接口的读写控制信号,确定错误是发生在写操作还是读操作上,排除错误

而PL4系统侧环回主要是为了验证输出FPGA与PM3388的输入PL4接口、输入FPGA与PM3388的输出PL4接口是否正常,调试方法是使用板级处理机向输出处理FPGA发送协议包,输出处理FPGA再把该数据包发送到PM3388的PL4接口的接收侧,接收侧把该数据包环回到PL4接口的发送侧,从发送侧发送到输入处理FPGA,最后该数据包被板级处理机读回来进行比较

5 总结

本文的创新点在于采用合适的设计方案和调试方案,完成了十接口千兆线路接口卡的设计与实现,研制的千兆线路接口卡完全满足了T比特路由器项目对十接口千兆线路接口卡设计的功能与性能要求