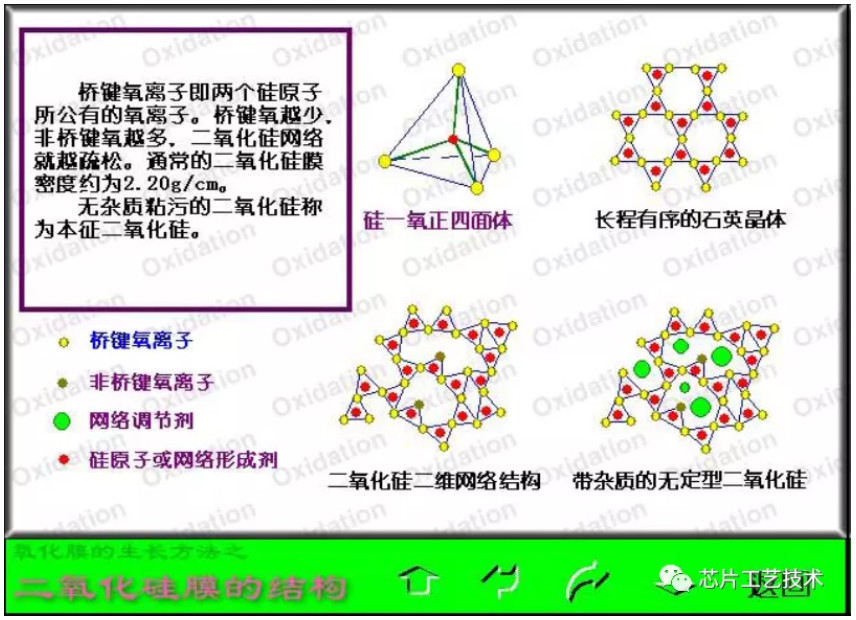

在自然界中sio2二氧化硅的存在是非常广泛的,本内容解释了sio2是什么意思,sio2的物理性质是什么,让大家充分了解sio2

2011-12-13 10:41:13 20242

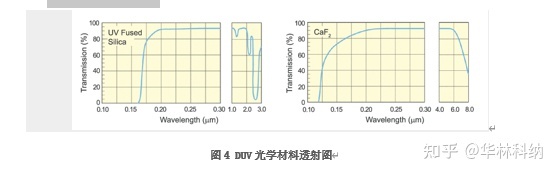

20242 关键词:玻璃陶瓷;氢氟酸;蚀刻条件;蚀刻速率;机制 引言 我们江苏华林科纳研究了氧化镁-氧化铝-二氧化硅玻璃陶瓷在氢氟酸中的腐蚀条件和机理。结果表明,在室温下,非晶相的腐蚀速率是纯堇青石晶体的218

2022-01-04 14:39:28 1655

1655

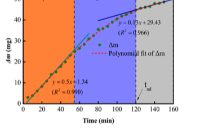

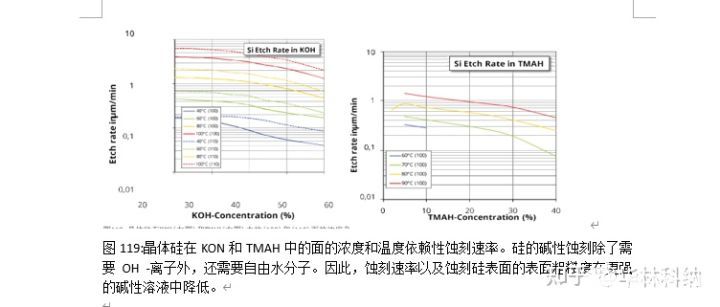

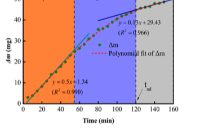

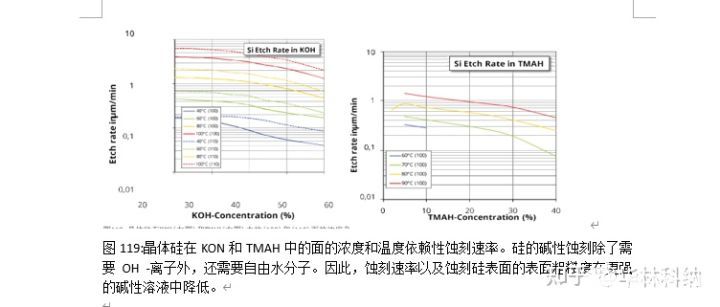

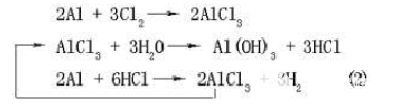

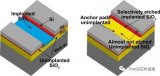

蚀刻机理 诸如KOH-、NaOH-或TMAH-溶液的强含水碱性介质蚀刻晶体硅通孔 硅+ 2 OH- + 2 H O 硅(OH) + H 二氧化硅(OH) 2- + 2 H 因为不同晶面的Si原子

2022-07-11 16:07:22 1344

1344

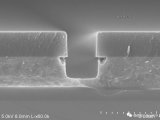

等离子体图形化刻蚀过程中,刻蚀图形将影响刻蚀速率和刻蚀轮廓,称为负载效应。负载效应有两种:宏观负载效应和微观负载效应。

2023-02-08 09:41:26 2467

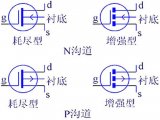

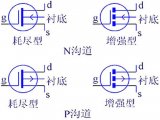

2467 铝)的栅极和隔着氧化层(O-绝缘层SiO2)的源极施加电压,产生电场的效应来控制半导体(S)导电沟道开关的场效应晶体管。由于栅极与源极、栅极与漏极之间均采用SiO2绝

2023-11-18 08:11:02 1325

1325

干法刻蚀技术是一种在大气或真空条件下进行的刻蚀过程,通常使用气体中的离子或化学物质来去除材料表面的部分,通过掩膜和刻蚀参数的调控,可以实现各向异性及各向同性刻蚀的任意切换,从而形成所需的图案或结构

2024-01-20 10:24:56 1114

1114

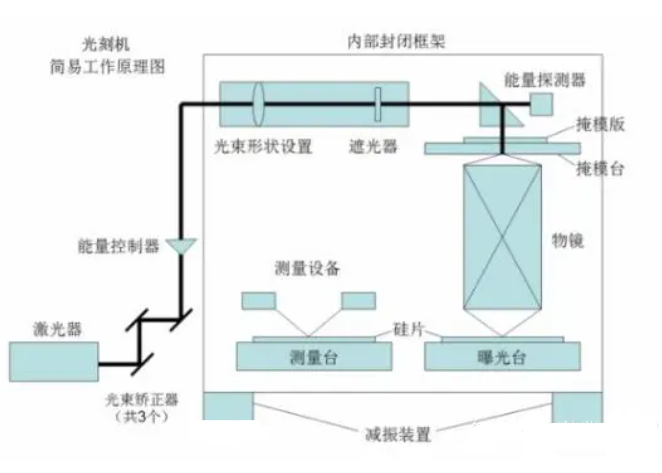

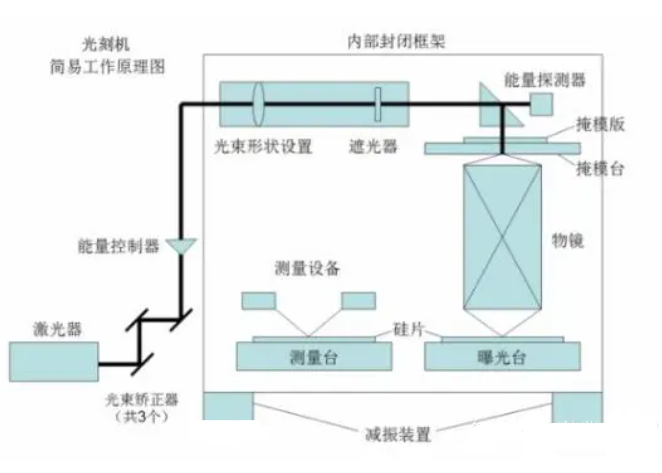

在半导体加工工艺中,常听到的两个词就是光刻(Lithography)和刻蚀(Etching),它们像俩兄弟一样,一前一后的出现,有着千丝万缕的联系,这一节介绍半导体刻蚀工艺。

2024-01-26 10:01:58 552

552

(干法刻蚀硅)17、 RIE SiO2 (干法刻蚀二氧化硅)18、 RIE Si3N4 (干法刻蚀氮化硅)19、 RIE Al、AlN、Ti、TiN (干法刻蚀金属,包括干法刻蚀铝、干法刻蚀氮化

2015-01-07 16:15:47

AOE刻蚀氧化硅可以,同时这个设备可以刻蚀硅吗?大致的气体配比是怎样的,我这里常规的刻蚀气体都有,但是过去用的ICP,还没有用过AOE刻蚀硅,请哪位大佬指点一下,谢谢。

2022-10-21 07:20:28

我正在使用 CY8C5867LTI-LP025。

我知道我需要使用 SIO 端口来使用 I2C、UART 等。

SPI通信是否也需要使用 SIO 端口?

2024-03-06 06:23:39

was used to prepare ferrite t hin film on SiO2 layer . The ferrite film of surface ap2pear s crack

2009-08-08 09:42:31

在上一讲已经知道了 FPGA就实现技术是可以分成三种不同 FPGA 的结构特点、实现的机理,这三种 FPGA 分别是基于 SRAM 技术、基于反熔丝技术、基于 E2PROM/FLASH技术。就电路结构...

2021-07-30 06:39:06

IGBT传统防失效机理是什么IGBT失效防护电路

2021-03-29 07:17:06

本帖最后由 gk320830 于 2015-3-9 22:04 编辑

N沟道耗尽型MOS管的二氧化硅中掺有大量的正离子(不是掺入低价元素形成的P型半导体),也就是说在不加电的情况下G(栅极)也

2009-07-04 16:00:27

`请问SMT焊点的主要失效机理有哪些?`

2019-12-24 14:51:21

post-charge time of SIO_D中post应该怎么翻译

2017-07-09 16:41:25

精炼、晶体生长和晶圆形成。硅精炼开始于在大约 2000 °C 的电弧炉中用碳源还原二氧化硅。碳有效地从 SiO2 分子中“拉”出氧,从而将 SiO2 化学还原为大约 98% 的纯硅,称为冶金级硅

2021-07-06 09:32:40

逆变器3.第一步将是形成n(1)用 SiO2(氧化物)保护层覆盖晶圆(2)删除应构建 n 阱的层(3)植入或扩散 n 掺杂剂进入暴露的晶圆(4)剥离 SiO2如有侵权,请联系作者删除`

2021-07-08 13:13:06

新加坡知名半导体晶圆代工厂招聘资深刻蚀工艺工程师和刻蚀设备主管!此职位为内部推荐,深刻蚀工艺工程师需要有LAM 8寸机台poly刻蚀经验。刻蚀设备主管需要熟悉LAM8寸机台。待遇优厚。有兴趣的朋友可以将简历发到我的邮箱sternice81@gmail.com,我会转发给HR。

2017-04-29 14:23:25

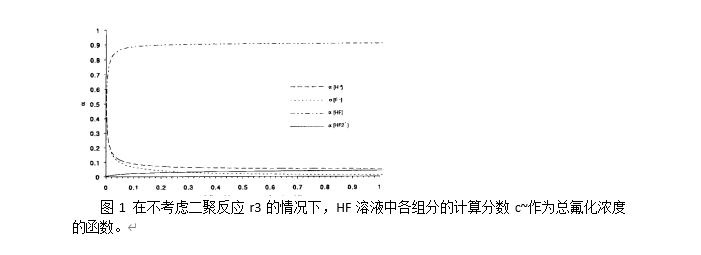

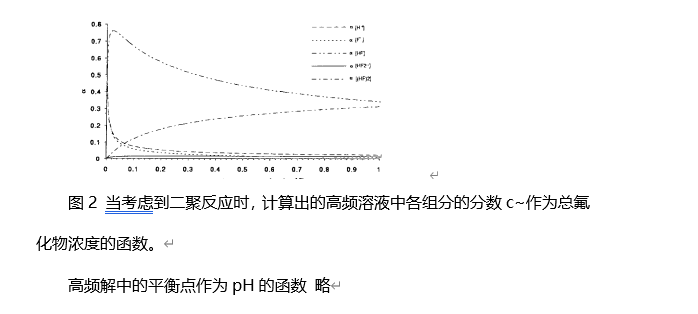

典型的硅刻蚀是用含氮的物质与氢氟酸的混合水溶液。这一配比规则在控制刻蚀中成为一个重要的因素。在一些比率上,刻蚀硅会有放热反应。加热反应所产生的热可加速刻蚀反应,接下来又产生更多的热,这样进行下去会

2018-12-21 13:49:20

线路上的数据波都可以,但SRAM没有响应。MISO线ReMin在高电平。保持(引脚7)被绑定到3V,SiO2(引脚3)被连接到GND。我试图替换MCU和SRAM,但问题仍然存在。这是我的简单代码。我哪里错了?谢谢。

2019-08-08 11:07:25

的偏压使得正性的可移动离子在poly/SiO2界面积累,造成阈值电压正偏。为评估器件在使用过程中阈值电压漂移情况,派恩杰半导体进行了大量BTI实验,基于实验数据建立了PBTI&NBTI

2022-03-29 10:58:06

“MOSFET”是英文MetalOxide Semicoductor Field Effect Transistor的缩写,译成中文是“金属氧化物半导体场效应管”。它是由金属、氧化物(SiO2或

2021-04-23 07:04:52

半导体光刻蚀工艺

2021-02-05 09:41:23

的加工工艺流程,加工过程中需要运用刻蚀机在晶圆上把复杂的3D图形一层一层“堆叠”起来,实现单片机IC芯片的更小化。芯片,本质上是一片载有集成电路(IC:Integrated circuit)的半导体元件

2018-08-23 17:34:34

台面刻蚀深度对埋栅SITH栅阴击穿的影响针对台面刻蚀深度对埋栅型静电感应晶闸管(SITH)栅阴击穿特性的影响做了实验研究。实验结果表明,随着台面刻蚀深度的增大,器件栅阴击穿由原来的软击穿变为硬击穿

2009-10-06 09:30:24

IT验证工作得以实现的基础。随着电路的日益复杂化、高度集成化,可探测的节点越来越少,可访问性越来越受到限制,后驱动技术在故障注入中的应用有效地解决了这个问题。然而后驱动可能引发的退化加速越来越受到关心,对后全文下载

2010-04-22 11:29:19

。目前广泛应用的是SiO2为绝缘层的绝缘栅场效应管,称为金属-氧化物-半导体场效应管,简称MOSFET。以功能类型划分,MOSFET分为增强型和耗尽型两种,其中耗尽型与增强型主要区别是在制造SiO2绝缘层

2019-07-29 06:01:16

介电常数膜如置于空气中,在吸收了膜表面吸附的水分后,会有膜的介电常数比增大的问题。对此,在典型的有机系低介电常数材料MPS及PAE中,找出了吸水性非常低的材料。如把使用TEOS的等离子CVD的SiO2膜

2018-08-29 10:53:04

1. 为什么要pad oxidation?仅仅是为了抵消SIN和SI之间的应力吗?这里的所谓应力指的是由于热膨胀导致的SIN和SI之间的应力吗?(印象中两者的的热膨胀系数好象很接近的?难道SIO2的是介于两者之间的?)

2011-12-02 14:32:59

表面产生龟裂,尽管可在包层中掺杂少量的B2O3 和 P2O5 来提高 SiO2 的热膨胀系数,同时降低 SiO2 的软化温度,但仍然难控制其中的残余应力。多次沉积、多次退火工艺难控制。采用 FHD 法

2018-02-22 10:06:53

上。 刻蚀只去除曝光图形上的材料。 在芯片工艺中,图形化和刻蚀过程会重复进行多次。2017年3月11日,据CCTV2财经频道节目的报道,中微AMEC正在研制目前世界最先进的5纳米等离子刻蚀机,将于2017年底将量产。转自吴川斌的博客`

2017-10-09 19:41:52

刻蚀技术,保留下栅隔离层上面的氮化硅层 12、湿法氧化,生长未有氮化硅保护的 SiO2 层,形成 PN 之间的隔离区 13、热磷酸去除氮化硅,然后用 HF 溶液去除栅隔离层位置的 SiO2 ,并重

2011-12-01 15:43:10

制备光路图案。所得有机无机复合ZrO22SiO2 板型平面光波导(衬底层+ 导光层) ,用棱镜耦合截断法测试其光损耗在632. 8 nm 波长处约为0. 8 dB/ cm。对板型平面波导的导光层薄膜

2009-08-08 09:57:18

打开后,D到S才会有电流流过。但实际上由于自由电子的存在,自由电子的附着在SIO2和N+、导致D-S有漏电流。图1.1.1 带IGBT开关逆变中的漏电流2、 电源漏电流开关电源中...

2021-08-27 06:09:57

实验名称:功率放大器在合成射流高效掺混机理研究中的应用

实验内容:合成射流是一种新型主动流动控制技术,其主要工作原理是利用振动薄膜或活塞周期性地吹/吸流体,在孔口外形成涡环,这些涡环在自诱导

2024-03-08 17:47:25

使用过程中的耐擦洗性以及美观度等,因此涂层的耐磨性是涂层的关键性能要求。考察n(SiO2)︰n(M+)︰n(PO43-)的不同比例对涂层耐摩擦次数的影响,以及在此基础上添加0.5%质量分数的纳米氧化锆分散

2017-10-13 16:53:27

老化与热老化;③电介质内部的电化学反应;④银离子迁移;⑤电介质在电容器制造过程中受到机械损伤;⑥电介质分子结构改变;⑦在高湿度或低气压环境中极间飞弧;⑧在机械应力作用下电介质瞬时短路。3.1.2引起电

2011-11-18 13:16:54

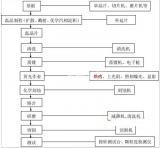

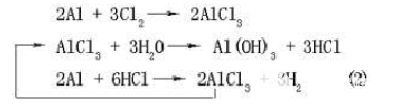

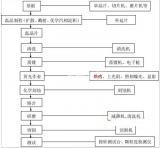

芯片制作工艺流程 工艺流程1) 表面清洗 晶圆表面附着一层大约2um的Al2O3和甘油混合液保护之,在制作前必须进行化学刻蚀和表面清洗。2) 初次氧化 有热氧化法生成SiO2 缓冲层,用来减小后续

2019-08-16 11:09:49

注入区表面形成薄薄的SiO2层,杂质离子透过这层SiO2进行注入。 硅和锗半导体材料经高度提纯后,其原子排列已变成非常整齐的晶体状态,称为单晶体也称本征半导体。在本征半导体硅或锗中掺入少量五价杂质元素

2019-08-16 11:11:34

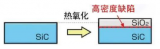

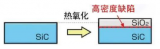

最近需要用到干法刻蚀技术去刻蚀碳化硅,采用的是ICP系列设备,刻蚀气体使用的是SF6+O2,碳化硅上面没有做任何掩膜,就是为了去除SiC表面损伤层达到表面改性的效果。但是实际刻蚀过程中总是会在碳化硅

2022-08-31 16:29:50

我在IND4汽车人App可以帮助大家解答汽车电子的相关技术问题,欢迎通过IND4汽车人App向我咨询。在永磁同步电机中,转子磁场中因为有永磁材料构成此磁体的南极和北极,转子磁场的产生机理及在空间

2021-08-27 07:08:02

氢氟酸要好,容易清除。工艺步骤简单。困难在,扩散均匀,印刷对齐。schmid 的腐蚀法SE 电池交钥匙工程,centrotherm 的激光刻蚀氧化膜SE电池交钥匙工程。 四、湿法腐蚀重扩散层

2018-09-26 09:44:54

Microstructures在SEMICON China期间推出了干法刻蚀模块与氧化物释放技术,该技术为MEMS器件设计师提供了更多的生产选择,同时带来了宽泛的制造工艺窗口,从而使良率得到了提升。麦|斯

2013-11-04 11:51:00

利用射频共溅射方法制备了一系列不同金属含量x的Fex(SiO2)(1−x)金属−绝缘体颗粒膜,系统地研究了薄膜的霍尔效应及其产生机理。在室温和1.3 T的磁场下,当体积分数为0.52

2008-12-03 13:10:25 9

9 ,使用温度在-200~+260℃;2、耐受强酸强碱等强腐蚀样品,比如:王水、魔酸、liu酸等;3、低的溶出和析出,金属元素空白值低,铅含量小于0.01ppb;4、本产

2022-09-01 13:30:27

研究了SiC表面氢化降低界面态密度的机理。采用缓慢氧化、稀释的HF刻蚀、沸水浸泡的表面氢化处理方法,降低SiC表面态密度。该方法用于SiC器件的表面处理,在100℃以下制备了理想

2009-05-07 20:31:44 35

35 分别以丙醇锆和正硅酸乙酯为原料,采用溶胶-凝胶工艺制备了性能稳定的ZrO2和SiO2溶胶。用旋转镀膜法在K9玻璃上分别制备了SiO2单层膜、ZrO2单层

2010-03-03 13:50:49 21

21 ITO玻璃技术之SiO2阻挡膜层规格

SiO2 阻挡膜层规格

2008-10-25 16:04:25 1408

1408 镀复SiO2膜的电容器介质膜

成功一种能在几百小时连续沉积SiO2膜的新颖电子束蒸发装置,获国家发明专利,在此基础上

2009-12-08 09:03:32 702

702 什么是Prescott/SiO2F?

这是Intel最新的CPU核心,目前还只有Pentium 4而没有低端的赛扬采用,其与Northwood最大的区别是采用了0.09um制造工艺

2010-02-04 11:28:54 394

394 干法刻蚀原理

刻蚀作用:去除边缘PN结,防止上下短路。干法刻蚀原理:利用高频辉光放电反应,使CF4气体激活成活性粒子,这些活性

2010-07-18 11:28:20 5637

5637 本文在浅沟槽隔离刻蚀过程中发现,当刻蚀腔室上石英窗口的温度超过85℃时,刻蚀终止出现在300mm晶圆的中心。我们认为刻蚀终止的原因是由于某些低挥发SiOxCly刻蚀产物再淀积。石英

2012-05-04 17:09:37 2803

2803

LED 芯片的制造工艺流程:外延片→清洗→镀透明电极层→透明电极图形光刻→腐蚀→去胶→平台图形光刻→干法刻蚀→去胶→退火→SiO2 沉积→窗口图形光刻→SiO2 腐蚀→去胶→N极图形光刻→预清洗→镀膜→剥离→退火→P 极图形光刻→镀膜→剥离→研磨→切割→芯片→成品测试。

2016-08-05 17:45:21 17422

17422

理论及不同退火温度、不同退火时间、SiO2薄膜厚度、SiO2薄膜折射率、不同盖片等试验参数对制备非吸窗口的影响,并且讨论了Si0,薄膜介质膜的多孔性对无杂质诱导量子阱混合的影响.实验制备出蓝移波长为53 nm的非吸收窗口,最佳制备非吸收窗口条件为退火温度为

2018-02-10 10:16:35 0

0 钝化层刻蚀对厚铝铝须缺陷影响的研究

2018-03-06 09:02:50 5607

5607 反刻是在想要把某一层膜的总的厚度减小时采用的(如当平坦化硅片表面时需要减小形貌特征)。光刻胶是另一个剥离的例子。总的来说,有图形刻蚀和无图形刻蚀工艺条件能够采用干法刻蚀或湿法腐蚀技术来实现。为了复制硅片表面材料上的掩膜图形,刻蚀必须满足一些特殊的要求。

2018-12-14 16:05:27 68523

68523 在等离子增强化学气相沉积法PECVD沉积 SiO2和 SiN掩蔽层过程中!分解等离子体中浓度较高的H原子使MG受主钝化!同时在P-GaN材料表面发生反应形成浅施主特性的N空位。

2018-12-17 08:00:00 17

17 N沟道增强型MOS管在P型半导体上生成一层SiO2薄膜绝缘层,然后用光刻工艺扩散两个高掺杂的N型区,从N型区引出电极(漏极D、源极S);在源极和漏极之间的SiO2绝缘层上镀一层金属铝作为栅极G;P型半导体称为衬底,用符号B表示。由于栅极与其它电极之间是相互绝缘的,所以NMOS又被称为绝缘栅型场效应管。

2019-03-10 10:44:22 23364

23364

外延片→清洗→镀透明电极层→透明电极图形光刻→腐蚀→去胶→平台图形光刻→干法刻蚀→去胶→退火→SiO2沉积→窗口图形光刻→SiO2腐蚀→去胶→N极图形光刻→预清洗→镀膜→剥离→退火→P极图形光刻→镀膜→剥离→研磨→切割→芯片→成品测试。

2019-03-27 16:58:15 20979

20979 湖北兴力电子材料有限公司年产3万吨电子级氢氟酸项目开工仪式在兴发集团宜昌新材料产业园举行。该项目建成后,将有效填补国内市场高端电子级氢氟酸生产空白,实现高端电子级氢氟酸的国产化。

2019-05-17 18:13:56 6718

6718 突破!滨化集团电子级氢氟酸成功打入韩国市场

2019-07-18 10:23:31 11155

11155 据最新消息,中国滨化集团生产的氢氟酸已成功拿到部分韩国半导体厂商的批量订单!

2019-07-18 14:56:17 2634

2634 SiO2 薄膜具有良好的硬度、光学、介电性质及耐磨、抗蚀、机械等特性,在光学、微电子等领域有着广泛的应用前景

2020-03-10 08:00:00 23

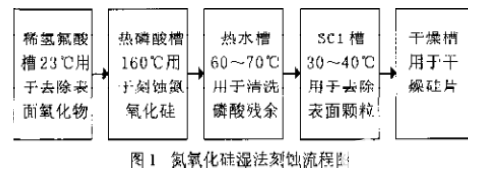

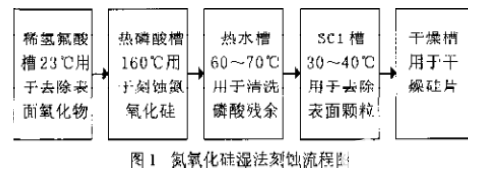

23 清洗不当造成的表面缺陷的形成机理,并通过合理的实验设计和分析,给出了具体的解决方案。 热磷酸湿法刻蚀已经在半导体制造工艺中应用了几十年了。由于热磷酸对氮化硅和氮氧化硅刻蚀具有良好的均匀性和较高的选择比,一直到

2020-12-29 14:36:07 2510

2510

在集成电路的制造过程中,刻蚀就是利用化学或物理方法有选择性地从硅片表面去除不需要的材料的过程。从工艺上区分,刻蚀可以分为湿法刻蚀和干法刻蚀。前者的主要特点是各向同性刻蚀;后者是利用等离子体来进行

2020-12-29 14:42:58 8547

8547

刻蚀机不能代替光刻机。光刻机的精度和难度的要求都比刻蚀机高出很多,在需要光刻机加工的时候刻蚀机有些不能办到,并且刻蚀机的精度十分笼统,而光刻机对精度的要求十分细致,所以刻蚀机不能代替光刻机。

2022-02-05 15:47:00 39913

39913 刻蚀速率是指在刻蚀过程中去除硅片表面材料的速度通常用Å/min表示, 刻蚀窗口的深度称为台阶高度。 为了高的产量, 希望有高的刻蚀速率。 在采用单片工艺的设备中, 这是一个很重要的参数。 刻蚀速率由工艺和设备变量决定, 如被刻蚀材料类型、 蚀机的结构配置、 使用的刻蚀气体和工艺参数设置。

2022-03-15 13:41:59 2907

2907

本文对晶片采用HF溶液洗净的晶片氢氟酸处理后的护发素及干燥方法,使用异丙基去除上述晶片表面残存的HF的步骤,关于晶片氢氟酸处理后的护发素和干燥方法,其特点是在对上述晶片施加82-84℃温度的同时通过

2022-03-23 17:06:05 1599

1599

在微电子技术以及在微结构、微光学和微化学传感器中,需要在由不同材料构成的大面积的薄膜层中构造功能完善的结构。

2022-03-29 15:49:58 3961

3961

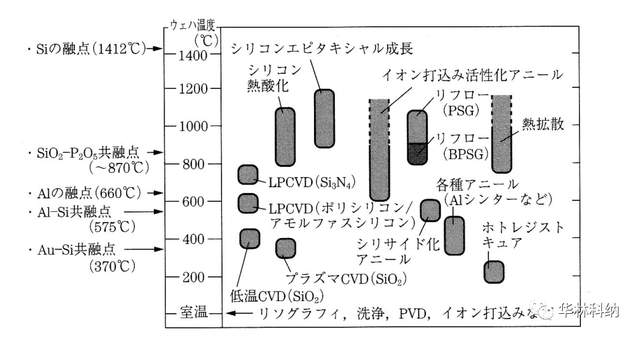

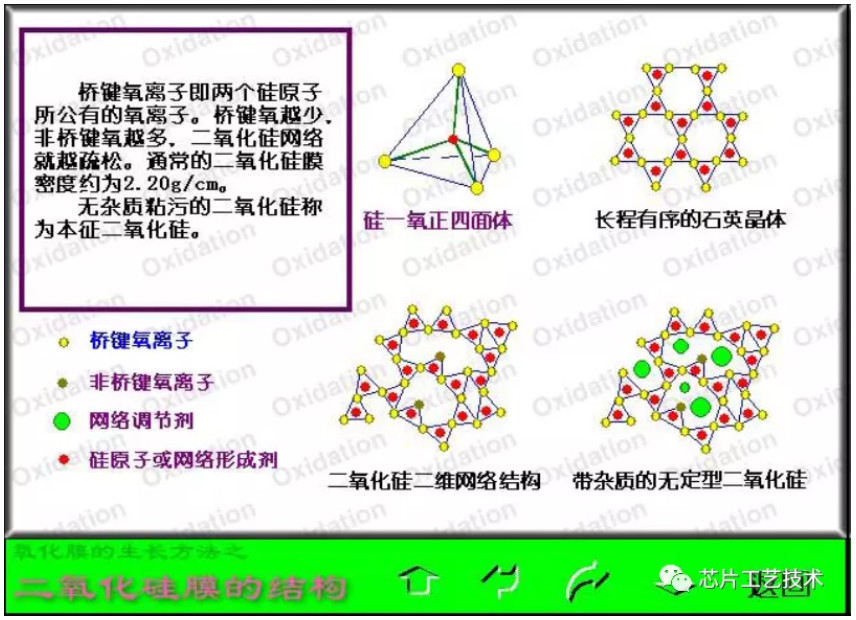

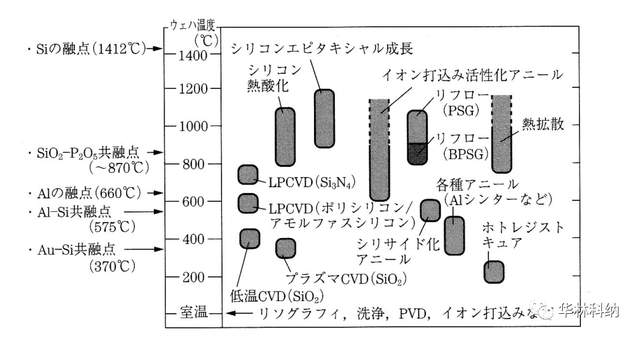

Si晶片在大气中自然氧化,表面非常薄,但被SiO2膜复盖。Si和在其上产生的SiO2膜的密合性很强。在高温下进行氧化,会产生厚而致密且稳定的膜。Si的熔点为1412℃,但SiO2的熔点为1732

2022-04-13 15:26:08 4795

4795

刻蚀室半导体IC制造中的至关重要的一道工艺,一般有干法刻蚀和湿法刻蚀两种,干法刻蚀和湿法刻蚀一个显著的区别是各向异性,更适合用于对形貌要求较高的工艺步骤。

2022-06-13 14:43:31 6

6 湿法刻蚀也称腐蚀。硅的湿法刻蚀是 MEMS 加工中常用的技术。其中,各向同性 (Isotropic)湿法刻蚀常用的腐蚀剂是由氢氟酸(HF)、硝酸( HNO3)和乙酸(CH3COOH)组成的混合物

2022-10-08 09:16:32 3581

3581 这款GO-FET生物传感器采用由p型硅(Si)衬底以及覆盖其上的二氧化硅(SiO2)介电层组成的p型硅片(Si/SiO2)制备。

2022-11-10 09:58:24 453

453 刻蚀是移除晶圆表面材料,达到IC设计要求的一种工艺过程。刻蚀有两种:一种为图形 化刻蚀,这种刻蚀能将指定区域的材料去除,如将光刻胶或光刻版上的图形转移到衬底薄膜 上

2023-02-01 09:09:35 1748

1748 刻蚀速率是测量刻蚀物质被移除的速率。由于刻蚀速率直接影响刻蚀的产量,因此刻蚀速率是一个重要参数。

2023-02-06 15:06:26 3998

3998 刻蚀有三种:纯化学刻蚀、纯物理刻蚀,以及介于两者之间的反应式离子刻蚀(ReactiveIonEtch,RIE)。

2023-02-20 09:45:07 2586

2586 对于湿法刻蚀,大部分刻蚀的终点都取决于时间,而时间又取决于预先设定的刻蚀速率和所需的刻蚀厚度。由于缺少自动监测终点的方法,所以通常由操作员目测终点。湿法刻蚀速率很容易受刻蚀剂温度与浓度的影响,这种影响对不同工作站和不同批量均有差异,因此单独用时间决定刻蚀终点很困难,一般釆用操作员目测的方式。

2023-03-06 13:56:03 1773

1773 硅的碱性刻蚀液:氢氧化钾、氢氧化氨或四甲基羟胺(TMAH)溶液,晶片加工中,会用到强碱作表面腐蚀或减薄,器件生产中,则倾向于弱碱,如SC1清洗晶片或多晶硅表面颗粒,一部分机理是SC1中的NH4OH

2023-06-05 15:10:01 1598

1598 目前,许多企业在SiC MOSFET的批量化制造生产方面遇到了难题,其中如何降低SiC/SiO₂界面缺陷是最令人头疼的问题。

2023-06-13 16:48:17 376

376

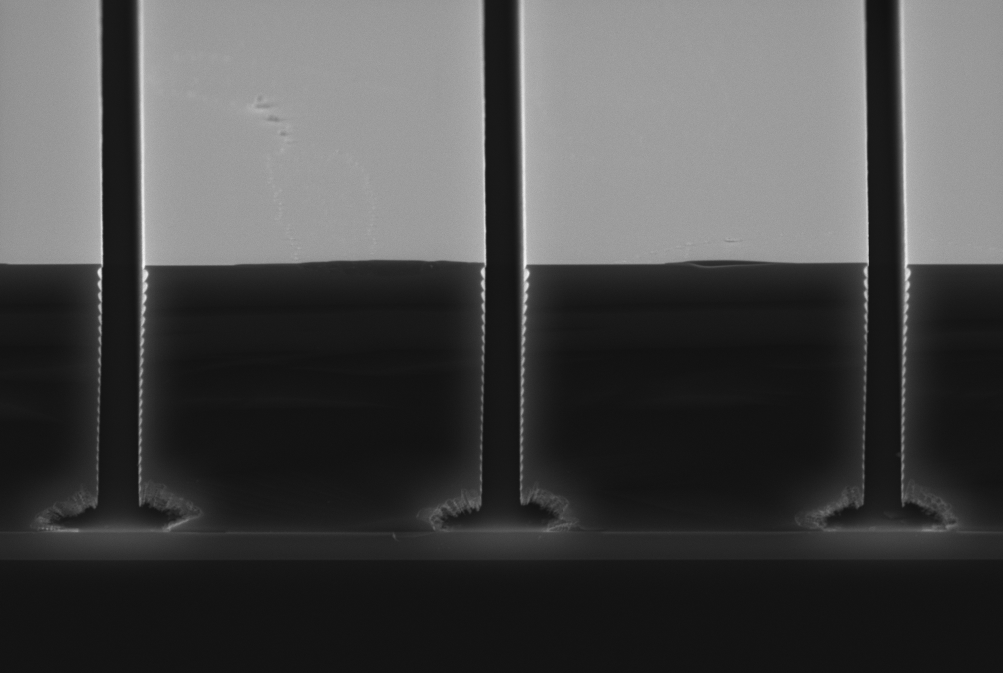

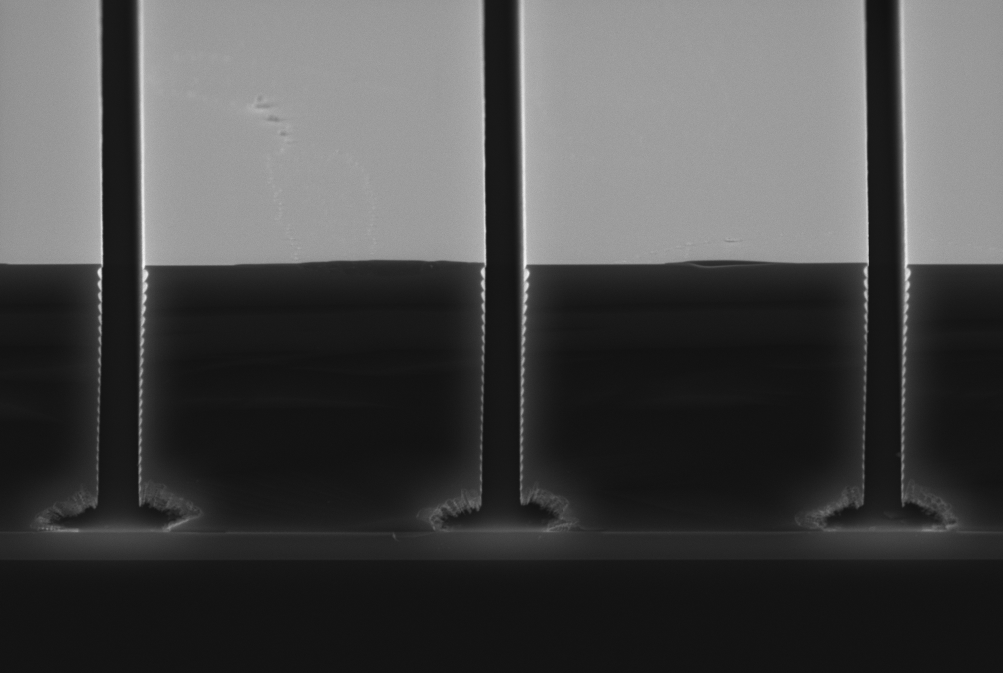

第一种是间歇式刻蚀方法(BOSCH),即多次交替循环刻蚀和淀积工艺,刻蚀工艺使用的是SF6气体,淀积工艺使用的是C4F8气体

2023-07-14 09:54:46 3214

3214

刻蚀(Etching)的目的是在材料表面上刻出所需的图案和结构。刻蚀的原理是利用化学反应或物理过程,通过移除材料表面的原子或分子,使材料发生形貌变化。

2023-08-01 16:33:38 3915

3915 硅在暴露在空气中时会形成一层氧化硅(SiO2)层。在许多制程步骤中,如在热处理过程之前,需要移除这层氧化硅。氢氟酸是唯一能够有效清洗硅片表面氧化硅的化学品。氢氟酸能够与SiO2发生反应,生成挥发性的氟硅酸,从而清除硅片表面的氧化物层。

2023-08-02 10:40:25 543

543

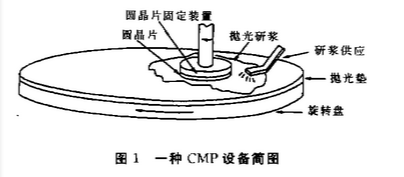

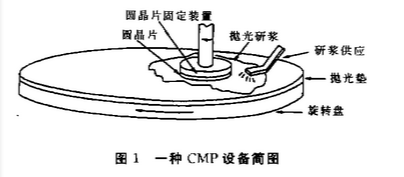

20世纪60年代以前,半导体基片抛光还大都沿用机械抛光,得到的镜面表面损伤是极其严重的。1965年Walsh和Herzog提出SiO2溶胶和凝胶抛光后,以SiO2浆料为代表的化学机械抛光工艺就逐渐代替了以上旧方法。

2023-08-02 10:48:40 7529

7529

在半导体制造中,刻蚀工序是必不可少的环节。而刻蚀又可以分为干法刻蚀与湿法刻蚀,这两种技术各有优势,也各有一定的局限性,理解它们之间的差异是至关重要的。

2023-09-26 18:21:00 3307

3307

刻蚀(或蚀刻)是从晶圆表面去除特定区域的材料以形成相应微结构。但是,在目标材料被刻蚀时,通常伴随着其他层或掩膜的刻蚀。

2023-10-07 14:19:25 2073

2073

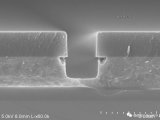

但是,在刻蚀SOI衬底时,通常会发生一种凹槽效应,导致刻蚀的形貌与预想的有很大出入。那么什么是凹槽效应?什么原因引起的?怎么抑制这种异常效应呢?

2023-10-20 11:04:21 461

461

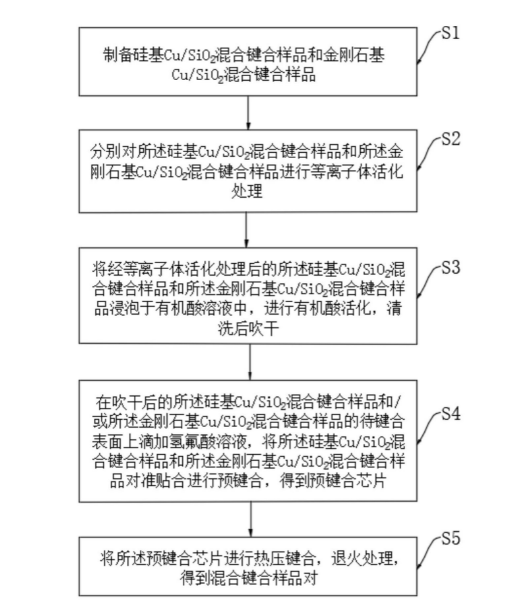

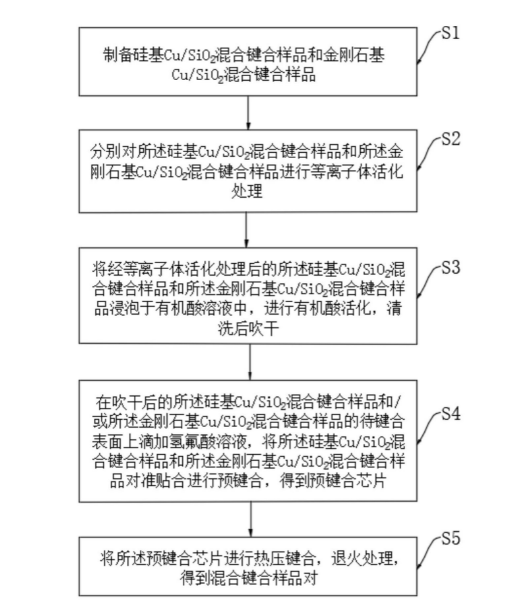

摘要本发明涉及芯片制造技术领域。硅基的cu/sio2混合结合样品和金刚石基础的cu/sio2混合结合样品的准备后,进行等离子体活性。经等离子体活性处理后,将cu/sio2混合结合试料浸泡在有机酸溶液中清洗后干燥。

2023-11-22 09:25:59 285

285

某种电介质的介电常数ε与真空介电常数ε0的比值,称为该电介质的相对介电常数,符号为εr,即εr=ε/ε0,εr是无量纲的纯数,其中真空介电常数ε0=8.854E-12F/m,SIO2的相对介电常数为εr=3.9,所以SIO2的介电常数ε=εr*ε0=3.9×8.854E-12F/m

2023-11-30 15:39:12 674

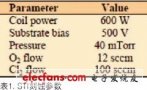

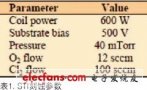

674 影响深硅刻蚀的关键参数有:气体流量、上电极功率、下电极功率、腔体压力和冷却器。

2024-02-25 10:44:39 283

283

刻蚀机的刻蚀过程和传统的雕刻类似,先用光刻技术将图形形状和尺寸制成掩膜,再将掩膜与待加工物料模组装好,将样品置于刻蚀室内,通过化学腐蚀或物理磨蚀等方式将待加工物料表面的非掩膜区域刻蚀掉,以得到所需的凹槽和沟槽。

2024-03-11 15:38:24 471

471

电子发烧友App

电子发烧友App

评论