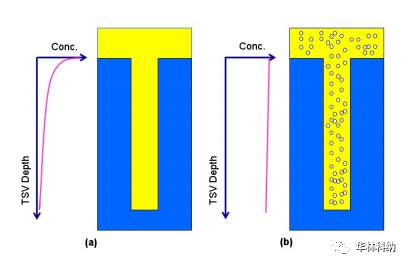

本文研究主要考虑基于CuSn金属互化物的微凸点(μbump)作为芯片堆叠的手段。系统研究了形成金属互化物凸点连接的两种方法。

2012-03-08 16:29:24 5495

5495

电子发烧友网报道(文/黄山明)近日,华为密集公布了多项技术专利,其中引人注意的是华为再次公布了两项与芯片堆叠有关的专利。为何说再次,因为就在一个月前,华为同样公开了“一种芯片堆叠封装及终端设备

2022-05-09 08:09:00 24420

24420 元器件PIP(堆叠封装)和PoP(堆叠组装)的比较

1. PiP (Package In Package,堆叠封装)

PiP一般称堆叠封

2009-11-20 15:47:28 6429

6429 、行业交流和采购洽谈于一体的综合商贸平台。本届活动将分为中国(上海)国际显示技术及应用创新展(简称“DIC EXPO”)、中国(上海)国际显示产业高峰论坛(简称“DIC Forum”)和国际显示技术创新大奖 (简称“DIC AWARD”)三大版块。通过三位一体的协同运营,DIC将实现以展共见行业

2022-07-11 09:40:03 2844

2844

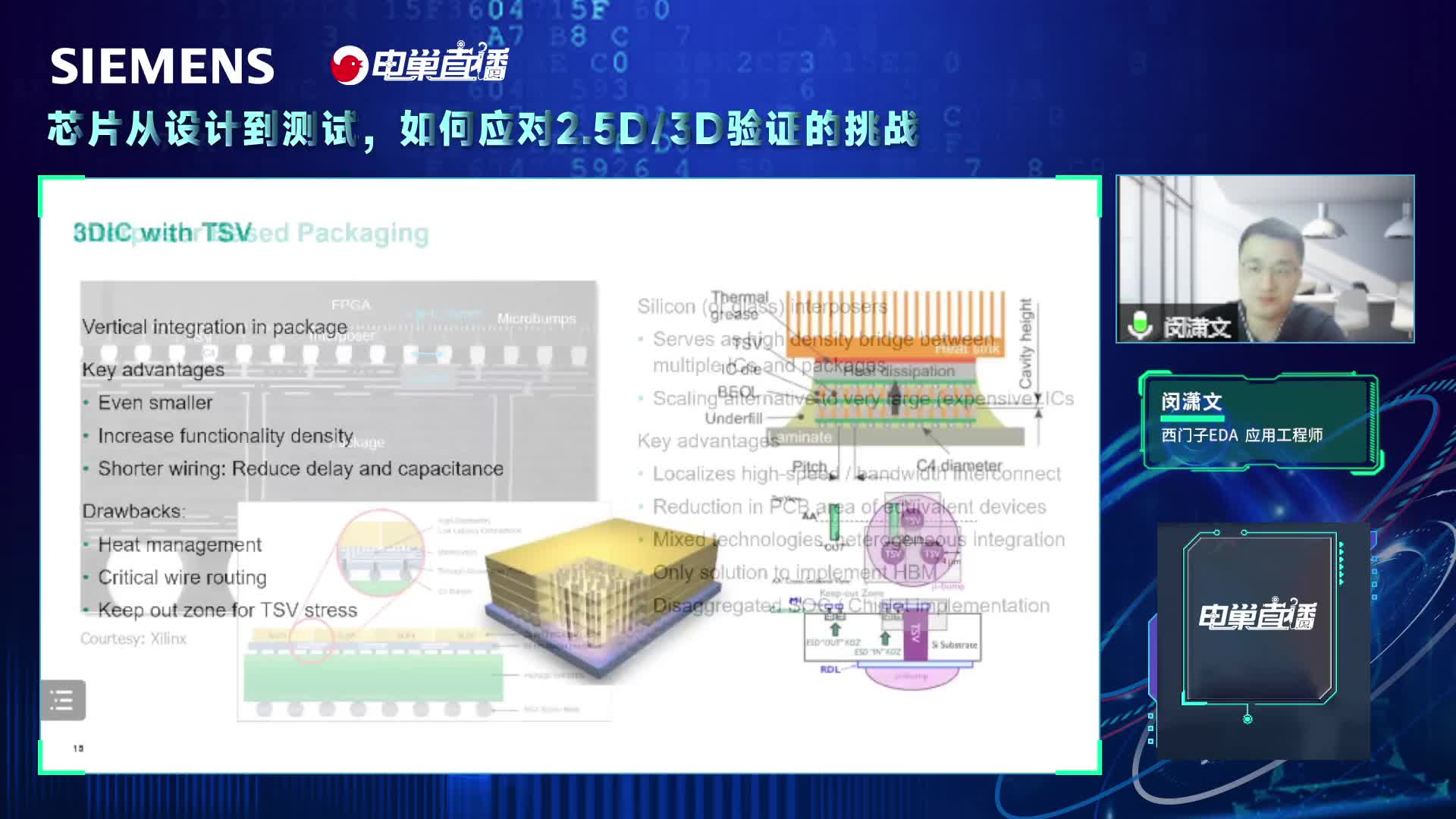

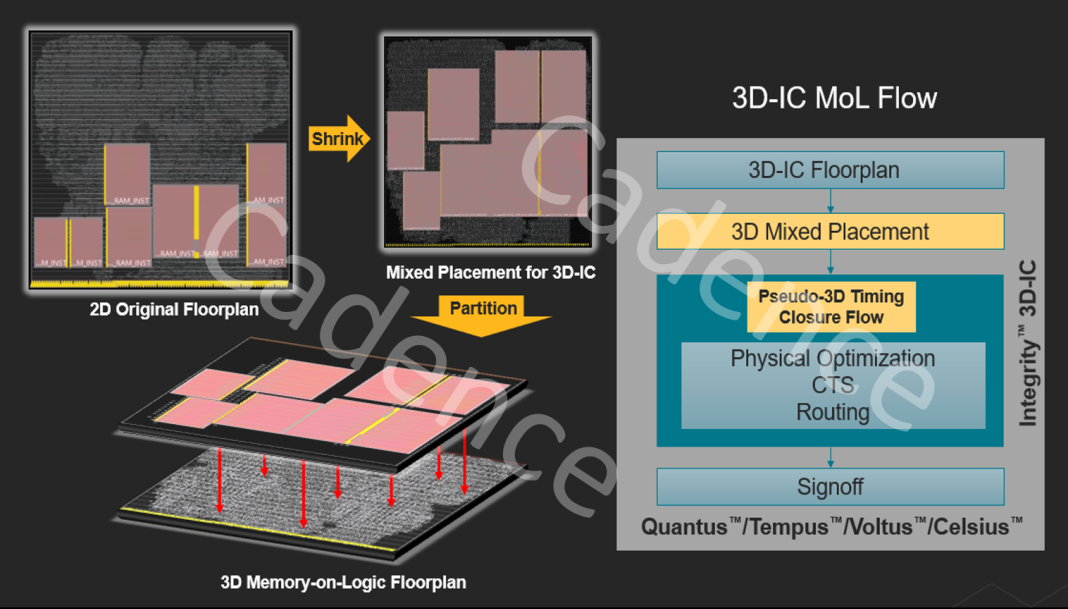

、性能更高,也因此成了新的设计主流,席卷了AI、服务器与汽车芯片等市场。但新的设计方案除了需要新一代的die-to-die的接口IP、2.5D/3D的封装技术外,也需要在EDA工具与工作流上做出创新。 西门子3D IC设计流工具 为了解决3DIC集成在设计工具上

2023-11-09 00:22:00 1275

1275 DIC 2021第四届上海国际显示技术及应用创新展览会DISPLAY INNOVATION CONVENTION & EXPO展会主题:新型显示 触手可及时间:2021年6月30-7月2日

2020-09-15 16:19:16

芯片堆叠技术在SiP中应用的非常普遍,通过芯片堆叠可以有效降低SiP基板的面积,缩小封装体积。 芯片堆叠的主要形式有四种: 金字塔型堆叠 悬臂型堆叠 并排型堆叠 硅通孔TSV型堆叠

2020-11-27 16:39:05

,使用斜杠分隔方式,比如这里小编输入了+2/-0.9。选中文字之后,我们点击工具栏中的“堆叠”选项。(2)执行结果如下图所示: 3、对角线堆叠样式: (1)输入自己所要进行堆叠操作的文字,使用“#”分隔方式

2020-04-21 15:21:11

和3DIC技术的发展,FPGA不断在加速取代ASSP和ASIC,但这还需要更多的突破,其中最大的障碍就是互联问题,需在纵向架构上“守正出奇”。

2019-09-23 07:50:27

大家好。对于我们的大学实验室,我为Nexys和Atlys板创建了运营商,可以简化在实验室环境中的处理。虽然这些仍然可以改进,但实现了一些主要目标。 - 易于存储,可堆叠设计 - 学生可以看到电路板

2019-09-26 08:25:42

labview中能实现将一个个圆堆叠成圆柱吗? 类似下图

2022-05-03 15:05:25

与堆叠仪器集成系统相比,PXI和VXI具有哪些优点和缺点?如何实现基于LAN的混合型系统的设计? 如何利用PC标准I/O简化系统通信和连通能力?

2021-04-13 06:08:55

1、什么是堆叠设计也称作系统设计,根据产品规划,产品定义的要求,为实现一定的功能,设计出合理可靠的具备可量产性的PCB及其周边元器件摆放的一种方案。2、堆叠工程师一般由结构工程师进行堆叠,有些公司

2021-11-12 08:17:17

元器件内芯片的堆叠大部分是采用金线键合的方式(Wire Bonding),堆叠层数可以从2~8层)。 STMICRO声称,诲今厚度到40μm的芯片可以从2个堆叠到8个(SRAM,Hash

2018-09-07 15:28:20

串联堆叠,可创建一个沟道长度为3μm的有效器件(图1)。 图1:将三个MOSFET串联堆叠,可提供3μm的沟道长度。 堆叠MOSFET在现代模拟设计中非常常见,但并不是没有问题。其主要问题是电容

2021-10-12 16:11:28

没有读者认识到发生在3DIC集成中的技术进步,他们认为该技术只是叠层和引线键合,是一种后端封装技术。而我们该如何去拯救3DIC集成技术?

2021-04-07 06:23:51

有两个主要组成部分 - 一个是为整个3DIC设备构建一个精确的电源模型,可以在详细的瞬态和AC Spice分析中使用,另一个是确保模型有效地反映了非常宽的响应范围,包括从板级/封装级的MHz到芯片

2017-09-25 10:14:10

各位高手。我想用labview实现多个2维数组的堆叠显示,比如将10个二维数组堆叠显示在三位空间里,且依然保留每一层的强度信息,效果类似图:

2016-10-01 14:29:49

`华尔街日报发布文章称,科技产品下一个重大突破将在芯片堆叠领域出现。Apple Watch采用了先进的的3D芯片堆叠封装技术作为几乎所有日常电子产品最基础的一个组件,微芯片正出现一种很有意思的现象

2017-11-23 08:51:12

Viterbi Compiler MegaCore Function User Guide

好东西哦。网上搜集,希望对你有用。

2006-03-25 15:40:49 32

32 Reed-Solomon Compiler

2006-03-25 15:42:49 26

26 Altera viterbi compiler

2006-03-25 15:45:58 18

18 Altera viterbi compiler v1.0 下载

2009-03-23 09:45:42 0

0 MATLAB Compiler The Language of Technical Computing:This chapter describes the MATLAB Compiler

2010-02-10 11:19:36 0

0 交换机堆叠

交换机堆叠是通过厂家提供的一条专用连接电缆,从一台交换机的"UP"堆叠端口直接连接到另一台交换机的"DOWN"堆叠端口。以实现单台交换机

2010-01-08 11:28:05 880

880 集线器的堆叠

部分集线器具有堆叠功能。集线器堆叠是通过厂家提供的一条专用连接电缆,从一台集线器的"UP"堆叠端口直接连接到另一台集线器的"DOWN"堆叠端口

2010-01-08 10:15:16 1443

1443 当大部份芯片厂商都感觉到遵循摩尔定律之途愈来愈难以为继时,3DIC成为了该产业寻求持续发展的出路之一。然而,整个半导体产业目前也仍在为这种必须跨越工具、制程、设计端并加

2011-06-22 08:51:53 261

261 当大部份芯片厂商都感觉到遵循摩尔定律之途愈来愈难以为继时,3DIC成为了该产业寻求持续发展的出路之一。然而,整个半导体产业目前也仍在为这种必须跨越工具、制程、设计端并加

2011-06-24 09:12:47 985

985 据台湾对外贸易发展协会(TAITRA)透露,芯片代工巨头台积电(TSMC)有望超过intel,在2011年底推出业内首款采用3-D芯片堆叠技术的半导体芯片产品。

2011-07-07 09:19:07 858

858 芯片堆叠封装是提高存储卡类产品存储容量的主流技术之一,采用不同的芯片堆叠方案,可能会产生不同的堆叠效果。针对三种芯片堆叠的初始设计方案进行了分析,指出了堆叠方案失

2012-01-09 16:14:14 42

42 Altera公司藉助TSMC的CoWoS整合生产及封装技术开发下一世代3DIC芯片

2012-03-23 08:31:27 991

991 2012年4月27日讯 - GLOBALFOUNDRIES今天宣布,在为新一代移动和消费电子应用实现3D芯片堆叠的道路上,公司达到了一个重要的里程碑。在其位于美国纽约萨拉托加郡的Fab 8,GLOBALFOUNDRIES已开始

2012-04-28 09:15:03 1294

1294 因应台积电明年积极布建?? 20nm制程产能并跨及3DIC封测,国内封测双雄日月光、矽品及记忆体封测龙头力成,下半年起也积极抢进3DIC封测,布建3DIC封测产能。

2012-07-30 09:08:04 1020

1020 TCL图纸PDP42U3A_DIC

2017-02-28 22:21:46 2

2 在不同的芯片或技术组合中,TSV技术还能提供更高水平的灵活度,例如采用45奈米制程的数字芯片中的芯片至芯片堆栈,以及在模拟晶圆(例如180nm)中,微机电(MEMS)组件或光传感器和光电二极管数组的堆栈,这只是其中的几个例子。

2017-04-26 11:34:40 3981

3981 CodeVision C Compiler 參考中文版

2017-09-21 09:26:29 0

0 来缩减晶方尺寸,同时也能使用先进的封装技术来实现系统小型化。 3DIC成为缩小传感器IC新解方 对于更高系统整合度的需求持续增加,这不只促使传统的组装服务供货商,也推动半导体公司开发更创新和更先进的封装技术。 最具前景且

2017-11-22 11:26:42 3

3 被称之为“堆叠硅片互联技术”的3D封装方法采用无源芯片中介层、微凸块和硅通孔 (TSV)技术,实现了多芯片可编程平台。

2019-01-03 13:20:59 3225

3225 在近日举行的英特尔“架构日”活动中,英特尔不仅展示了基于10纳米的PC、数据中心和网络系统,支持人工智能和加密加速功能的下一代“Sunny Cove”架构,还推出了业界首创的3D逻辑芯片封装技术——Foveros。这一全新的3D封装技术首次引入了3D堆叠的优势,可实现在逻辑芯片上堆叠逻辑芯片。

2018-12-14 15:35:32 7850

7850 英特尔近日向业界推出了首款3D逻辑芯片封装技术“Foveros”,据悉这是在原来的3D封装技术第一次利用3D堆叠的优点在逻辑芯片上进行逻辑芯片堆叠。也是继多芯片互连桥接2D封装技术之后的又一个颠覆技术。

2018-12-14 16:16:45 2343

2343 近日,武汉新芯研发成功的三片晶圆堆叠技术备受关注。有人说,该技术在国际上都处于先进水平,还有人说能够“延续”摩尔定律。既然3D芯片堆叠技术有如此大的作用,那今天芯师爷就跟大家一起揭开它的面纱。

2018-12-31 09:14:00 30341

30341 对全新芯片堆叠技术的全面支持确保实现最高性能的3D-IC解决方案

2019-05-18 11:28:01 3642

3642 日前,麻省理工学院助理教授Max Shulaker在DARPA电子复兴倡议(ERI)峰会上展示了一块碳纳米管+RRAM通过ILV技术堆叠的3DIC晶圆。

2019-08-05 15:08:16 2935

2935 对于我国的半导体行业来说,碳纳米管+RRAM+ILV 3DIC是一个值得关注的领域。目前碳纳米管+RRAM+ILV 3DIC是否能真正成为下一代标准半导体工艺还存在很大的不确定因素,因此在适当

2019-09-09 17:00:42 5922

5922 困于10nm的Intel也在这方面寻找新的机会,其在去年年底的“架构日”活动中,推出其业界首创的3D逻辑芯片封装技术——Foveros,Foveros首次引入3D堆叠的优势,可实现在逻辑芯片上堆叠

2020-01-28 16:10:00 3031

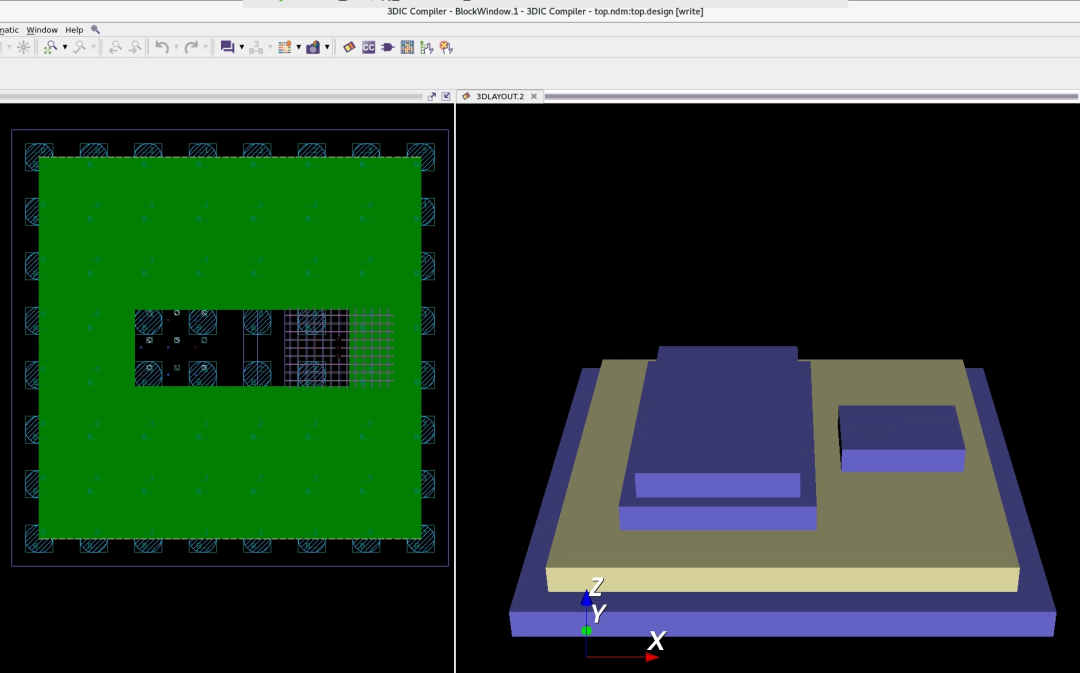

3031 新思科技的3DIC Compiler建立在一个IC设计数据模型的基础上,通过更加现代化的3DIC结构,实现了容量和性能的可扩展性。该平台提供了一个集规划、架构探究、设计、实现、分析和signoff于一体的环境。

2020-08-28 15:43:55 2457

2457 重点 ● TSMC认证基于新思科技3DIC Compiler统一平台的CoWoS和InFO设计流程 ● 3DIC Compiler可提高先进封装设计生产率 ● 集成Ansys芯片封装协同分析解决方案

2020-10-14 11:11:21 2099

2099 AD2009:3个半的DIC线DPM过时的数据Sheet

2021-05-14 12:28:34 8

8 随着摩尔定律的逐渐失效,缩小芯片尺寸的挑战日益艰巨。但随着新工艺和技术接连涌现,芯片设计规模仍在持续拓展。其中一种方式就是采用3DIC,它将硅晶圆或裸晶垂直堆叠到同一个封装器件中,从而带来性能、功耗

2021-06-09 17:46:17 1962

1962 多芯片系统设计分析的统一平台,为客户构建了一个完全集成、性能卓著且易于使用的环境,提供了从开发、设计、验证、信号完整性仿真、电源完整性仿真到最终签核的3DIC全流程解决方案。 随着芯片制造工艺不断接近物理极限,芯片的布局设计——异构集成的3DIC先进

2021-08-30 13:32:23 1506

1506 随着芯片制造工艺不断接近物理极限,芯片的布局设计——异构集成的3DIC先进封装(以下简称“3DIC”)已经成为延续摩尔定律的最佳途径之一。

2021-08-30 14:12:17 1436

1436 3DIC架构并非新事物,但因其在性能、成本方面的优势及其将异构技术和节点整合到单一封装中的能力,这种架构越来越受欢迎。随着开发者希望突破传统二维平面IC架构的复杂度和密度限制,3D集成提供了引入更多

2021-09-03 10:17:53 6458

6458 盛合晶微原名中芯长电半导体有限公司,是中国大陆第一家致力于12英寸中段凸块和硅片级先进封装的企业,也是大陆最早宣布以3DIC多芯片集成封装为发展方向的企业。

2021-10-11 14:14:51 1915

1915 新思科技3DIC Compiler是统一的多裸晶芯片设计实现平台,无缝集成了基于台积公司3DFabric技术的设计方法,提供完整的“探索到签核”的设计平台

2021-11-01 16:29:14 371

371 双方拓展战略合作,提供全面的3D系统集成功能,支持在单一封装中集成数千亿个晶体管 新思科技3DIC Compiler是统一的多裸晶芯片设计实现平台,无缝集成了基于台积公司3DFabric技术

2021-11-05 15:17:19 5826

5826 新思科技和三星晶圆厂(以下简称为“三星”)着力提升先进节点和多裸晶芯片封装的创新和效率,满足HPC、AI、汽车和5G等应用的大量需求

2021-12-08 11:08:36 1231

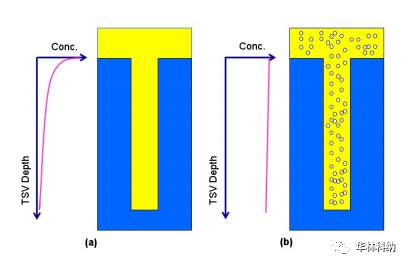

1231 直通硅通孔(TSV)器件是3D芯片封装的关键推动者,可提高封装密度和器件性能。要实现3DIC对下一代器件的优势,TSV缩放至关重要。

2022-04-12 15:32:46 942

942

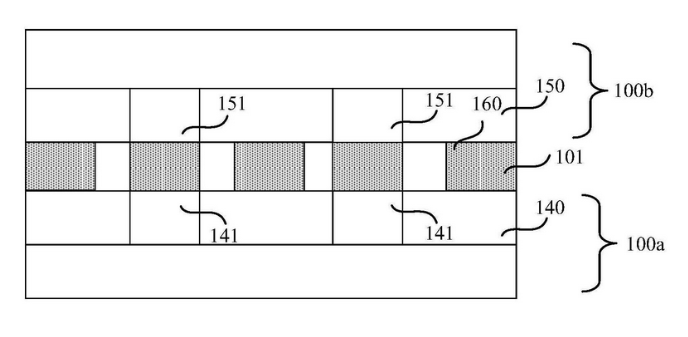

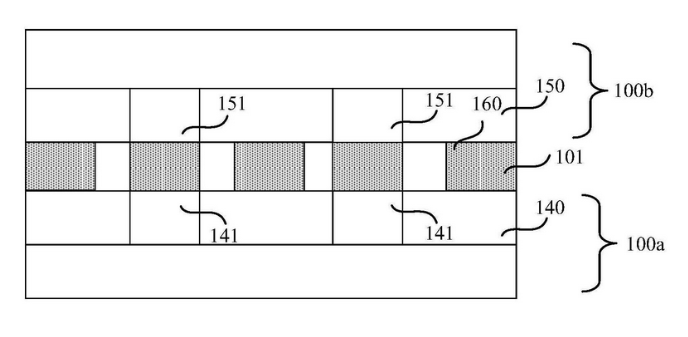

自今年4月5日华为公布芯片堆叠专利后,而过了一个月,5月6日,华为又公开了一项名为“芯片堆叠封装结构及其封装方法、电子设备”的专利,申请公布号为CN114450786A。 据国家知识产权局官网显示

2022-05-07 15:59:43 100213

100213 电子发烧友网报道(文/黄山明)近日,华为密集公布了多项技术专利,其中引人注意的是华为再次公布了两项与芯片堆叠有关的专利。为何说再次,因为就在一个月前,华为同样公开了“一种芯片堆叠封装及终端设备”的专利。多项与芯片堆叠相关专利的公开,或许也揭露了华为未来在芯片技术上的一个发展方向。

2022-05-09 09:50:20 5437

5437 堆叠技术也可以叫做3D堆叠技术,是利用堆叠技术或通过互连和其他微加工技术在芯片或结构的Z轴方向上形成三维集成,信号连接以及晶圆级,芯片级和硅盖封装具有不同的功能,针对包装和可靠性技术的三维堆叠处理技术。

2022-05-10 15:58:13 3605

3605

在芯片成品制造环节中,市场对于传统打线封装的依赖仍居高不下。市场对于使用多芯片堆叠技术、来实现同尺寸器件中的高存储密度的需求也日益增长。这类需求给半导体封装工艺带来的不仅仅是工艺能力上的挑战,也对工艺的管控能力提出了更高的要求。

2022-08-07 11:43:22 3393

3393 “芯片堆叠”技术近段时间经常听到,在前段时间苹果举行线上发布会时,推出了号称“史上最强”的Apple M1 ultra,这就是一种采用堆叠思路设计的芯片。

2022-08-11 15:39:02 9324

9324

目前有多种基于 3D 堆叠方法, 主要包括: 芯片与芯片的堆叠( D2D) 、芯片与圆片的堆叠( D2W ) 以及圆片与圆片的堆叠( W2W) 。

2022-11-01 09:52:51 1430

1430 芯和半导体2.5D/3D多芯片Chiplets解决方案

2022-11-24 16:54:08 550

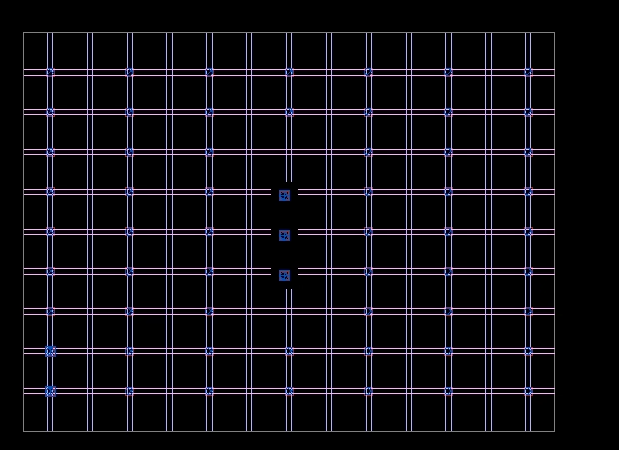

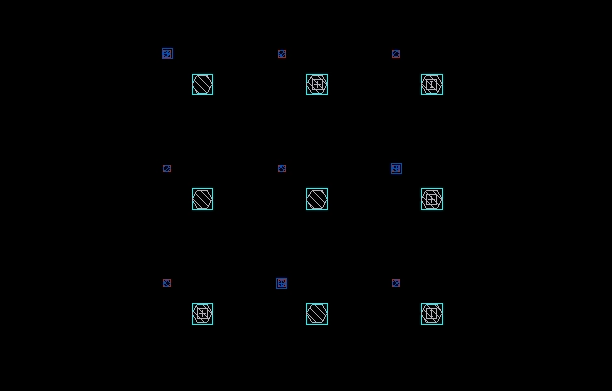

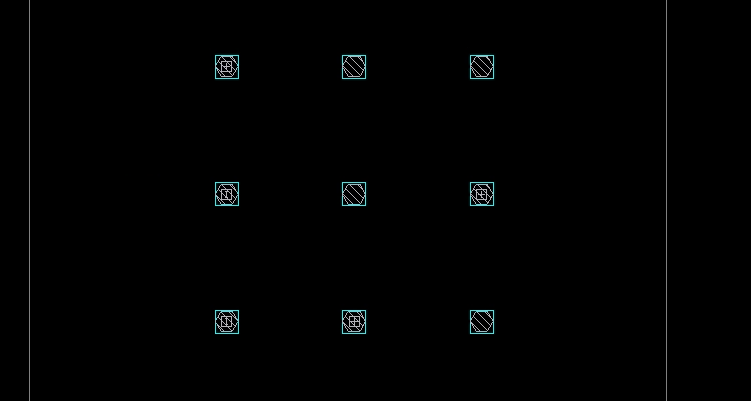

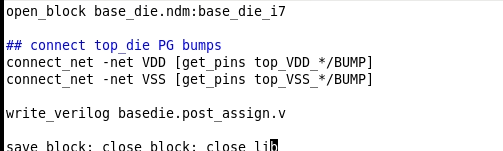

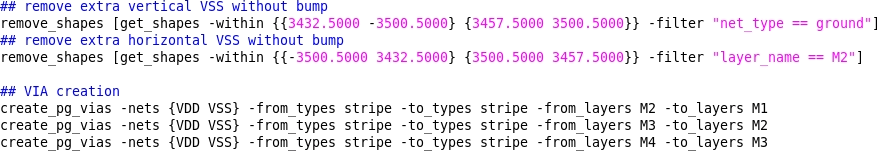

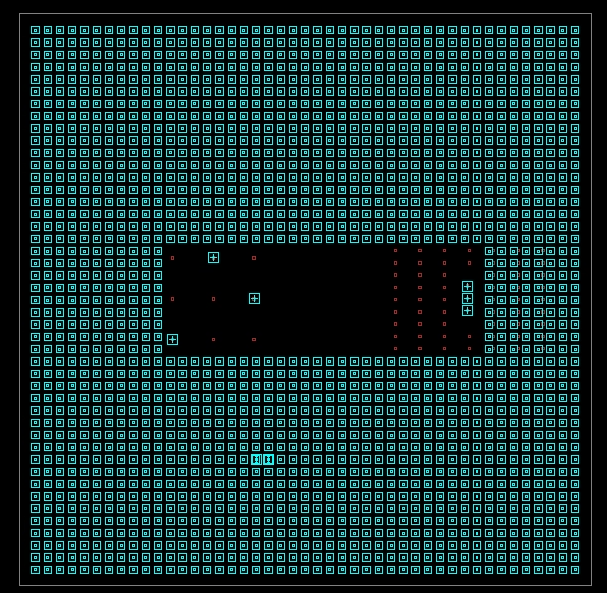

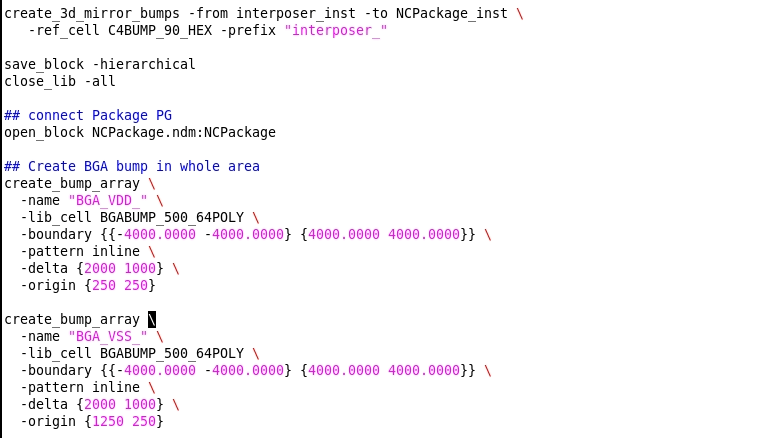

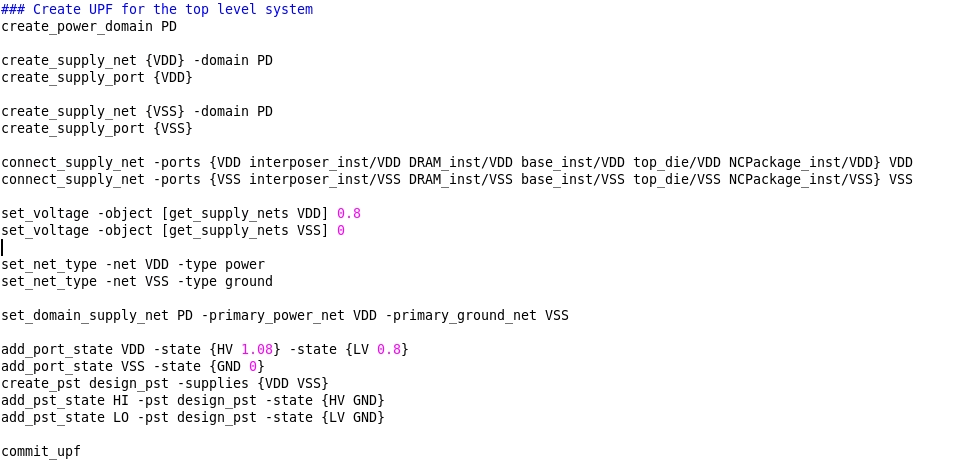

550 在没有bump library cells的情况下,3DIC Compiler 如何在GUI界面使用“pseudo” bumps 快速实现Bump Planning,流程包括: 定义bump

2022-11-24 16:58:19 863

863 在3DFabric™技术和3Dblox™标准中的合作,新思科技提供了一系列全面的、系统级的、经过产品验证的解决方案,助力共同客户能够满足复杂的多裸晶芯片系统对于功耗和性能的严苛要求。 经过流片验证的新思科技3DIC Compiler是该解决方案中的一个关键技术。作为统一的多裸晶芯片协同设计和分析平台,

2022-12-01 14:10:19 486

486 为什么芯片可以进行堆叠呢?这里面我们讲的主要是未经过封装的裸芯片。曾经有用户问我,封装好的芯片可不可以进行堆叠呢?一般来说是不可以的,因为封装好的芯片引脚在下表面直接焊接到基板上,而裸芯片的引脚一般在芯片上表面,通过键合的方式连接到基板。

2023-02-11 09:44:18 1596

1596 目前阶段开始有同构集成。国际上已经有异构集成CPU+GPU+NPU的Chiplet,其他功能芯片则采用次先进工艺制程的芯粒,感存算一体属于3DIC的Chiplet这样的方案可以灵活堆出算力高达200tops。

2023-02-14 15:00:00 2011

2011 HPC、AI、数据中心以及汽车自动化等应用对于高效能和高性能算力需求持续增长,单芯片系统实现方案从设计、实现、生产制造、可靠性等各个方面都遇到了严峻的技术挑战。

2023-02-15 16:01:39 1488

1488 下的“存储墙”、“功耗墙”问题。存算一体将存储与计算有机融合以其巨大的能效比提升潜力,有望成为数字经济时代的先进生产力。存算一体芯片设计迭代和投产的效率至关重要,如何能够设计出更低损耗、更低噪声、更低能耗,并符合信号完整性、电源完整性指标性能的存算一体芯片,从而提高存算一体芯片的设计效率呢?

2023-02-24 09:34:28 2954

2954 M3T-NC30WA V.6.00 C/C++ Compiler 用户手册 (C/C++ Compiler Package for M16C Series and R8C Family)

2023-04-17 19:32:55 0

0 R32C/100 Series C Compiler Package V.1.02 C Compiler 用户手册

2023-04-19 19:24:26 0

0 M3T-NC308WA V.5.42 C Compiler 用户手册 (C Compiler Package for M32C Series)

2023-04-19 19:25:01 0

0 原文标题:谁说3DIC系统设计难?最佳PPAC目标轻松实现 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-04-21 02:05:04 323

323

原文标题:下周五|谁说3DIC系统设计难?最佳PPAC目标轻松实现 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-04-21 19:30:01 273

273

原文标题:仿真分析:3DIC全流程解决方案的第一步 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-05-11 20:16:30 425

425

原文标题:下周五|仿真分析:3DIC全流程解决方案的第一步 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-05-11 20:16:35 276

276

原文标题:本周五|仿真分析:3DIC全流程解决方案的第一步 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-05-11 20:16:38 272

272

原文标题:1+1>2?3DIC+Metis助力实现协同设计和仿真分析 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-05-11 20:16:40 272

272

原文标题:下周五|1+1>2?3DIC+Metis助力实现协同设计和仿真分析 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-05-11 20:17:25 292

292

RH850 Family C Compiler Package CC-RH V1.02.00 用户手册: Compiler

2023-05-15 19:47:57 0

0 3DIC设计的重要性日益凸显。当今市场对AI应用的需求在不断增加,而摩尔定律的步伐却在放缓,这使得芯片开发者不得不寻求其他类型的芯片架构,以满足消费者和领先服务提供商的预期。3DIC设计并不是简单

2023-06-27 17:35:01 746

746 RH850 Family C Compiler Package CC-RH V1.02.00 用户手册: Compiler

2023-07-12 18:40:53 0

0 芯片技术领域的应用概要,用于简化芯片堆叠结构及其形成方法、芯片封装结构、电子设备、芯片堆栈结构的制造技术。该芯片的堆叠结构至少包括两个堆叠的芯片,每一个芯片包括电线层,电线层设有电具组。

2023-08-09 10:13:42 1369

1369

新思科技经认证的多裸晶芯片系统设计参考流程和安全的Die-to-Die IP解决方案,加速了三星SF 5/4/3工艺和I-Cube及X-Cube技术的设计和流片成功。 新思科技3DIC

2023-09-14 09:38:28 839

839 长期以来,个人计算机都可以选择增加内存,以便提高处理超大应用和大数据量工作的速度。由于3D芯片堆叠的出现,CPU芯粒也有了这个选择,但如果你想打造一台更具魅力的计算机,那么订购一款有超大缓存的处理器可能是正确的选择。

2023-10-15 10:24:23 371

371

交换机为什么要堆叠?有哪些设备可以堆叠?如何建立堆叠? 交换机的堆叠是一种将多个交换机连接在一起管理和操作的技术。通过堆叠,管理员可以将一组交换机视为一个虚拟交换机来进行集中管理和配置,提供灵活性

2023-11-09 09:24:35 1140

1140 作为全球领先的互联产品和解决方案公司,奇异摩尔期待以自身 Chiplet 互联芯粒、网络加速芯粒产品及全链路解决方案,结合智原全面的先进封装一站式服务,通力协作,深耕 2.5D interposer 与 3DIC 领域,携手开启 Chiplet 时代的新篇章。

2023-11-12 10:06:25 456

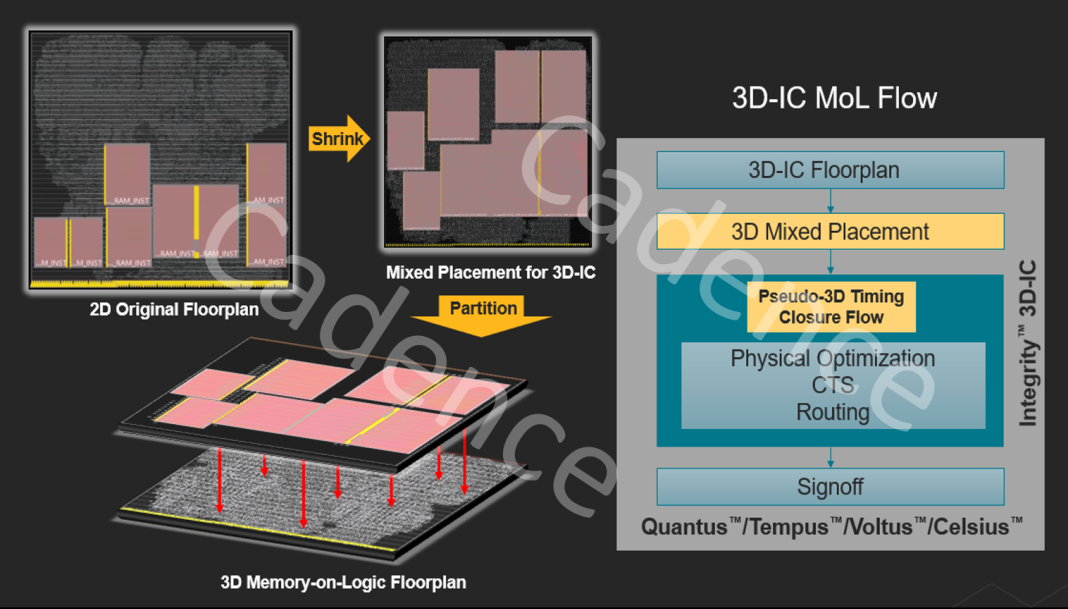

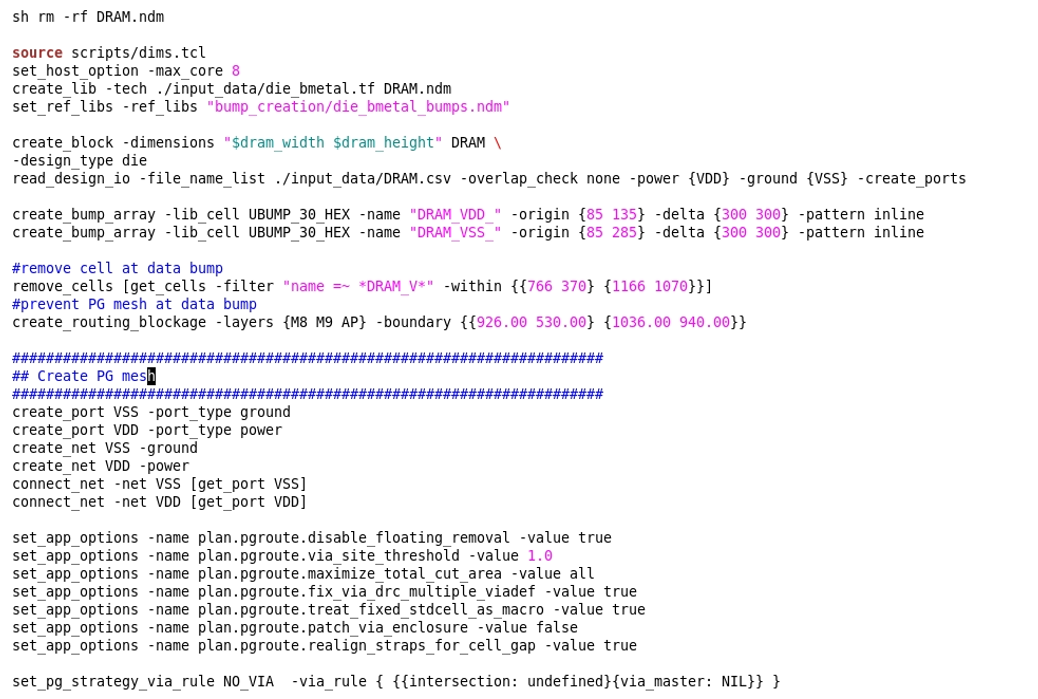

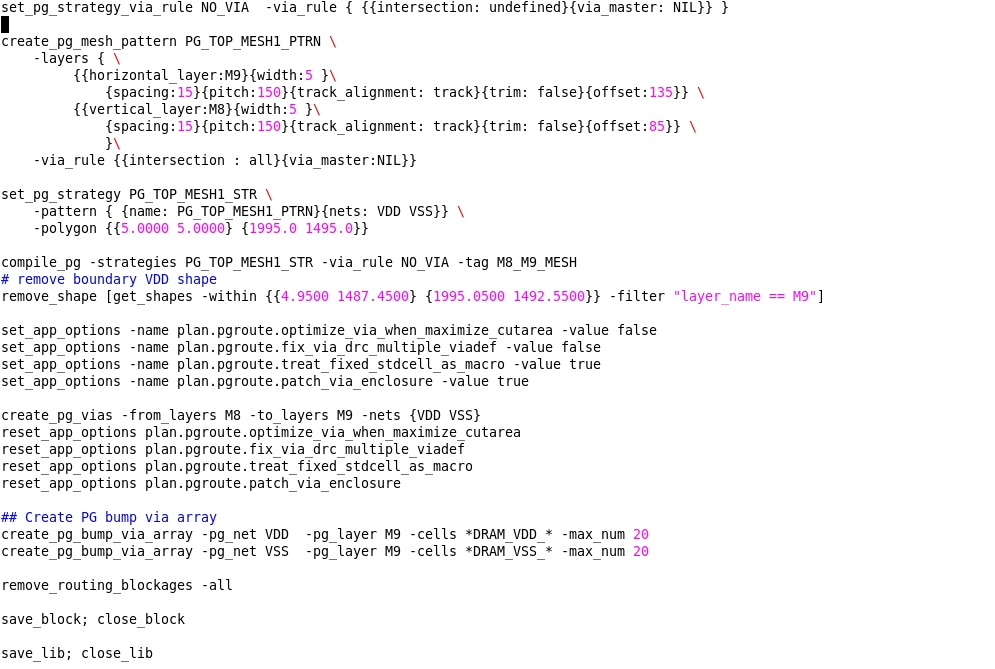

456 3D-IC 设计之 Memory-on-Logic 堆叠实现流程

2023-12-01 16:53:37 255

255

TSV是2.5D和3D集成电路封装技术中的关键实现技术。半导体行业一直在使用HBM技术将DRAM封装在3DIC中。

2023-11-27 11:40:20 211

211

利用Multi-Die系统能实现异构集成,并且利用较小Chiplet实现更高良率,更小的外形尺寸和紧凑的封装,降低系统的功耗和成本。Ansys半导体产品研发主管Murat Becer指出:“3DIC正在经历爆炸性增长,我们预计今年3DIC设计的数量将是去年的3倍左右。”

2023-11-29 16:35:48 268

268 本文介绍了堆叠线的定义、分类、作用以及与光纤线的区别,并提供详细的堆叠线接法和相关问题的解答。堆叠线是一种用于连接网络设备的高性能数据线缆,通过在设备之间建立逻辑连接,实现设备的堆叠和集中管理。

2024-01-08 13:43:04 230

230 新思科技3DIC Compiler集成了3Dblox 2.0标准,可用于异构集成和“从架构探索到签核”的完整解决方案。

2024-01-12 13:40:50 232

232

什么是交换机堆叠?有哪些设备可以堆叠?如何建立堆叠? 交换机堆叠是指将多个交换机通过特定的方法连接在一起,形成一个逻辑上的单一设备。堆叠可以实现多交换机的集中管理和统一配置,提供更高的可靠性和性能

2024-02-04 11:21:47 379

379 ; 新思科技广泛的高质量 IP组合降低集成风险并加快产品上市时间,为采用Intel 18A 工艺的开发者提供了竞争优势; 新思科技 3DIC Compiler提供了覆盖架构探索到签收的统一平台,可实现采用

2024-03-05 10:16:59 84

84

电子发烧友App

电子发烧友App

评论