介绍

深度亚微米技术的进步,以及增加多种功能以降低成本,结合现有操作规模,意味着SoC的设计变得更加复杂。

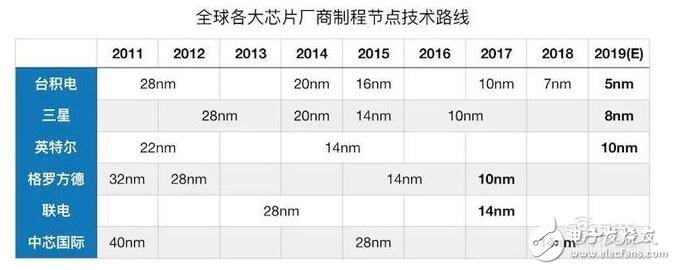

低于16纳米工艺节点的最大驱动因素是这些先进节点更高的晶体管密度所带来的功率下降和性能提高。然而,这样做会给物理实现和时序/功率收敛带来挑战。特别是高速IP,如SerDes、DDR、PCIE在大型SoC中的集成,需要仔细的floor planning,以减少项目时间,并实现定时/功率签收。在这篇文章中,我们将探讨由于5纳米技术以及SoC中新的额外功能而带来的新挑战。我们将展示解决floor planning和时序问题的方法,以减少物理实施的迭代。

方法

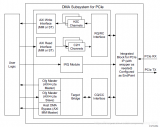

大型、复杂的IP集成的实施需要一种方法,以有效地完成 floorplansignoff 标准,并在后期阶段防止大量的时序违规。

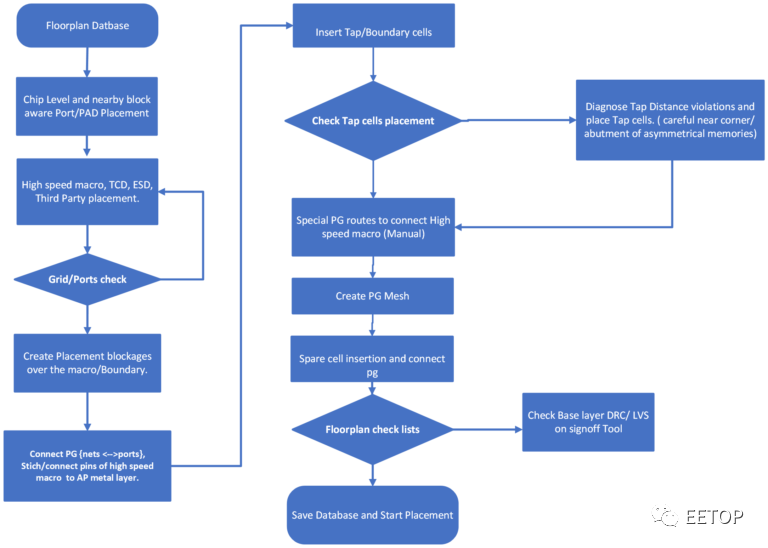

图 1:Custom FloorplanMethodology

5nm 物理设计的挑战

沿着从 SoC 到高级封装技术(如 InFo/Feveros/X-Cube)的路径,需要一种整体方法来同时解决项目的规划、编辑和优化环境问题。以及向后考虑决策路径的影响。例如,通过在工艺早期迭代放置凸块(bump )、PAD 和macros,可以缩短周转时间。

另一个在流程需要早期考虑和规划的是放置和布线之前的热效应,以便通过设计出可能导致故障的热点来提高产量和可靠性。例如,以高密度封装的标准单元会产生热点。这是因为,在14/16纳米节点,使用三到四个鳍片来为每个栅极提供结构稳定性,但在7纳米以下,使用了两个。这些都是较高的,以补偿鳍片数量的减少,并仍然提供所需的加固。然而,应注意标准单元的放置,因为被电介质(栅极氧化物)包围的鳍片具有较差的导热性,因此不能像预期的那样进行散热,从而产生一个热点。因此,在早期阶段进行功率分析(动态/静态)有助于防止在后期的功率signoff阶段出现热点意外。

最后,在较低的几何形状下,工艺和电压变化强度更高。为了解决这个问题,由于噪声和转换要求,PT-ECO signoff通常需要对大型复杂块进行 12 次以上的迭代。

集成高速模块的挑战

由于模拟团队对硬IP的不断改进,部分硬IP具有较高的变动性。这可以通过使用为不同设计阶段量身定做的模型来解决,随着我们接近流片,模型的复杂程度和完整程度会越来越高。在这个过程中,尽快获得IP交付物清单对迅速和成功的整合至关重要。

最后,Floorplanning、DFT 集成、自定义时钟树和时序/功率 signoff 的设计复杂性都需要脚本知识和基本的 IP 理解来调整实施。

Floorplan挑战

在最近的设计中,代工厂提供了一个multi-height库,最初,很难通过网格检查。问题是我们使用高效能库来实现我们的设计,但是第三方 IP 位于高性能库上。因此,两种库类型的放置必须在最小公倍数 (LCM) 行上。问题是,我们正在使用一个高效的库来实现我们的设计,但第三方IP是在高性能库上。因此,这两种库类型必须放置在最小公共多行(LCM)上。

需要注意的是:

避免在模拟信号路径的特殊区域插入分接单元和边界单元。

Power Grid (PG) 连接对于多电源域设计以及模拟 VDD 以及第三方 IP VDD 非常重要。

连接 PG 网络/引脚必须根据模拟团队/第三方 IP 可交付成果定义的指南。

根据代工厂定义的功率钳位实现规则连接 TCD/ESD IP。

插入备用单元后需要进行合法性检查:网格检查负责 IP 放置的合法性。

在芯片级集成块时,集成检查符合顶层floorplan DRC。

终端/端口放置检查,因为这是初始设计集成中的一项重要检查。

PG 设计规则检查 (DRC),例如 PG Via 和电源条布线,加上宏到宏和宏到边界间距规则检查以避免 DRC。

Floorplan 规划目标

这是为了有一个干净的设计规则检查 (DRC) 和布局与原理图 (LVS) 设计,遵循设计实施指南以及时序/拥塞感知宏布局。

这些是如何通过改进floorplan来实现这一目标的阶段。注意,此示例中使用了 Synopsys Fusion编译器。

1、由于第三方IP有多个供应商,需要创建网格,因此生成网格提供了互连的统一性:

create_grid-type block -x_step $cell_site_pitch -y_step $cell_row_pitch -orientations “R0MX” Macro_wrapper set_block_grid_references-grid [get_grids Macro_wrapper ] -design Macro_Wrapper

set_snap_setting-class macro_Cell -snap block -user_grid Macro_wrapp

## 宏封装器需要对齐到 7.752um、9.576um,它是单元站点 0.051 和单元行高 0.028 的倍数(1 个轨道距离)

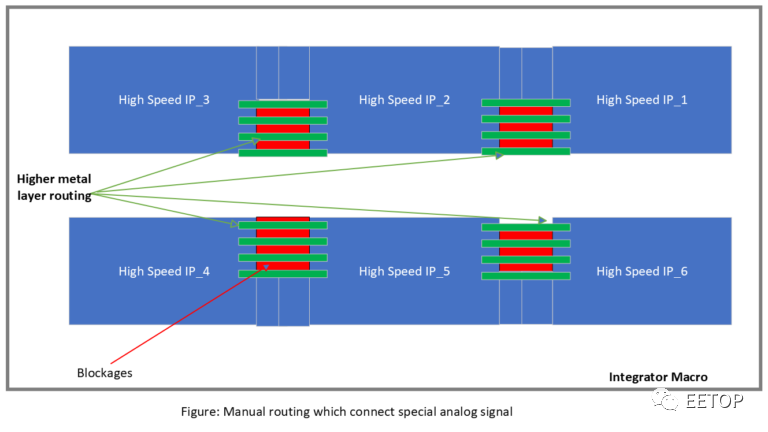

2、当您进行floorplan时,您需要手动对高速信号进行布线。您将需要通过使用在该区域上创建阻塞来避免任何布局或布线

· create_routing_blockage

· create_placement_blockage

例如:

· create_placement_blockage -name $blk_name -boundary [get_attr [get_attr$blk_poly poly_rects] point_list]

· create_routing_blockage -name SNRG#${blk_name} -boundary [get_attr[get_attr $blk_poly poly_rects] point_list] -layers [get_layers -filterfull_name!~*G*] -zero_spacing

图 2:高速宏上的块和信号路由

3、Power Grid (PG) 连接要求 PG 网状路由遵循实现定义的预连接命令。因此,我们需要连接模拟 PG 端口和 BUMP 连接以及数字电源/接地连接。

示例:

Connect_pg_net –net VDD [get_pins BUMPS_VDD_*/BUMP]

Connect_pg_net–net VSS [get_pins BUMPS_VSS_*/BUMP]

#特殊PG连接

foreach v“VDDAVSSA VDDM”{

Connect_pg_net–net $v [get_pins High_speed_IP_*/[string tolower $v]]

Connect_pg_net–net $v [get_pins Monitor*/[string tolower $v]]

}

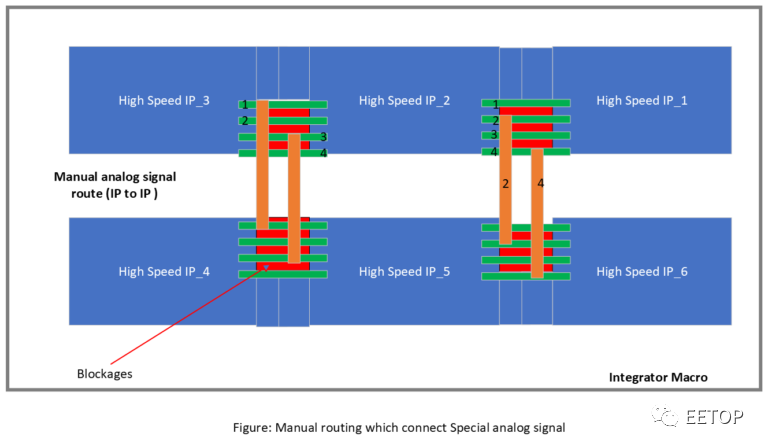

4、当您没有足够或不完整的库交换格式 (LEF) 但必须检查块级和芯片级布局与原理图 (LVS) 时,模拟团队定义的在块级连接的额外信号和特殊连接可能具有挑战性。

例子:

图 3:连接特殊模拟信号的手动路由

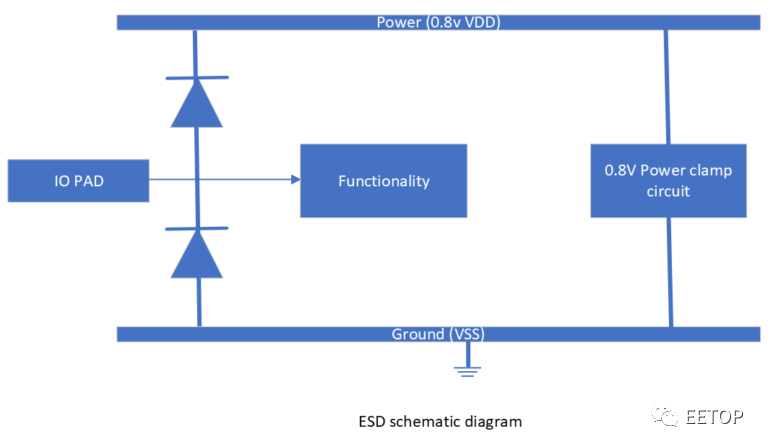

5、需要进行 ESD 单元和 TCD(Test-key Critical Dimension)检查。需要静电放电宏来保护高速模拟宏。TCD单元用于监控最小线宽等关键尺寸。同时检查单元的关键尺寸以确保制造过程中的布局均匀性以提高良率。

注意:我们将 ESD 单元放置在 Hard IP 附近,并提供与 Hard IP 所需的电压相同的电压以提高效率。

图4 示意图

6、终端/端口放置检查。这些是用于发现错误的平面布置图的常见且简单的检查。

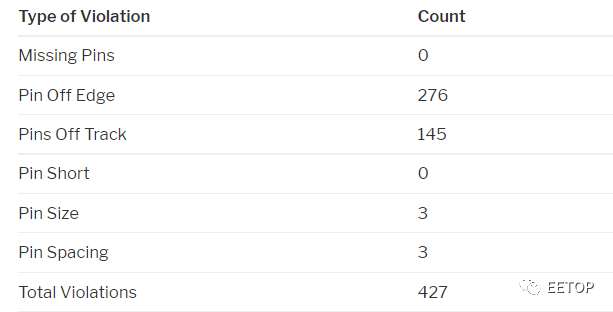

示例:要检查的违规行为

7、Power Grid设计规则检查:写出 PG DRC 报告并将实施工具 PG DRC 与 ICV/Calibre 的平面图signoff(规则甲板感知)DRC 进行比较。如果 DRC 违规,例如非法重叠、宽度不足、最小金属宽度最小金属面积、非法形状或最小金属边缘,请尝试通过插入脚本调试 PG 网格脚本和手动 PG。

注意:在暂定signoff迭代期间进一步执行下一步之前,应该清理 PG 上的 Shorts 和 Opens。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论