编者按:

晶圆清洗是半导体制造工艺中最重要、最频繁的工序,并且随着尺寸的缩小、结构的复杂化,晶圆对杂质含量的敏感度也相应提高。清洗质量的好坏将直接影响到器件的成品率、性能和可靠性,国内外各大公司、研究机构等对清洗工艺的研究从未停止,但一些特殊问题仍未得到彻底解决。本文介绍了一些晶圆清洗方案以及更先进制程中晶圆清洗遇到的诸多挑战与待解决的问题。

以下为原文:

Wafer cleaning, once a rather mundane task as simple as dipping wafers in cleaning fluid, is emerging as one of the top major engineering challenges for manufacturing GAA FETs and 3D-ICs.

With these new 3D structures — some on the horizon but some already in high-volume manufacturing — semiconductor wafer equipment and materials suppliers in the wet cleaning business are at the epicenter of a push for increased yield and reliability. Cleaning logic and memory structures used to be straightforward. But starting with finFETs, and moving next into gate-all-around (GAA) structures, as well as advanced DRAM capacitors and 3D NAND, cleaning has entered a third — and not always visible nor measurable — dimension.

Cleaning steps are found throughout the semiconductor manufacturing process, and there are hundreds of them. They involve not just cleaning, but making sure the surface is prepared for the next step in photoresist, post-etch and implant strip, general cleaning, and backside cleaning for multiple patterning and EUV, notes Sally-Ann Henry, director of business development at ACM Research. What was once a bath in a wet bench has evolved into innovative single-wafer cleaning solutions for the advanced nodes.

“As new materials and process architectures are introduced into an already complex manufacturing process, a specialized cleaning process is the key to further innovation,” said Brian Wilbur, director, Semiconductor Products Diversification at Brewer Science. He described the company’s customized approach to cleaning. For instance, Brewer’s selective surface modification materials can provide high selectivity to metals, polymers, dielectrics, etc., to enhance cleaning solutions.

“As scaling continues, features are getting smaller and more complex, and chipmakers are exploring new materials. This is making achieving precise, uniform cleaning more challenging,” said David Kretz, senior director of key account technology for Lam Research’s Clean Product Line. “New approaches are needed for advanced next-generation logic, DRAM, and NAND. As cleaning processes are also used multiple times in the chip-making process to remove yield-limiting residue and defects, the need for cost-effective, highly efficient processes is even greater.”

The market for Wet Wafer Processing Systems is slightly more than $5B, according to TechInsights. The top three companies — in order: Screen Semiconductor Solutions, TEL and Lam — account for about 75% of the market. The next three — Semes, Naura, and ACM Research — account for another 20%. Despite the dominance of the top three, Risto Puhakka, president of VLSI Research (now part of TechInsights), describes the marketplace as “fairly competitive.” Like much of the equipment market, the wet clean equipment market saw big upswings over the last couple of years, reaching growth of more than 40% in 2021. The firm sees it dropping to -7% in 2023, but picking up again with an AAGR in 2022 to 2027 of 8.3%.

3D structures

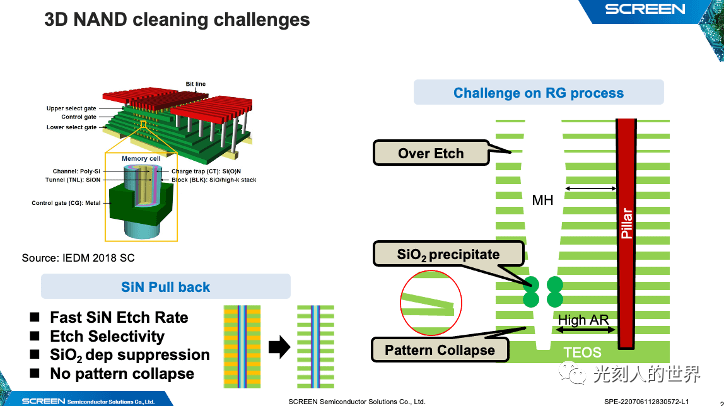

The challenges are somewhat different for logic versus memory structures. At Semicon West 2022, Ian Brown, vice president, engineering at Screen, gave a detailed talk entitled, “Unique Challenges Associated with Manufacturing 3D Devices and Structures Including GAA, 3D DRAM, and 3D NAND and Wafer Cleaning Technology in 3D Integrated Circuit Devices.” (The video is available here.)

Consider logic devices. While cleaning for finFETs in high-volume manufacturing no longer presents any particular difficulties, the impending move to GAA structures — first nanosheets and later forksheets — is rife with challenges.

“The big challenge is the hidden surfaces,” said Brown. “How do I clean etch a surface I cannot see?” The confined, hidden vertical surfaces are especially tough. In nanosheets, six vertical surfaces are hidden, and in forksheet FETs that number rises to sixteen.

New materials also are being added, which raise complications for selectivity. The industry is looking at new wet chemistry options, vapor etch, or some combination therein.

But with the arrival of nanosheets, Brown said the new consideration is pattern collapse. This phenomena was encountered previously with 3D NAND, so some of that learning can be applied to the new logic structures.

Fig. 2: New logic structures will require new cleaning solutions. Source: Screen Semiconductor/SEMI

In memory structures, both 3D NAND and deep DRAM capacitors present challenges. In 3D NAND, the number of cell layers keeps increasing. Micron recently announced it has reached 232 layers. That makes etching uniformity down the pillars very critical. “You know, it’s very easy to over-etch these things because you’re targeting a uniform edge top to bottom,” Brown observed. “And the performance of these devices requires a uniform edge in the vertical direction.”

A lot of work has been done over the last five years, but this remains difficult. “As part of the scaling of 3D NAND, the aspect ratio of these horizontal lines is getting more challenging,” he said. “And even today, we have pattern collapse in the horizontal direction.

While the industry has long dealt with vertical pattern collapse, the challenge is now the aspect ratio in the horizontal direction. The industry is working on solving that problem to bring this technology into high-volume manufacturing.

Fig. 3: 3D NAND poses new cleaning challenges. Source: Screen/SEMI

Defect removal

Defect removal was once just a case of etching the surface and soaking the wafers in a wet bench bath, releasing the particles so they floated away. That cost-effective approach worked up to around 90nm, and it had extremely high throughput. However, after 90nm, other solutions were also needed. Wafers were cleaned individually using a dual-fluid spray system. As particles became smaller, more dispersed, and harder to detach, the spray condition was tuned. But that only will go so far before the spray pressure causes structural damage.

Furthermore, the tiny spray droplets are still about a micron in size — often twice the size of the trenches they need to clean in advanced 3D structures. And with GAA structures, there is no line of sight, so the sprays can’t even access hidden surfaces.

Researchers in the industry are now looking at polymers to help remove particles. A polymer film is spun on and then peeled off away in a structured fashion, taking particles with it. Screen’s version of this is called Nanolift.

Backside wafer contamination and wafer warping also have become general issues in advanced technology nodes. Particles left on the back of the wafer can throw off lithography.

Prior to 65nm, a popular wet cleaning technology was megasonics, which uses very high frequency sonic waves to create oscillating bubbles that gently scrub the structure. But after 65nm, the industry moved away from megasonics, because popping bubbles can damage delicate structures.

ACM Research brought megasonics back to the fore a few years ago with the introduction of highly controlled bubbles, making it appropriate for the current range of advanced structures with hard-to-reach areas. The Smart Megasonix technology allow chemicals to enter deep holes in 3D structures, followed by the company’s hot IPA vapor dryer. The success is in the numbers. ACM posted nearly 75% year-over-year growth from 2020 to 2021. It’s Space Alternated Phase Shift (SAPS) technology employs alternating phases of megasonic waves to deliver megasonic energy to flat and patterned wafer surfaces in a highly uniform manner on a microscopic level. The bubbles are allowed to burst, but in a very controlled way, so they remove random defects across the wafer much more efficiently than conventional jet spray processes, according to the company.

For even more delicate structures, ACM’s Timely Energized Bubble Oscillation (TEBO) technology enables precise, multi-parameter control of bubble cavitation during megasonic cleaning by using a sequence of rapid pressure changes to force bubbles to oscillate in specific sizes and shapes. And because these bubbles oscillate but don’t burst, TEBO technology avoids feature damage, making it a good fit for advanced 3D structures and devices with very high aspect ratios.

Drying

After each cleaning step, there is a drying step. In advanced 3D structures, that drying step creates greater risks of pattern collapse. In logic, the risk occurs in post STI etch, post poly etch, nanosheet release, and nanowire release. In 3D NAND, the risk of collapse comes during the silicon nitride pullback used to create what looks like a “staircase.”

DRAM capacitors are currently the biggest challenge due to the aggressive aspect ratios.

Drying processes using spin, isopropyl alcohol (IPA), and some N2 drying carried the industry through the 2D epoch. But advanced 3D structures now rely on more and more IPA drying steps. While this is not a new process, says Brown, said more IPA drying creates greater volatile organic compound (VOC) emissions from fabs. Most of the cleaning vendors and suppliers are now tackling that in partnership with their customers.

Currently for finFETs, IPA drying with surface modification is the state-of-the-art. But with more advanced 3D structures, the surface tension of the liquid can increase the risk of pattern collapse. The next option is sublimation, which eliminates the liquid phase transition altogether by going directly from a solid to a gas.

The next drying option beyond sublimation is super-critical carbon dioxide (SC-CO2), in which the properties of the CO2 are midway between a gas and a liquid. While it is currently in use by some chipmakers, it is a relatively slow process that involves much higher pressure and energy for heating — all adding up to much higher costs. Brown reckons that the ongoing work to extend IPA drying and sublimation ultimately will prove more cost-effective for most HVM.

Etch uniformity

In 2D, uniformity was a question of within-wafer or wafer-to-wafer. But in 3D NAND, the uniformity of the etch creates the gate, so the device performance is very strongly dependent on etch uniformity. The etch at the top, middle and bottom needs to be uniform. A straight profile is required for the liner and recess metal. “These are fun problems to work on,” and some of the industry’s best minds are working on it, Brown said.

There are a few approaches to improving wet etching. The mass transport on the emulsion tools can be improved, or the switch can be made from immersion tools to single-wafer tools. Other alternatives include vapor etch or a combination of wet and vapor etch. To study the controlling of wet chemistry in narrow spaces, the industry has turned to advanced simulation to understand the fundamentals of the processes. The chemical suppliers also are devising creative solutions to enhance control.

Environmental concerns

Companies in the cleaning equipment and materials business are on the front line of environmental and sustainability concerns, so are looking for ways to reduce the chemical and water usage as well as the exhaust emissions of their equipment.

TEL and Screen are among those that have joined imec’s Sustainable Semiconductor Technologies and Systems (SSTS) research program, which supports the semiconductor industry in reducing its carbon footprint.

All the major players are looking for ways to reduce sulfuric acid use (one of the most widely used chemicals in the industry), as well as other chemicals. Screen, for example, has developed a sulfuric peroxide mixture (SPM) reclaim function on their single-wafer SU-3300 platform, where the 70% of the dispense volume of H2SO4 can be reclaimed, and an optional exhaust recirculation system can reduce emissions by 65%. The company is targeting a 20% reduction in greenhouse gas emissions from the use of sold products by 2030.

Chipmakers also are doing their part to decrease the environmental footprint of advanced structure cleaning processes. UMC, for example, has been working with chemical suppliers to develop greener, less toxic chemicals, many of which have now been deployed in their fabs.

“This will continue to be challenging as fabrication technologies become increasingly complex, customers’ designs become more sophisticated, and new materials are introduced,” said Chun-lung Chen, a director in UMC’s Technology Development Module Division who oversees advanced development of etching and cleaning processes. “Enhancing the efficiency of cleaning solvents and reducing the environmental impact of chemicals used in the cleaning processes used to be viewed separately, but the two challenges are converging. Whether required by customers, regulatory requirements, or internal ESG targets, the trend is moving toward greener solutions and less waste.”

This represents a big shift for foundries. “At UMC, we first focus on reducing etching waste, or adjusting the residue composition so that it is easier to remove,” he said. “We then work on optimizing the formula, concentration, and temperature of solvents in order to achieve greater cleaning efficiency. More wafers can be produced using the same amount of chemicals, which brings down costs and generates less hazardous waste.”

The metrology gap

“If you can’t measure it, how well do you know how you’re performing?” asks Brown. Trying new solutions during the development process then having to wait days for a SEM to come back and tell them if they are on the right track is frustrating.

Mark Thirsk, managing partner at Linx Consulting, calls it the metrology gap. “Metrology systems are not able to measure the contamination levels and particle sizes that are critical,” said Thirsk, whose company provides strategic consulting and market analysis services to chemical, gas and materials suppliers in the electronics supply chain. Linx puts the “formulated cleans” market — the chemicals used to remove residues post-etch and post-CMP — at $560 million, with a CAGR of 5% through 2025.

A contaminant of just a few nanometers won’t show up on standard in-line metrology equipment. It requires a SEM image to find it, which is not practical in a high-volume manufacturing environment, Thirsk noted. “We’re asking the cleaning companies or the chemical companies or the equipment companies to control beyond where we can measure,” he said. And that’s a problem that’s yet to be solved.

For its part, KLA points to solutions for identifying contaminants on unpatterned wafers for wafer and process tool qualification, on patterned wafers for inline monitoring of after clean processes, and to chemistry process control products used to qualify the incoming chemicals. “KLA works in close collaboration with our customers and partners across the semiconductor ecosystem to understand their next-generation challenges,” said Ming Li, senior marketing director of the Surfscan and ADE Division at KLA. “This information drives our technology roadmap, so that we are producing products capable of addressing chip manufacturers’ most critical challenges at the right time.”

Conclusion

Cleaning is critical to yield and reliability. New 3D structures have added many new challenges. Leaders in cleaning technologies are working on innovative solutions, but some particular problems, like the lack of the line-of-sight and the metrology gap, remain unsolved.

编辑:黄飞

电子发烧友App

电子发烧友App

评论