每个半导体产品的制造都需要数百个工艺,泛林集团将整个制造过程分为八个步骤:晶圆加工-氧化-光刻-刻蚀-薄膜沉积-互连-测试-封装。

为帮助大家了解和认识半导体及相关工艺,我们将以三期微信推送,为大家逐一介绍上述每个步骤。

第一步 晶圆加工

所有半导体工艺都始于一粒沙子!因为沙子所含的硅是生产晶圆所需要的原材料。晶圆是将硅(Si)或砷化镓(GaAs)制成的单晶柱体切割形成的圆薄片。要提取高纯度的硅材料需要用到硅砂,一种二氧化硅含量高达95%的特殊材料,也是制作晶圆的主要原材料。晶圆加工就是制作获取上述晶圆的过程。

① 铸锭

首先需将沙子加热,分离其中的一氧化碳和硅,并不断重复该过程直至获得超高纯度的电子级硅(EG-Si)。高纯硅熔化成液体,进而再凝固成单晶固体形式,称为“锭”,这就是半导体制造的第一步。硅锭(硅柱)的制作精度要求很高,达到纳米级,其广泛应用的制造方法是提拉法。

② 锭切割

前一个步骤完成后,需要用金刚石锯切掉铸锭的两端,再将其切割成一定厚度的薄片。锭薄片直径决定了晶圆的尺寸,更大更薄的晶圆能被分割成更多的可用单元,有助于降低生产成本。切割硅锭后需在薄片上加入“平坦区”或“凹痕”标记,方便在后续步骤中以其为标准设置加工方向。

③ 晶圆表面抛光

通过上述切割过程获得的薄片被称为“裸片”,即未经加工的“原料晶圆”。裸片的表面凹凸不平,无法直接在上面印制电路图形。因此,需要先通过研磨和化学刻蚀工艺去除表面瑕疵,然后通过抛光形成光洁的表面,再通过清洗去除残留污染物,即可获得表面整洁的成品晶圆。

第二步 氧化

氧化过程的作用是在晶圆表面形成保护膜。它可以保护晶圆不受化学杂质影响、避免漏电流进入电路、预防离子植入过程中的扩散以及防止晶圆在刻蚀时滑脱。

氧化过程的第一步是去除杂质和污染物,需要通过四步去除有机物、金属等杂质及蒸发残留的水分。清洁完成后就可以将晶圆置于800至1200摄氏度的高温环境下,通过氧气或蒸气在晶圆表面的流动形成二氧化硅(即“氧化物”)层。氧气扩散通过氧化层与硅反应形成不同厚度的氧化层,可以在氧化完成后测量它的厚度。

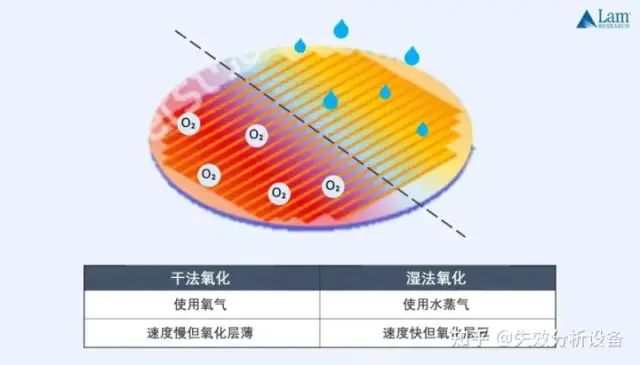

干法氧化和湿法氧化

根据氧化反应中氧化剂的不同,热氧化过程可分为干法氧化和湿法氧化,前者使用纯氧产生二氧化硅层,速度慢但氧化层薄而致密,后者需同时使用氧气和高溶解度的水蒸气,其特点是生长速度快但保护层相对较厚且密度较低。

除氧化剂以外,还有其他变量会影响到二氧化硅层的厚度。首先,晶圆结构及其表面缺陷和内部掺杂浓度都会影响氧化层的生成速率。此外,氧化设备产生的压力和温度越高,氧化层的生成就越快。在氧化过程,还需要根据单元中晶圆的位置而使用假片,以保护晶圆并减小氧化度的差异。

第三步 光刻

光刻是通过光线将电路图案“印刷”到晶圆上,我们可以将其理解为在晶圆表面绘制半导体制造所需的平面图。电路图案的精细度越高,成品芯片的集成度就越高,必须通过先进的光刻技术才能实现。具体来说,光刻可分为涂覆光刻胶、曝光和显影三个步骤。

① 涂覆光刻胶

在晶圆上绘制电路的第一步是在氧化层上涂覆光刻胶。光刻胶通过改变化学性质的方式让晶圆成为“相纸”。晶圆表面的光刻胶层越薄,涂覆越均匀,可以印刷的图形就越精细。这个步骤可以采用“旋涂”方法。

根据光(紫外线)反应性的区别,光刻胶可分为两种:正胶和负胶,前者在受光后会分解并消失,从而留下未受光区域的图形,而后者在受光后会聚合并让受光部分的图形显现出来。

② 曝光

在晶圆上覆盖光刻胶薄膜后,就可以通过控制光线照射来完成电路印刷,这个过程被称为“曝光”。我们可以通过曝光设备来选择性地通过光线,当光线穿过包含电路图案的掩膜时,就能将电路印制到下方涂有光刻胶薄膜的晶圆上。

在曝光过程中,印刷图案越精细,最终的芯片就能够容纳更多元件,这有助于提高生产效率并降低单个元件的成本。在这个领域,目前备受瞩目的新技术是EUV光刻。去年2月,泛林集团与战略合作伙伴ASML和imec共同研发出了一种全新的干膜光刻胶技术。该技术能通过提高分辨率(微调电路宽度的关键要素)大幅提升EUV光刻曝光工艺的生产率和良率。

③ 显影

曝光之后的步骤是在晶圆上喷涂显影剂,目的是去除图形未覆盖区域的光刻胶,从而让印刷好的电路图案显现出来。显影完成后需要通过各种测量设备和光学显微镜进行检查,确保电路图绘制的质量。

以上是对晶圆加工、氧化和光刻工艺的简要介绍,下面,我们将为大家介绍半导体制造中两大重要步骤——刻蚀和薄膜沉积!

第四步 刻蚀

在晶圆上完成电路图的光刻后,就要用刻蚀工艺来去除任何多余的氧化膜且只留下半导体电路图。要做到这一点需要利用液体、气体或等离子体来去除选定的多余部分。

刻蚀的方法主要分为两种,取决于所使用的物质:使用特定的化学溶液进行化学反应来去除氧化膜的湿法刻蚀,以及使用气体或等离子体的干法刻蚀。湿法刻蚀

使用化学溶液去除氧化膜的湿法刻蚀具有成本低、刻蚀速度快和生产率高的优势。然而,湿法刻蚀具有各向同性的特点,即其速度在任何方向上都是相同的。这会导致掩膜(或敏感膜)与刻蚀后的氧化膜不能完全对齐,因此很难处理非常精细的电路图。

干法刻蚀

干法刻蚀可分为三种不同类型。第一种为化学刻蚀,其使用的是刻蚀气体(主要是氟化氢)。和湿法刻蚀一样,这种方法也是各向同性的,这意味着它也不适合用于精细的刻蚀。

第二种方法是物理溅射,即用等离子体中的离子来撞击并去除多余的氧化层。作为一种各向异性的刻蚀方法,溅射刻蚀在水平和垂直方向的刻蚀速度是不同的,因此它的精细度也要超过化学刻蚀。但这种方法的缺点是刻蚀速度较慢,因为它完全依赖于离子碰撞引起的物理反应。

最后的第三种方法就是反应离子刻蚀(RIE)。RIE结合了前两种方法,即在利用等离子体进行电离物理刻蚀的同时,借助等离子体活化后产生的自由基进行化学刻蚀。除了刻蚀速度超过前两种方法以外,RIE可以利用离子各向异性的特性,实现高精细度图案的刻蚀。

如今干法刻蚀已经被广泛使用,以提高精细半导体电路的良率。保持全晶圆刻蚀的均匀性并提高刻蚀速度至关重要,当今最先进的干法刻蚀设备正在以更高的性能,支持最为先进的逻辑和存储芯片的生产。

针对不同的刻蚀应用,泛林集团提供多个刻蚀产品系列,包括用于深硅刻蚀的DSiE系列和Syndion系列、关键介电刻蚀产品Flex系列、用于导体刻蚀的Kiyo系列、用于金属刻蚀的Versys Metal系列。在行业领先的Kiyo和Flex工艺模块的基础上,泛林集团还于去年3月推出Sense.i系列,其高性能表现能够满足前述生产过程所需的精确性和一致性要求,适合各种关键和半关键性刻蚀应用。

第五步 薄膜沉积

为了创建芯片内部的微型器件,我们需要不断地沉积一层层的薄膜并通过刻蚀去除掉其中多余的部分,另外还要添加一些材料将不同的器件分离开来。每个晶体管或存储单元就是通过上述过程一步步构建起来的。我们这里所说的“薄膜”是指厚度小于1微米(μm,百万分之一米)、无法通过普通机械加工方法制造出来的“膜”。将包含所需分子或原子单元的薄膜放到晶圆上的过程就是“沉积”。

要形成多层的半导体结构,我们需要先制造器件叠层,即在晶圆表面交替堆叠多层薄金属(导电)膜和介电(绝缘)膜,之后再通过重复刻蚀工艺去除多余部分并形成三维结构。可用于沉积过程的技术包括化学气相沉积 (CVD)、原子层沉积 (ALD) 和物理气相沉积 (PVD),采用这些技术的方法又可以分为干法和湿法沉积两种。

01.化学气相沉积

在化学气相沉积中,前驱气体会在反应腔发生化学反应并生成附着在晶圆表面的薄膜以及被抽出腔室的副产物。

等离子体增强化学气相沉积则需要借助等离子体产生反应气体。这种方法降低了反应温度,因此非常适合对温度敏感的结构。使用等离子体还可以减少沉积次数,往往可以带来更高质量的薄膜。

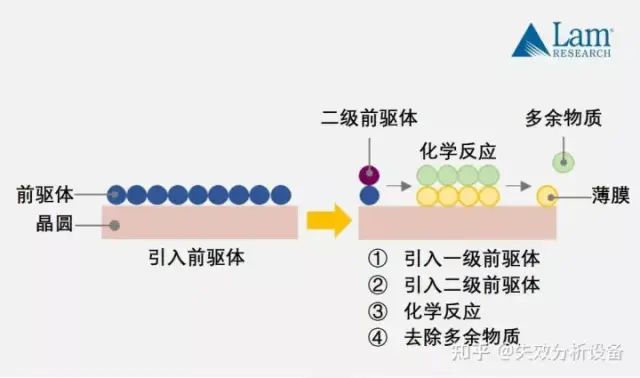

02.原子层沉积

原子层沉积通过每次只沉积几个原子层从而形成薄膜。该方法的关键在于循环按一定顺序进行的独立步骤并保持良好的控制。在晶圆表面涂覆前驱体是第一步,之后引入不同的气体与前驱体反应即可在晶圆表面形成所需的物质。

03.物理气相沉积

顾名思义,物理气相沉积是指通过物理手段形成薄膜。溅射就是一种物理气相沉积方法,其原理是通过氩等离子体的轰击让靶材的原子溅射出来并沉积在晶圆表面形成薄膜。

在某些情况下,可以通过紫外线热处理 (UVTP) 等技术对沉积膜进行处理并改善其性能。

泛林集团的沉积设备均具备出色的精度、性能和灵活性,包括适用于钨金属化工艺的ALTUS系列、具有后薄膜沉积处理能力的SOLA系列、高密度等离子体化学气相沉积SPEED系列、采用先进ALD技术的Striker系列以及VECTOR PECVD系列等。

我们已经从前面的了解了半导体制造的前几大步骤,包括晶圆加工、氧化、光刻、刻蚀和薄膜沉积。我们继续介绍最后三个步骤:互连、测试和封装,以完成半导体芯片的制造。

第六步 · 互连

半导体的导电性处于导体与非导体(即绝缘体)之间,这种特性使我们能完全掌控电流。通过基于晶圆的光刻、刻蚀和沉积工艺可以构建出晶体管等元件,但还需要将它们连接起来才能实现电力与信号的发送与接收。

金属因其具有导电性而被用于电路互连。用于半导体的金属需要满足以下条件:

低电阻率:由于金属电路需要传递电流,因此其中的金属应具有较低的电阻。

热化学稳定性:金属互连过程中金属材料的属性必须保持不变。

高可靠性:随着集成电路技术的发展,即便是少量金属互连材料也必须具备足够的耐用性。

制造成本:即使已经满足前面三个条件,材料成本过高的话也无法满足批量生产的需要。互连工艺主要使用铝和铜这两种物质。

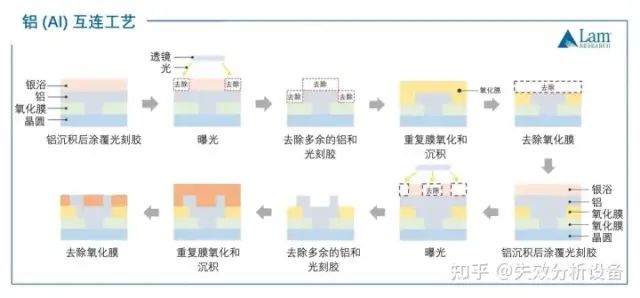

铝互连工艺

铝互连工艺始于铝沉积、光刻胶应用以及曝光与显影,随后通过刻蚀有选择地去除任何多余的铝和光刻胶,然后才能进入氧化过程。前述步骤完成后再不断重复光刻、刻蚀和沉积过程直至完成互连。

除了具有出色的导电性,铝还具有容易光刻、刻蚀和沉积的特点。此外,它的成本较低,与氧化膜粘附的效果也比较好。其缺点是容易腐蚀且熔点较低。另外,为防止铝与硅反应导致连接问题,还需要添加金属沉积物将铝与晶圆隔开,这种沉积物被称为“阻挡金属”。

铝电路是通过沉积形成的。晶圆进入真空腔后,铝颗粒形成的薄膜会附着在晶圆上。这一过程被称为“气相沉积 (VD) ”,包括化学气相沉积和物理气相沉积。

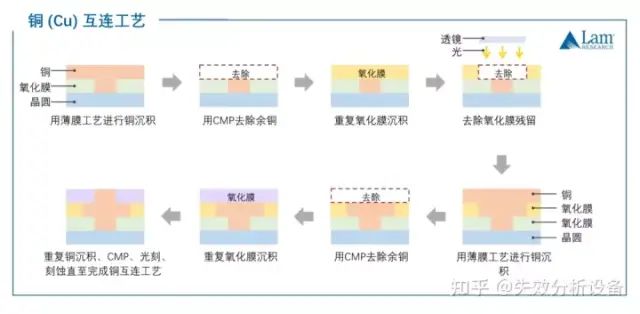

铜互连工艺

随着半导体工艺精密度的提升以及器件尺寸的缩小,铝电路的连接速度和电气特性逐渐无法满足要求,为此我们需要寻找满足尺寸和成本两方面要求的新导体。铜之所以能取代铝的第一个原因就是其电阻更低,因此能实现更快的器件连接速度。其次铜的可靠性更高,因为它比铝更能抵抗电迁移,也就是电流流过金属时发生的金属离子运动。

但是,铜不容易形成化合物,因此很难将其气化并从晶圆表面去除。针对这个问题,我们不再去刻蚀铜,而是沉积和刻蚀介电材料,这样就可以在需要的地方形成由沟道和通路孔组成的金属线路图形,之后再将铜填入前述“图形”即可实现互连,而最后的填入过程被称为“镶嵌工艺”。

随着铜原子不断扩散至电介质,后者的绝缘性会降低并产生阻挡铜原子继续扩散的阻挡层。之后阻挡层上会形成很薄的铜种子层。到这一步之后就可以进行电镀,也就是用铜填充高深宽比的图形。填充后多余的铜可以用金属化学机械抛光 (CMP) 方法去除,完成后即可沉积氧化膜,多余的膜则用光刻和刻蚀工艺去除即可。前述整个过程需要不断重复直至完成铜互连为止。

通过上述对比可以看出,铜互连和铝互连的区别在于,多余的铜是通过金属CMP而非刻蚀去除的。

第七步 测试

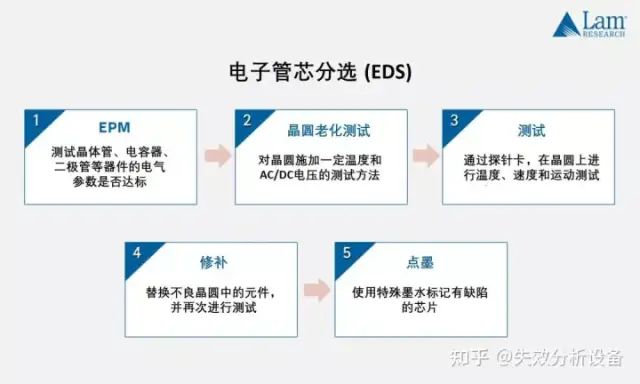

测试的主要目标是检验半导体芯片的质量是否达到一定标准,从而消除不良产品、并提高芯片的可靠性。另外,经测试有缺陷的产品不会进入封装步骤,有助于节省成本和时间。电子管芯分选 (EDS) 就是一种针对晶圆的测试方法。

EDS是一种检验晶圆状态中各芯片的电气特性并由此提升半导体良率的工艺。EDS可分为五步,具体如下 :

01.电气参数监控 (EPM)

EPM是半导体芯片测试的第一步。该步骤将对半导体集成电路需要用到的每个器件(包括晶体管、电容器和二极管)进行测试,确保其电气参数达标。EPM的主要作用是提供测得的电气特性数据,这些数据将被用于提高半导体制造工艺的效率和产品性能(并非检测不良产品)。

02.晶圆老化测试

半导体不良率来自两个方面,即制造缺陷的比率(早期较高)和之后整个生命周期发生缺陷的比率。晶圆老化测试是指将晶圆置于一定的温度和AC/DC电压下进行测试,由此找出其中可能在早期发生缺陷的产品,也就是说通过发现潜在缺陷来提升最终产品的可靠性。

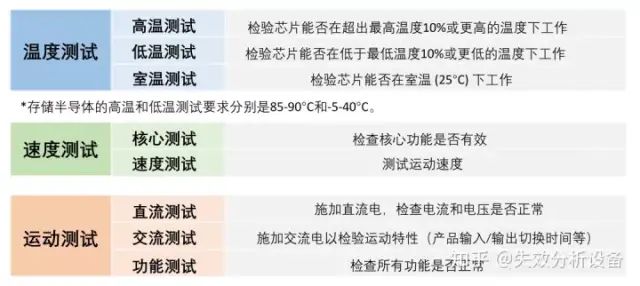

03.检测

老化测试完成后就需要用探针卡将半导体芯片连接到测试装置,之后就可以对晶圆进行温度、速度和运动测试以检验相关半导体功能。具体测试步骤的说明请见表格。

04.修补

修补是最重要的测试步骤,因为某些不良芯片是可以修复的,只需替换掉其中存在问题的元件即可。

05.点墨

未能通过电气测试的芯片已经在之前几个步骤中被分拣出来,但还需要加上标记才能区分它们。过去我们需要用特殊墨水标记有缺陷的芯片,保证它们用肉眼即可识别,如今则是由系统根据测试数据值自动进行分拣。

第八步 · 封装

经过之前几个工艺处理的晶圆上会形成大小相等的方形芯片(又称“单个晶片”)。下面要做的就是通过切割获得单独的芯片。刚切割下来的芯片很脆弱且不能交换电信号,需要单独进行处理。这一处理过程就是封装,包括在半导体芯片外部形成保护壳和让它们能够与外部交换电信号。整个封装制程分为五步,即晶圆锯切、单个晶片附着、互连、成型和封装测试。

01.晶圆锯切

要想从晶圆上切出无数致密排列的芯片,我们首先要仔细“研磨”晶圆的背面直至其厚度能够满足封装工艺的需要。研磨后,我们就可以沿着晶圆上的划片线进行切割,直至将半导体芯片分离出来。

晶圆锯切技术有三种:刀片切割、激光切割和等离子切割。刀片切割是指用金刚石刀片切割晶圆,这种方法容易产生摩擦热和碎屑并因此损坏晶圆。激光切割的精度更高,能轻松处理厚度较薄或划片线间距很小的晶圆。等离子切割采用等离子刻蚀的原理,因此即使划片线间距非常小,这种技术同样能适用。

02.单个晶片附着

所有芯片都从晶圆上分离后,我们需要将单独的芯片(单个晶片)附着到基底(引线框架)上。基底的作用是保护半导体芯片并让它们能与外部电路进行电信号交换。附着芯片时可以使用液体或固体带状粘合剂。

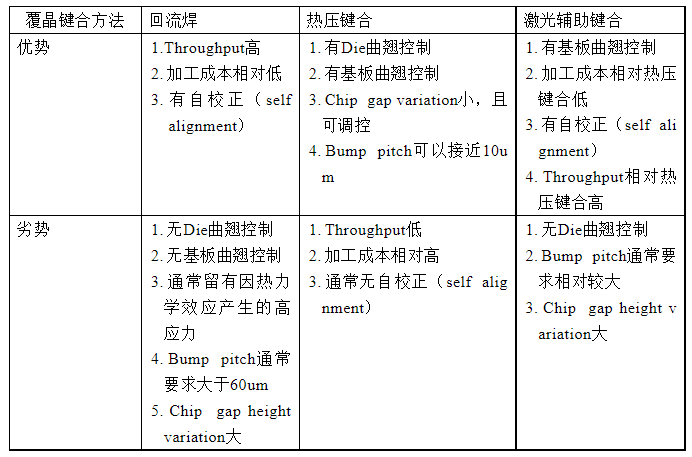

03.互连

在将芯片附着到基底上之后,我们还需要连接二者的接触点才能实现电信号交换。这一步可以使用的连接方法有两种:使用细金属线的引线键合和使用球形金块或锡块的倒装芯片键合。引线键合属于传统方法,倒装芯片键合技术可以加快半导体制造的速度。

04.成型

完成半导体芯片的连接后,需要利用成型工艺给芯片外部加一个包装,以保护半导体集成电路不受温度和湿度等外部条件影响。根据需要制成封装模具后,我们要将半导体芯片和环氧模塑料 (EMC) 都放入模具中并进行密封。密封之后的芯片就是最终形态了。

05.封装测试

已经具有最终形态的芯片还要通过最后的缺陷测试。进入最终测试的全部是成品的半导体芯片。它们将被放入测试设备,设定不同的条件例如电压、温度和湿度等进行电气、功能和速度测试。这些测试的结果可以用来发现缺陷、提高产品质量和生产效率。

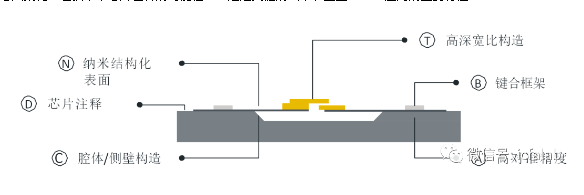

封装技术的演变

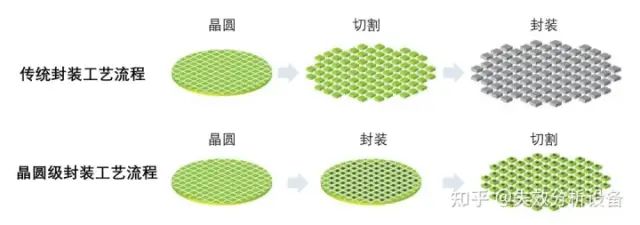

随着芯片体积的减少和性能要求的提升,封装在过去数年间已经历了多次技术革新。面向未来的一些封装技术和方案包括将沉积用于传统后道工艺,例如晶圆级封装(WLP)、凸块工艺和重布线层 (RDL) 技术,以及用于前道晶圆制造的的刻蚀和清洁技术。

下面我们介绍一些基于泛林集团开发的先进封装解决方案。

什么是先进封装?

传统封装需要将每个芯片都从晶圆中切割出来并放入模具中。晶圆级封装(WLP)则是先进封装技术的一种, 是指直接封装仍在晶圆上的芯片。WLP的流程是先封装测试,然后一次性将所有已成型的芯片从晶圆上分离出来。与传统封装相比,WLP的优势在于更低的生产成本。

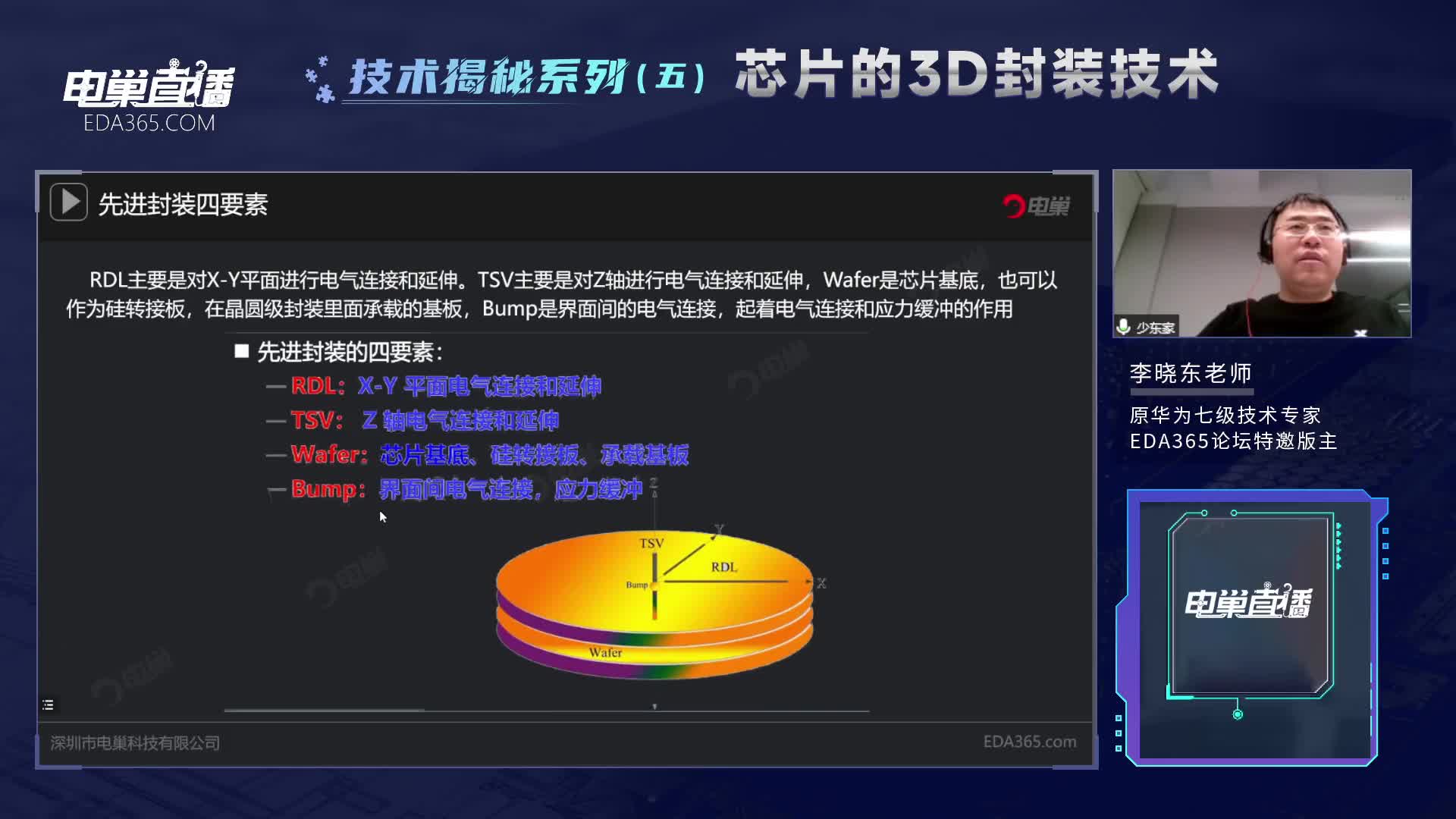

先进封装可划分为2D封装、2.5D封装和3D封装。

更小的2D封装

如前所述,封装工艺的主要用途包括将半导体芯片的信号发送到外部,而在晶圆上形成的凸块就是发送输入/输出信号的接触点。这些凸块分为扇入型(fan-in) 和扇出型 (fan-out) 两种,前者的扇形在芯片内部,后者的扇形则要超出芯片范围。我们将输入/输出信号称为I/O(输入/输出),输入/输出数量称为I/O计数。I/O计数是确定封装方法的重要依据。如果I/O计数低就采用扇入封装工艺。由于封装后芯片尺寸变化不大,因此这种过程又被称为芯片级封装 (CSP) 或晶圆级芯片尺寸封装 (WLCSP)。如果I/O计数较高,则通常要采用扇出型封装工艺,且除凸块外还需要重布线层 (RDL) 才能实现信号发送。这就是“扇出型晶圆级封装 (FOWLP)”。

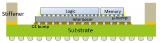

2.5D 封装

2.5D封装技术可以将两种或更多类型的芯片放入单个封装,同时让信号横向传送,这样可以提升封装的尺寸和性能。最广泛使用的2.5D封装方法是通过硅中介层将内存和逻辑芯片放入单个封装。2.5D封装需要硅通孔 (TSV)、微型凸块和小间距RDL等核心技术。

3D 封装

3D封装技术可以将两种或更多类型的芯片放入单个封装,同时让信号纵向传送。这种技术适用于更小和I/O计数更高的半导体芯片。TSV可用于I/O计数高的芯片,引线键合可用于I/O计数低的芯片,并最终形成芯片垂直排列的信号系统。3D封装需要的核心技术包括TSV和微型凸块技术

泛林集团能够提供上述工艺所需的核心方案,包括硅刻蚀、金属扩散阻挡层、镀铜和清洗技术,以及构建微型凸块和微型RDL所需的电镀、清洗和湿刻蚀方案。

至此,半导体产品制造的八个步骤“晶圆加工-氧化-光刻-刻蚀-薄膜沉积-互连-测试-封装”已全部介绍完毕,从“沙粒”蜕变到“芯片”,半导体科技正在上演现实版“点石成金”。

编辑:黄飞

电子发烧友App

电子发烧友App

评论