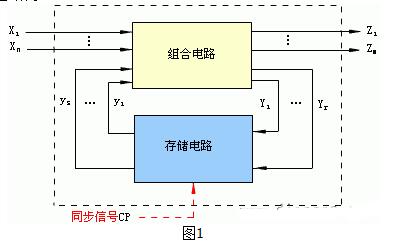

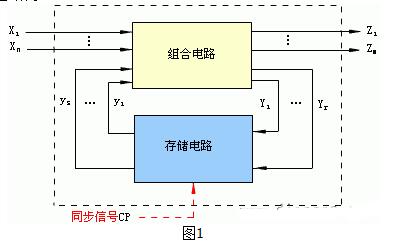

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 59632

59632

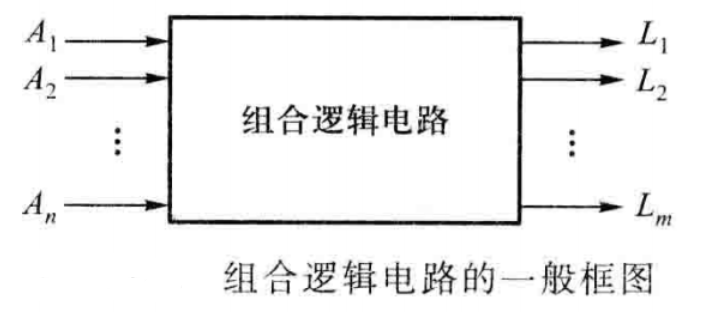

分析组合逻辑电路的目的是,对于一个给定的逻辑电路,确定其逻辑功能。

2020-08-04 15:50:00 37815

37815 对于一个逻辑电路,其输出状态在任何时刻只取决于同一时刻的输入状态,而与电路原来的状态无关,这种电路被定义为组合逻辑电路。

2024-02-04 15:33:21 4148

4148

、安全处理器等,利用逻辑电路实现数据加密、身份验证等安全功能。

英锐恩科技的逻辑电路芯片则负责信号处理、数据转发等关键功能,确保了通信网络的稳定性和可靠性。值得一提的是,英锐恩科技的逻辑电路芯片在安全

2024-09-30 10:47:47

逻辑电路主要逻辑门电路之间的关系是怎样的

2020-04-15 17:53:30

逻辑电路的纠错技术是如何实现的?纠错技术在逻辑电路中有什么作用?

2021-06-18 09:50:31

CPLD逻辑电路

2019-10-29 09:10:54

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

`内容简介本书是“实用电子电路设计丛书”之一。本书以实现高速高可靠性的数字系统设计为目标,以完全同步式电路为基础,从技术实现的角度介绍ASIC逻辑电路设计技术。内容包括:逻辑门电路、逻辑压缩、组合

2018-04-03 17:14:16

本文为明德扬原创及录用文章,转载请注明出处!一、 什么是组合逻辑电路? 在数字电路中,根据逻辑功能的不同,我们可以将数字电路分成两大类,一类叫做组合逻辑电路、另一类叫做时序逻辑电路。本次主要

2020-04-24 15:07:49

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

Verilog程序模块的结构是由哪些部分组成的?如何去实现时序逻辑电路和组合逻辑电路的设计呢?

2021-11-03 06:35:57

时序逻辑电路的特点

2019-10-08 05:34:53

时序逻辑电路的设计实验1 进一步强化EDA仿真软件的使用;2 掌握利用MSI

2009-03-19 15:10:18

组合逻辑电路实验实验三 组合逻辑电路一、 实验目的1、 掌握组合逻辑电路的功能测试2、 验证半加器和全加器的逻辑功能3、 学会

2009-03-20 18:11:09

逻辑电路中,输出始终取决于其输入的组合。因此,组合电路是无记忆的。 因此,如果其输入条件之一从0-1或1-0改变状态,则默认情况下,组合逻辑电路的结果输出也将在其设计中具有“无内存”,“时序”或“反馈回路

2020-12-31 17:01:17

怎样去设计一种检纠错逻辑电路?怎样对检纠错逻辑电路进行仿真?

2021-05-06 08:12:58

组合逻辑电路的基本模块是什么?时序逻辑电路怎样进行工作的?

2021-09-18 09:19:42

在上一篇博文CPU的设计与实现(1)--方案设计中,较为详细地讲解了我将要设计实现的Gater8这个基于自制CPU的自制计算机的设计方案。 这是本系列第二篇博文,我将详细分析具体设计完成的Gater8的数字逻辑电路。最初计划本系列博文的第二篇应该是打算用各种纯二进制门(与门、...

2021-07-30 07:19:40

集成逻辑电路、组合逻辑电路实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法

2008-12-11 23:36:32

组合逻辑电路 :

2007-12-20 23:02:07 30

30

数字逻辑电路的内容:数制与编码,,逻辑代数和逻辑函数,集成逻辑门,组合逻辑电路,中规模集成组

2008-09-06 01:54:26 33

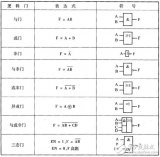

33 基本逻辑电路: 组合逻辑电路、&

2008-09-12 16:35:29 40

40 组合逻辑电路设计一、实验目的1. 熟悉组合逻辑电路的基本设计方法;2. 练习用门电路、译码器、数据选择器设计组合逻辑电路。二、实验设备1.

2008-09-12 16:41:23 0

0 时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 组合逻辑电路(简称组合电路)任意时刻的输出信号仅取决于该时刻的输入信号,与信号作用前电路原来的状态无关时序逻辑电路(简称时序电路)任意时刻的输出信号不仅取决

2009-07-15 18:45:58 0

0 组合逻辑电路电子教案:数字逻辑电路可分为两大类: 一类叫组合逻辑电路;另一类叫时序逻辑电路。本章首先介绍组合逻辑电路的共同特点和描述方法,然后重点介绍组合逻辑电

2009-09-01 08:58:29 0

0 数字系统的基本算法与逻辑电路实现:本章主要介绍数字系统的基本算法设计及对应的逻辑电路的实现方法。算法设计中主要考虑的因素1.逻辑指标这是数字系统最重要、

2009-09-01 09:04:09 0

0 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 0

0 钟控传输门绝热逻辑电路和SRAM 的设计

本文利用NMOS管的自举效应设计了一种新的采用二相无交叠功率时钟的绝热逻辑电路---钟控传输门绝热逻辑电路,实现对输

2010-02-23 10:14:13 15

15 讲述组合逻辑电路设计基础

2010-05-06 10:29:15 0

0 数字逻辑电路设计课程

数字逻辑电路的设计包括两个方面:基本逻辑功能电路设计和逻辑电路系统设计。关于基本逻辑功能电路设计一般在《数字电路技术基础

2010-05-24 16:05:50 0

0 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 0

0 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 24

24 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

55 一、实验目的掌握组合逻辑电路的设计与测试方法

2010-09-21 16:52:20 0

0 基本组合逻辑电路

一、 实验目的?⒈ 掌握一般组合逻辑电路的分析和设计方法。?⒉ 熟悉集成优先编码器的逻辑功能及简单应用。

2008-09-24 22:14:03 2886

2886 组合逻辑电路的分析与设计-逻辑代数

在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而与先前状态无关的逻辑电路称为组合逻辑电路。

2009-04-07 10:07:57 3923

3923

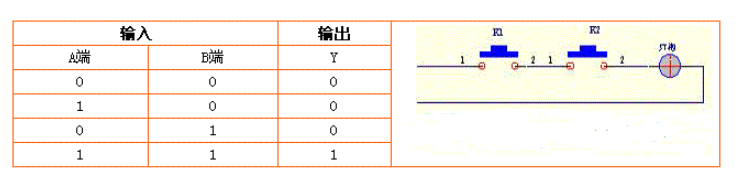

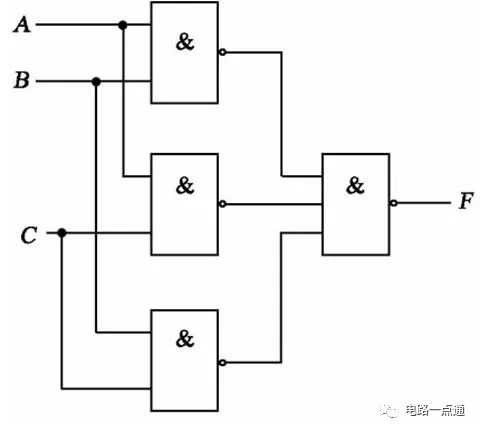

组合逻辑电路的分析

分析组合逻辑电路的目的是为了确定已知电路的逻辑功能,其步骤大致如下: 1.由逻辑图写出各输出端的逻辑表达式; 2.化简和变换各

2009-04-07 10:11:55 8346

8346

组合逻辑电路的设计

组合逻辑电路的设计与分析过程相反,其步骤大致如下: (1)根据对电路逻辑功能的要求,列出真值表; (2)由真值表写出逻辑表达

2009-04-07 10:12:22 14015

14015

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 9154

9154

时序逻辑电路的特点

在第三章所讨论的组合逻辑电路中,任一时刻的输出信号仅仅取决于该时刻的输入信号,而与电路原来

2009-09-30 18:19:22 10881

10881

数字逻辑电路

数字逻辑电路的用途和特点

数字电子电路中的后起之秀是数字逻辑电路。把它叫做数字电路是因为电路中传递的虽然也是脉冲,但这些脉冲是

2009-11-10 10:13:26 17873

17873 CPLD逻辑电路 图6是CPLD内部逻辑电路,CPLD选用的是LATTICE公司的ispLSI1016E,逻辑设计采用原理图输入法,主要功能是对MUX的通道进行选择、对A/D转换器进

2009-11-13 12:04:13 2982

2982

各种逻辑电路简介

逻辑电路:

以二进制为原理、实现数字信号逻辑运算和操作的电路。分组合逻辑电路和

2009-11-24 13:27:04 3539

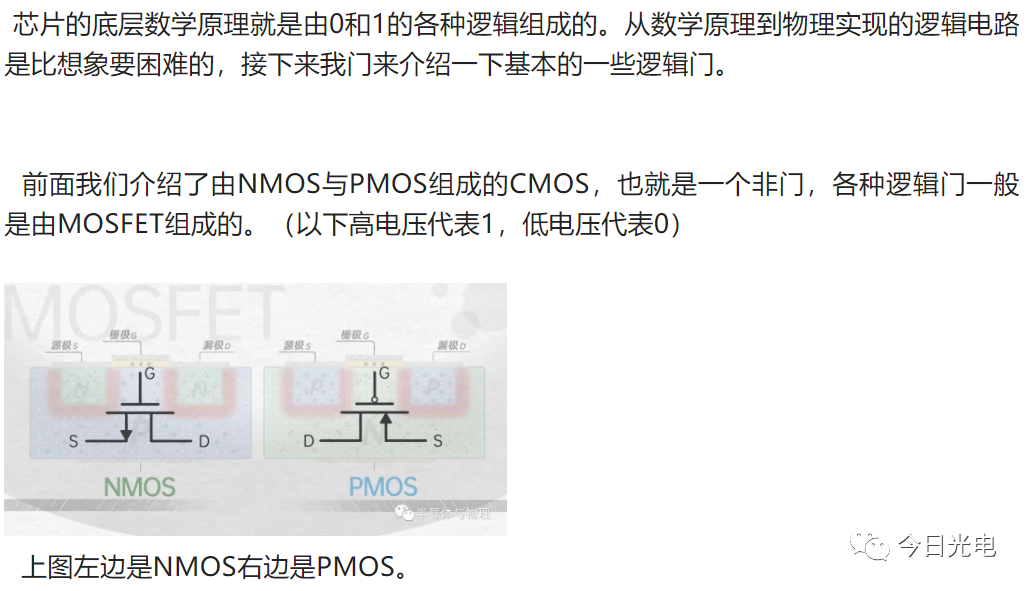

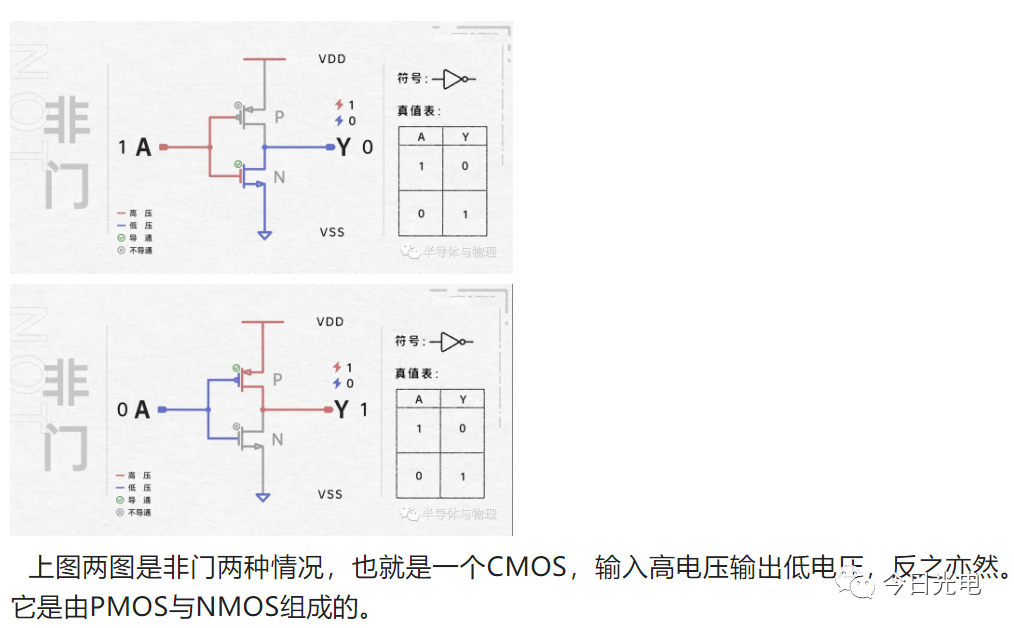

3539 CMOS逻辑电路,CMOS逻辑电路是什么意思

CMOS是单词的首字母缩写,代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类

2010-03-08 11:31:47 3921

3921 什么是阵列逻辑电路

阵列逻辑电路的特点: 逻辑元件在硅片上以阵列形式排列,芯片面积小、用户自编程、设计方便。 典型的阵列

2010-04-15 13:43:17 4213

4213 组合逻辑电路,感兴趣的可以下载看看,免费的哦!

2015-10-29 15:08:16 34

34 数字电路 实验一 组合逻辑电路的设计与测试

2015-11-17 18:23:49 2

2 定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计定时控制器逻辑电路设计

2015-12-17 18:18:50 0

0 1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、熟悉CPLD设计的过程,比较原理图输入和文本输入的优劣。

2022-07-10 14:38:36 17

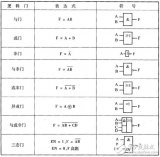

17 逻辑电路是包含逻辑关系的数字电路, 以二进制为原理、实现数字离散信号的传递,逻辑运算和操作的电路。最基本的逻辑电路是常见的门电路,而最简单的门电路为与电路、或电路和非电路。

2017-05-22 09:58:43 21951

21951

逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。

2017-05-22 15:15:59 77019

77019

时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑电路有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

2018-04-09 16:00:00 6913

6913

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

2018-01-30 16:24:25 40174

40174

组合逻辑电路的设计与分析过程相反,本文小编主要跟大家介绍一下关于组合逻辑电路的设计步骤,顺便回顾一下组合逻辑电路的分析方法。

2018-01-30 16:46:31 124120

124120

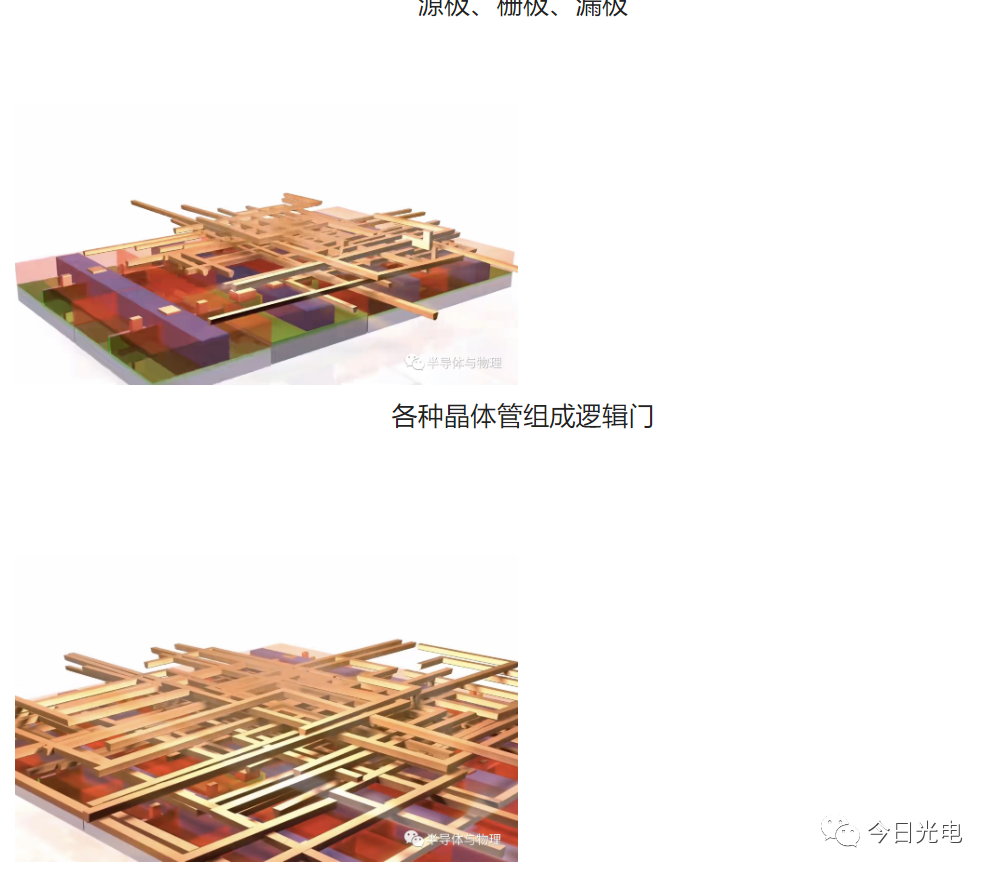

逻辑电路按其逻辑功能和结构特点可分为组合逻辑电路和时序逻辑电路。单一的与门、或门、与非门、或非门、非门等逻辑门不足以完成复杂的数字系统设计要求。组合逻辑电路是采用两个或两个以上基本逻辑门来实现更实用、复杂的逻辑功能。

2018-01-30 17:05:44 67768

67768

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 94951

94951

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 128321

128321

时序逻辑路是数字电路的一种,时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 19:19:25 67995

67995

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 112182

112182

根据逻辑功能的不同,可把数字电路分为组合逻辑电路(Combinational Logic Circuit)和 时序逻辑电路(Sequential Logic Circuit)两大类。

2018-07-20 08:00:00 0

0 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 32851

32851 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 52418

52418 组合逻辑电路是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路不仅仅取决于当前的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-02-26 15:32:30 67228

67228 从整体上来看,数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。在逻辑功能方面,组合逻辑电路在任一时刻的输出信号仅与当时的输入信号有关,与信号作用前电路原来所处的状态无关;而时序逻辑电路在任一时刻的输出信号不仅与当时的输入信号有关,而且还与电路原来的状态有关。

2019-05-16 18:27:52 10796

10796

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 8978

8978

组合逻辑电路是无记忆数字逻辑电路,其任何时刻的输出仅取决于其输入的组合.

2019-06-22 10:53:20 50945

50945

在逻辑电路中,输入和输出只有两种状态,即高电平和低电平。通常以逻辑“1”和“0”表示电平高低

2020-06-19 16:51:17 14097

14097

逻辑电路在任何时刻产生的稳定的输出信号仅仅取决于该时刻的输入信号,而与过去的输入信号无关,即与输入信号作用前的状态无关,这样的电路称为组合逻辑电路。

2020-08-08 10:40:00 6454

6454

本文档的主要内容详细介绍的是组合逻辑电路和时序逻辑电路的学习课件免费下载包括了:任务一 组合逻辑电路,任务二 编码器,任务三 译码器,任务四 集成触发器,任务五 寄存器,任务六 计数器。

2020-10-27 15:58:24 31

31 数字电路的分类

(1)按电路结构分类

组合逻辑电路

时序逻辑电路:。

(2)按集成电路规模分:小规模、中规模和大规模。

2022-12-05 14:54:47 14

14 组合逻辑电路:用各种门电路组成的,用于实现某种功能的复杂逻辑电路。特点:某一时刻的输出状态仅由该时刻电路的输入信号决定, 而与该电路在此输入信号之前所具有的状态无关。

2022-12-05 14:52:54 9

9 本文介绍开发组合逻辑电路时可能发生的意外开关事件,称为危险。 本文是关于使用逻辑门进行组合电路设计和仿真的介绍性系列文章的第二部分。在上一篇文章中,我们介绍了 组合逻辑电路 以及如何简化它们

2023-01-27 14:18:00 2709

2709

数字电路中的组合逻辑电路的设计与分析过程相反,本文小编主要跟大家介绍一下关于组合逻辑电路的设计步骤,顺便回顾一下组合逻辑电路的分析方法。

2023-02-03 09:56:23 8000

8000 所谓组合逻辑电路的分析,就是根据给定的逻辑电路图,求出电路的逻辑功能。

2023-03-06 14:37:26 5872

5872 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 8731

8731

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 5503

5503

时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 8532

8532

所谓组合逻辑电路的分析,就是根据给定的逻辑电路图,求出电路的逻辑功能。

2023-08-16 09:15:23 11275

11275

当逻辑电路由多个逻辑门组成且不含存储电路,对于给定的输入变量组合将产生确定的输出,则这种逻辑电路称为组合逻辑电路。

2024-02-04 11:46:36 3338

3338

组合逻辑电路和时序逻辑电路是数字电路中两种重要的逻辑电路类型,它们主要区别在于其输出信号的依赖关系和对时间的敏感性。

2024-02-04 16:00:27 7169

7169 时序逻辑电路是一种能够存储信息并根据时钟信号按照特定顺序执行操作的电路。它是计算机硬件中非常重要的一部分,用于实现存储器、时序控制器等功能。与之相对的是组合逻辑电路,它根据输入信号的组合情况,立即

2024-02-06 11:18:34 13635

13635 时序逻辑电路的输出与输入信号以及内部存储器状态有关。时序逻辑电路是一类特殊的数字电路,其输出信号的值不仅取决于当前的输入信号,还取决于过去的输入信号以及内部存储器的状态。 时序逻辑电路由两部分

2024-02-06 14:30:23 4297

4297 什么是组合逻辑电路和时序逻辑电路?时序逻辑电路和组合逻辑电路的区别是什么 组合逻辑电路和时序逻辑电路是数字电路中两种基本类型的电路设计。 组合逻辑电路是由逻辑门组成的,逻辑门的输出仅由它的当前输入

2024-03-26 16:12:14 6631

6631 。 逻辑电路的应用领域: 一、计算机与微处理器 逻辑电路是计算机和微处理器的基础,用于实现算术逻辑单元(ALU)、控制单元等核心部件。这些部件负责执行程序的指令,处理数据,以及协调计算机内部各个部分的工作。 二、通信

2024-05-24 15:54:55 3132

3132 在数字电路设计中,触发器和时序逻辑电路是构建复杂数字系统不可或缺的基础元素。触发器(Flip-Flop)作为基本的存储单元,能够存储一位二进制信息,并在特定的时钟信号控制下更新其状态。而时序逻辑电路

2024-07-18 17:43:41 4403

4403 一、引言 组合逻辑电路是数字电路中的重要组成部分,它仅由逻辑门电路(如与门、或门、非门等)和输入/输出端组成,不包含任何存储元件。组合逻辑电路的输出仅取决于当前的输入信号,与电路的历史状态无关。因此

2024-07-30 14:38:04 3067

3067 组合逻辑电路是数字电路中的一种基本类型,它由逻辑门组成,根据输入信号的组合产生相应的输出信号。组合逻辑电路广泛应用于计算机、通信、控制等领域。设计组合逻辑电路需要遵循一定的步骤,以确保电路的正确性

2024-07-30 14:39:55 2311

2311 组合逻辑电路是数字逻辑电路的一种,其特点是输出只依赖于当前的输入状态,而与输入信号的变化历史无关。组合逻辑电路广泛应用于数字系统中,如计算机、通信设备、控制设备等。以下是对常用的组合逻辑电路的介绍

2024-07-30 14:41:37 4786

4786 的信号。理解它们之间的区别对于设计和实现复杂的数字系统至关重要。 第一部分:逻辑电路 1.1 定义 逻辑电路是一种电子电路,它根据输入信号的逻辑状态(通常是二进制的0和1)产生输出信号。逻辑电路的基本功能是实现布尔代数

2024-07-30 15:00:11 2196

2196 时序逻辑电路是一种数字电路,它根据输入信号和电路内部状态的变化产生输出信号。时序逻辑电路广泛应用于计算机、通信、控制等领域。 一、时序逻辑电路概述 时序逻辑电路是一种动态逻辑电路,其输出不仅取决于

2024-07-30 15:02:11 3422

3422 组合逻辑电路是一种基本的数字电路,它由逻辑门组成,用于实现各种逻辑功能。组合逻辑电路的结构特点主要包括以下几个方面: 无记忆功能 :组合逻辑电路的输出仅取决于当前的输入状态,与过去的状态无关。这与

2024-08-11 11:14:59 2617

2617 加法器不是时序逻辑电路 ,而是组合逻辑电路的一种。时序逻辑电路和组合逻辑电路的主要区别在于它们如何处理输出信号。 组合逻辑电路的输出仅依赖于当前的输入信号,而不依赖于电路之前的状态或输入历史。这

2024-08-28 11:05:51 2051

2051 时序逻辑电路是数字电路中的一种重要类型,其特点是电路的输出不仅取决于当前的输入,还取决于电路的状态。时序逻辑电路广泛应用于计算机、通信、控制等领域。 1. 引言 在数字电路设计中,时序逻辑电路是实现

2024-08-28 11:41:38 1914

1914 时序逻辑电路是数字电路中的一种重要类型,它不仅在计算机、通信、控制等领域有着广泛的应用,而且对于理解和设计现代电子系统具有重要意义。 1. 时序逻辑电路的基本概念 时序逻辑电路(Sequential

2024-08-28 11:45:49 5359

5359 时序逻辑电路确实具有记忆功能 。这一特性是时序逻辑电路与组合逻辑电路的本质区别之一。

2024-08-29 10:31:28 2362

2362

电子发烧友App

电子发烧友App

硬声App

硬声App

59632

59632

0

0 71

71 0

0 0

0 0

0 0

0 0

0 15

15 0

0 0

0 24

24 55

55 3923

3923

8346

8346

14015

14015

17873

17873 2982

2982

3921

3921 21951

21951

6913

6913

40174

40174

124120

124120

67768

67768

94951

94951

128321

128321

67995

67995

112182

112182

0

0 32851

32851 67228

67228 10796

10796

8978

8978

6454

6454

31

31 9

9 2709

2709

8000

8000 8731

8731

5503

5503

13635

13635 4297

4297 6631

6631 3132

3132 4403

4403 3067

3067 2311

2311 4786

4786 2196

2196 3422

3422 2617

2617 2051

2051 1914

1914 5359

5359

评论