芯片制造是个“点沙成金”的过程,一颗芯片从设计到诞生,经历了漫长的“旅行”。芯片制造有数百道工序,制造过程分为晶圆加工、氧化、光刻、刻蚀、薄膜沉积、互连、测试和封装八个步骤,涉及到的工厂有晶圆加工厂、Fab和封测厂。本文对芯片制造的基本步骤进行了简单梳理!

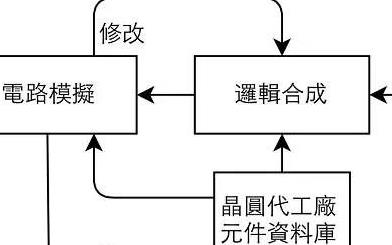

在《数字芯片是怎样设计出来的?》一文中,我们谈到,在芯片设计完成,交由芯片制造厂(Fab)进行试产(Tape out)之后,就可以进行量产了。但Tape out是个漫长的过程,在此过程中,Fab里的工艺及设备工程师们需要不断调试,使得芯片达到一定的良率。对于一个全新的产品,Fab要不断改善工艺,使芯片良率提高到80-90%,方可大规模量产。

芯片制造有数百道工序,制造过程分为晶圆加工、氧化、光刻、刻蚀、薄膜沉积、互连、测试和封装八个步骤,涉及到的工厂有晶圆加工厂、Fab和封测厂。其中,电子级的晶圆加工厂在国内占比较小,能做高端逻辑芯片的工厂只有台积电,但国内的封测厂现阶段已经比较成熟。

硅晶圆的生产

为什么我们要使用硅做半导体的原材料?因为硅的储量丰富且价格低廉,易于获取,硅还有着优良的热性能与机械性能;硅材料还具有易于生长成大尺寸高纯度晶体的特点,现在阶段,硅材料的工艺流程处在成熟的发展阶段。但硅材料的物理性质(禁带宽度、电子迁移速率、饱和速率等)限制了其在光电子和高频、高功率器件上的应用。随着高速信息产业的蓬勃发展,砷化镓这种半导体新材料迅速发展,因为镓的电子迁移率是硅的6倍多,其具有硅器件所不具有的高频、高速和光电性能,并可在同一芯片同时处理光电信号,被公认是新一代的通信应用材料。在本文中,我们谈到的的芯片原材料,仍围绕着硅材料展开。

晶圆加工的原材料是高纯度的硅,硅在自然界多以化合物形式存在,原材料加工工厂把石英沙经过冶炼去除杂质,经过物理提纯和还原,把化合物的硅变成电子级的多晶硅(99.999999%的硅含量)。由于多晶硅在光学、机械、力学、热学和电学性质方面不如单晶硅,所以要制造芯片,还需要把多晶硅变成单晶硅。展开来说,制作晶圆需要铸锭、切割和抛光三个步骤。在晶圆制造材料中,硅片占比为35%,市场规模可达上百亿美金。

◉ 铸锭

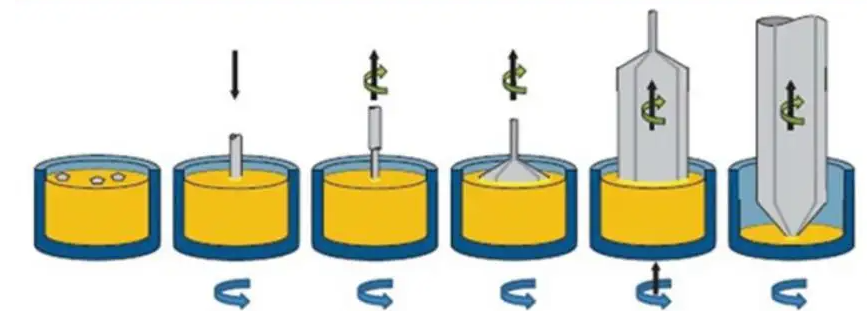

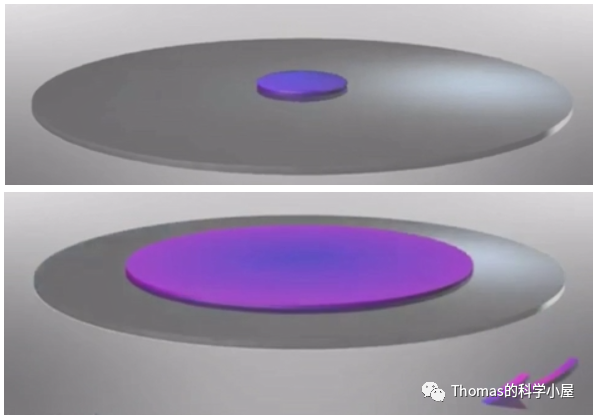

铸锭就是通过直拉法(Czochralski,CZ法)或区熔法(Floating Zone法,FZ法),把多晶硅拉成单晶硅棒的过程。具体而言,就是将电子级纯度的多晶硅放在石英坩埚中加热,得到硅溶液,把一根电子级高纯度硅棒放进硅溶液后,经过引晶、收颈、放肩、转肩、等径生长和收尾这些专业步骤,得到一根极高纯度的单晶硅棒。

铸锭的过程

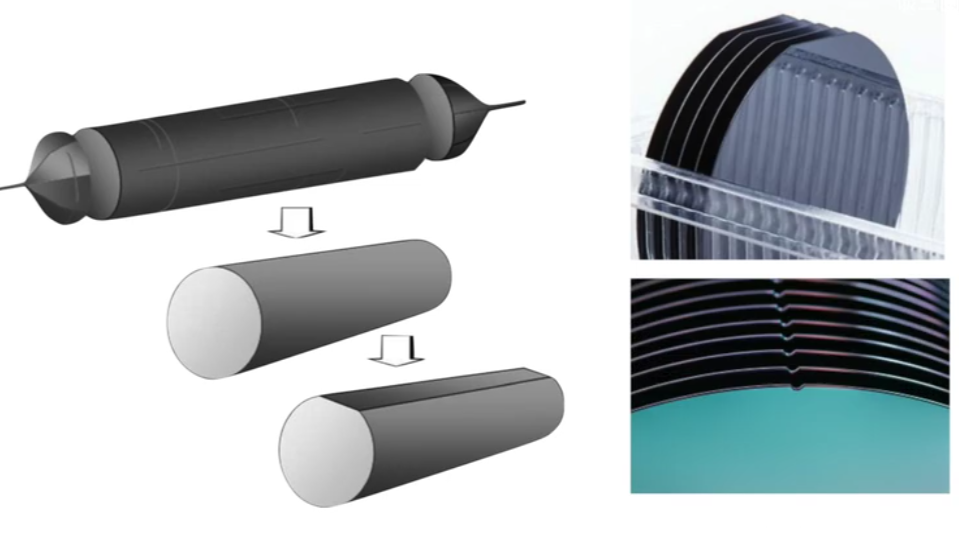

◉ 锭切割

由于直拉法无法获得一个完美的圆柱体,整个硅锭都会有尺寸的偏差,因此,这根生长出来的硅锭还需要修整和研磨。铸锭完成后,需要用金刚石锯切掉铸锭的两端,成为一个硅段,并经过滚磨后,得到目标尺寸;滚磨完成后,会在硅段的侧面再磨出一个平面或一道沟槽,这就是之后硅片上的定位边(flat,小于12寸)或定位槽(notch)。***需要通过定位边对硅片进行最开始的定位和校准。此外,定位边还可用来标明硅片的类型和晶向。接着把硅段切片,目前主流的方式是使用金刚线的多线切割机。

◉ 倒角

这一步是通过倒角机把硅片边缘的直角边磨成圆弧形,这样处理可以减少边缘崩裂的风险。同时,圆弧状的边还有两个优点:一是在光刻时,光刻胶是通过旋转的方式涂抹在硅表面上的,圆弧形的硅片边缘可以避免光刻胶因为离心力在边缘处累积造成厚度不均;二是在做外延生长时,沉积物会优先堆积在直角边,影响沉积较效果,而圆弧状的边可以消除边缘沉积的现象。

倒角示意图

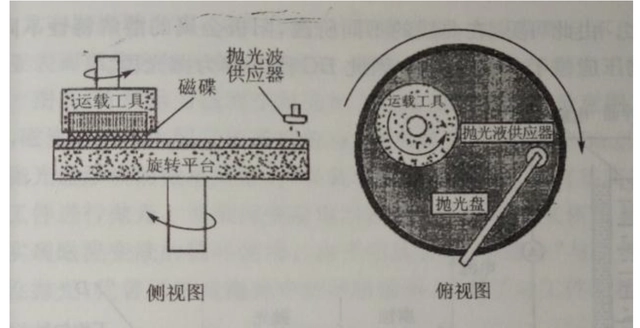

◉ 晶圆表面抛光

切割过后的薄片被称为“裸片”。能直接印刷电路图形的硅片,其光滑度和平整度要控制在1nm以内,就像影院的imax大幕布,起伏波动不能超过一根头发丝,所以裸片的表面还远远不能直接用来印刷电路图形。因此,需要用化学-机械抛光法(CMP)进行反复多次地抛光,抛光的过程涉及到抛光机、抛光液、抛光垫、后CMP清洗设备、抛光终点检测及工艺控制设备、废物处理和检测设备等。其中,抛光液和抛光垫占据整个CMP的80%以上价值。

晶圆表面抛光示意图

以上步骤就是为芯片的制造提供基础硅晶圆材料。目前全球90%以上的硅晶圆份额被日本信越化学(Shin-Etsu)、日本胜高科技(SUMCO)、台湾环球晶圆(Global Wafer)、德国世创(Siltronic)、韩国SK Siltron(原LG Siltron)五家企业瓜分。其他的硅晶圆厂商还有法国Soitec、芬兰Okmet、台湾合晶(Wafer Works)、台湾嘉晶(Episil)等;国内较为知名的硅晶圆厂商有上海新昇半导体科技有限公司、浙江金瑞泓科技股份有限公司、天津市环欧半导体材料技术有限公司、 安徽易芯半导体有限公司、合晶科技股份有限公司(台湾合晶投资)、宁夏银和半导体科技有限公司等。

氧 化

当每块磨得比镜子还光滑万倍的硅片送到fab厂,就开始了它们成为芯片的旅程。在给芯片印刷电路板前,需要给它加一层保护膜,即氧化。氧化的过程会在整个芯片的制程中反复多次进行。不同的工艺、器件上做表面氧化处理的目的不同,例如需要沉积大应力薄膜、进行深刻蚀等。氧化过程的第一步是去有机物、金属等杂质及蒸发残留的水分。清洁完成后就可以将晶圆置于数百上千度的高温环境下,通过氧气和蒸气在晶圆表面的流动形成二氧化硅层。热氧化过程可分为干法氧化和湿法氧化,前者使用纯氧产生二氧化硅层,速度慢,但氧化层薄而致密;后者需同时使用氧气和高溶解度的水蒸气,其特点是生长速度快,但保护层相对较厚且结构略粗糙。实际生产中,一般会用“干氧氧化+湿氧氧化+干氧氧化”这样常规三步热氧化模式,既保证了二氧化硅表面和界面的质量,又解决了生长速率的问题。

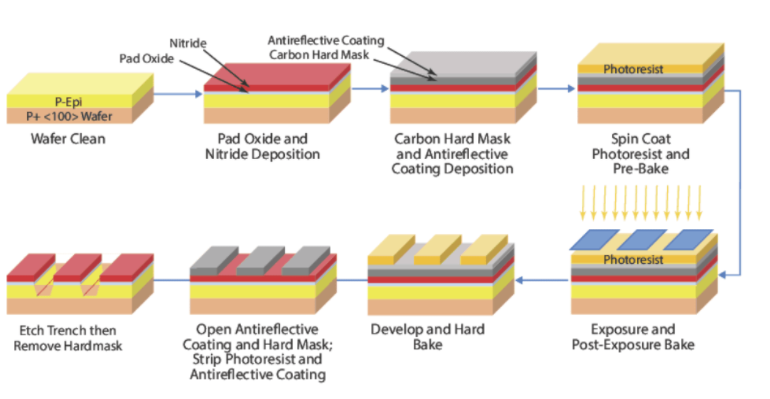

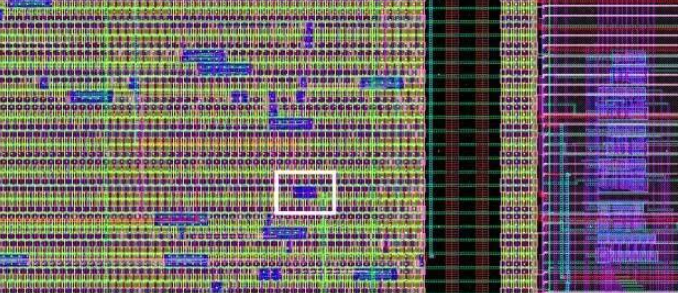

光 刻

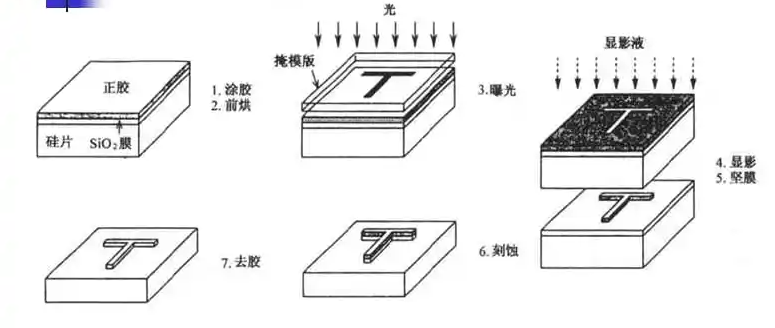

“光刻”是制造芯片的基础,光刻可分为涂覆光刻胶、曝光和显影冲洗三个步骤。光刻工序需要***、光掩膜和光刻胶。光掩膜是芯片的蓝图,是一张有集成电路版图的玻璃遮光板。一块先进制程的硅片上,需要用到数百张掩膜。***就像纳米级的打印机,将光掩膜上的图形投射在硅片上,光刻胶则是能把光影化为现实的一种胶体。

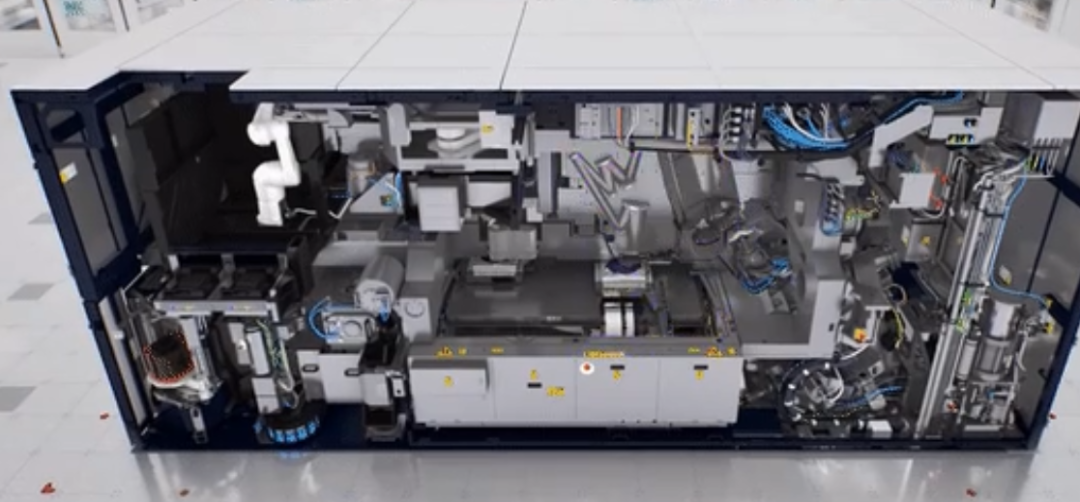

荷兰ASML的***

◉ 涂覆

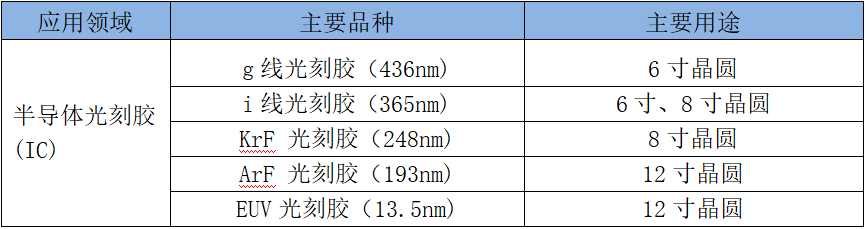

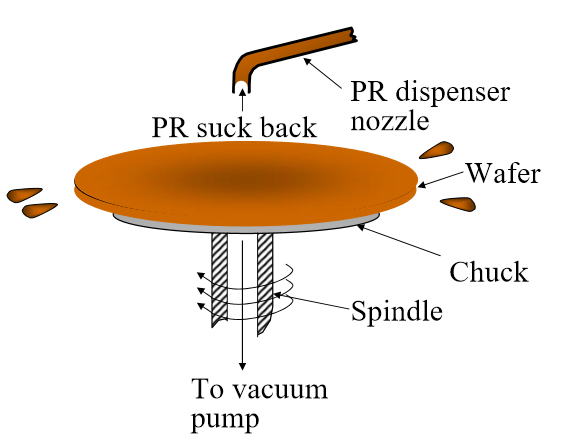

涂覆就是给硅片涂光刻胶,可以理解为:涂上了光刻胶的晶圆就像一张张“相纸”。光刻胶被从容器中取出滴布到置于涂胶机中的晶圆表面,晶圆高速旋转,光刻胶在离心力的作用下向边缘流动。光刻胶有正胶和负胶之分,凡是特定波长的光照过的地方,胶水可以被去除的就是正胶;如果产生了交联反应,光照的地方坚挺,未被照过的地方能被去除的是负胶。晶圆表面的光刻胶层越薄,涂覆越均匀,可以印刷的图形就越精细。涂胶过程中,要严格控制转速和排风大小,以防止任何细微的气泡产生。此外,甩到硅片边缘的胶体一定需要切割和磨边,尽量减少光刻胶在硅片边缘的沉积。光刻胶在晶圆制造材料中,约占有6%的市场份额,约有20多亿美金的市场,虽然光刻胶占比不大,但是却饱含着极高的技术含量,其中日本光刻胶厂商在这个领域占据了大部分市场份额,尤其是在Arf(12寸晶圆制程)光刻胶市场,日本企业几乎占据了全球百分之九十以上的市场份额。

涂覆示意图

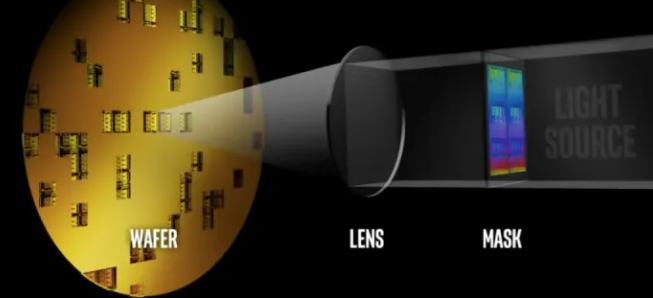

◉ 曝光

晶圆均匀覆盖光刻胶薄膜后,需要烘烤以增加光刻胶粘性。在100℃左右的炉子或者铁板上烘烤一分钟后,***就上场了。这个步骤如同相机照相一样,相机拍摄的照片是印在底片上,而光刻则是把光掩模上的电路图复刻到硅片上那一层薄薄的光刻胶上。光刻胶只要遇到了光,就会发生分解或交联作用,再经过***的曝光,在一张晶圆上就会形成成千上万的沟槽,在曝光过程中,印刷图案越精细,最终的芯片就能够容纳更多元件。

在***的领域,要高度的光学和电子工业基础,因此最早的***市场被日本的佳能、尼康占据,而荷兰的ASML凭借台积电科学家林本坚发明的“浸入式光刻技术”方案,成功将光源波长一举从193nm缩短到132nm。随后ASML又加入了由Intel和美国能源部牵头组建EUV LLC前沿技术组织,至此,尼康、佳能逐渐失去了***的市场,国际上技术最先进,最主流的***市场被ASML牢牢占据。而分辨率在数微米以上的***,则主要有德国SUSS、美国MYCRO NXQ4006、以及中国的一些品牌品牌,这些***主要用在生产线和研发上。

目前备受瞩目的新技术是极紫外光源(EUV)光刻技术。在这道工序中起作用的***,也是整个芯片制程中最关键的设备。以头ASML为例,一台价值10亿的***里,包含了10万个零部件,需要上游5000多家供应商协作;这台***中也蕴藏了众多人类工程学的诸多巅峰之作。例如:表面起伏不超过0.05纳米Zeiss透镜,是地球文明最接近三体水滴的得意之作;能同步对准和曝光的双工件台系统,是阿斯麦法成为顶级***厂商的法宝之一;TRUMPF和ASML、Zeiss合作研发的,每秒可以把5万个液态锡滴轰成等离子体的激光放大器,则是产生EUV的关键。

曝光示意图

◉ 显影冲洗

从***出来后还要经历曝光后的烘焙,简称后烘。这一步的目的是通过加热让光刻胶中的光化学反应充分完成,可以弥补曝光强度不足的问题;同时还能减少光刻胶显影后由于助驻效应产生的一圈圈纹路。后烘可以把之前曝光的部分溶解清除,光掩膜上的图形就浮现在了光刻胶上,这就是显影和冲洗。之后的步骤是浸润硅片,涂显影液,再去除多余光刻胶,从而让印刷好的电路图案显现出来。显影完成后需要通过各种测量设备和光学显微镜进行检查,确保电路图绘制的质量。一张硅片要反复经过上千次这样的操作,才能雕刻出数以亿计的电子细节及其对应的电路连接,最终成为一枚小小芯片。

目前,整个光刻流程所必需的***、光刻胶和光掩膜,国产替代程度都很低。

显影冲洗示意图

刻 蚀

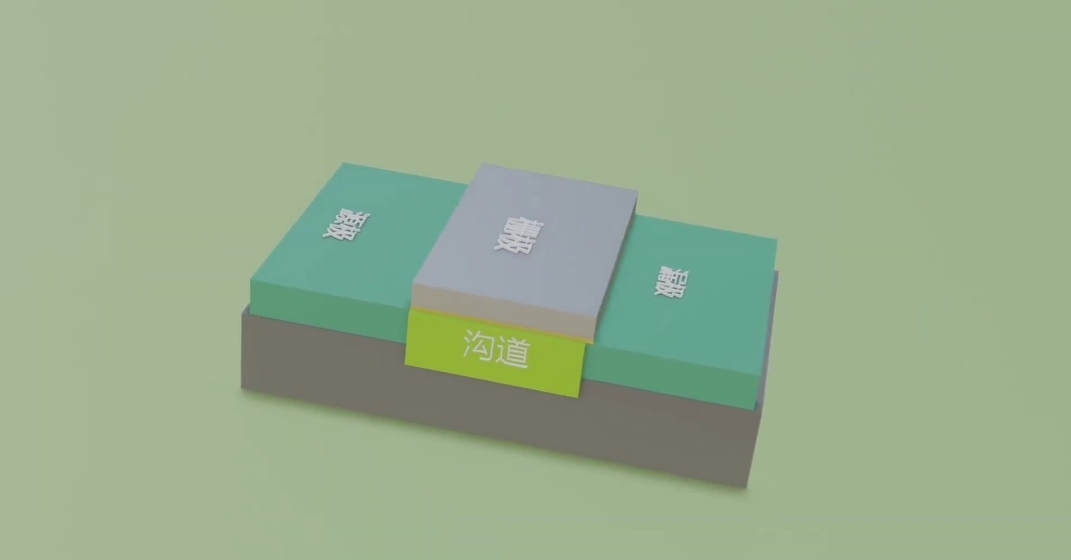

在晶圆的光刻胶上完成电路图的光刻后,需要先掺杂。纯净的硅是不导电的,所有的电子都束缚在硅原子的周围,掺杂也就是改变硅片的电学特性,让这块硅片获得所需的电学参数。掺杂的方式主要有扩散和离子注入,两种方法互补使用,扩散可应用于形成深结,离子注入可形成浅结。接着,就要用刻蚀工艺去除多余的氧化膜,只留下半导体电路图。刻蚀有两种方式:一是使用液态化学品的湿法刻蚀,让硅片在强酸强碱的中“泡澡”;另一种是使用气体等离子体的干法刻蚀,让硅片在化学气体的离子轰击下局部“瘦身”。使用化学溶液去除氧化膜的湿法刻蚀具有成本低、刻蚀速度快和生产率高的优势,但这种方法的精度较低,如今干法刻蚀已经被广泛使用,以提高精细半导体电路的良率。保持全晶圆刻蚀的均匀性并提高刻蚀速度至关重要,目前最先进的干法刻蚀设备正在以更高的性能,支持最为先进的逻辑和存储芯片的生产。

芯片的刻蚀机市场方面,美国泛林半导体市场占有率是全球第一,日本的东京电子的ccp(capacitive coupled plasma 电容耦合)刻蚀机占到全球出货量的一半,美国应用材料公司是刻蚀机多应用在尖端存储器和逻辑芯片上,中国的中微公司和北方华创是后起之秀,其中,中微公司的5nm刻蚀机是国内唯一一家被台积电所认可的设备厂商;北方华创的硅刻蚀技术一家突破了14纳米。

蚀刻示意图

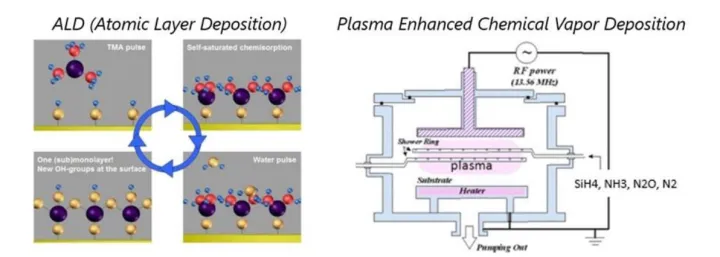

薄膜沉积

以上步骤是给芯片“挖沟槽”,挖好了沟槽,就要添加一些材料将不同的器件分离开来。这时需要不断地沉积一层层的薄膜并刻蚀掉多余部分,就如乐高积木一样层层搭建。将这些厚度小于1微米的薄膜放到晶圆挖好的沟槽的过程就是“沉积”。先进的制程需要在晶圆表面反复交替堆叠多层薄导电膜和绝缘膜,再通过刻蚀工艺去除多余部分并形成三维结构。所以整个芯片的制造流程,有很多步骤都是要反复进行的。可用于沉积过程的技术包括化学气相沉积 (CVD)、原子层沉积(ALD) 和物理气相沉积(PVD),采用这些技术的方法又可以分为干法和湿法沉积两种。

原子层沉积(ALD)示意图

在以上的制程里,主要的设备、材料的供应商大多都欧美、日韩的企业,我国这些年也涌现除了不少优秀的半导体设备厂商,虽然在市场份额上和欧美、日韩企业无法相提并论,但近几年,国产半导体设备厂商通过自主研发,已在多个工艺制程中实现了设备的国产化替代,并进入产业化量产阶段,在半导体设备的专题中,我们将会详细讨论国内外半导体设备的对比。

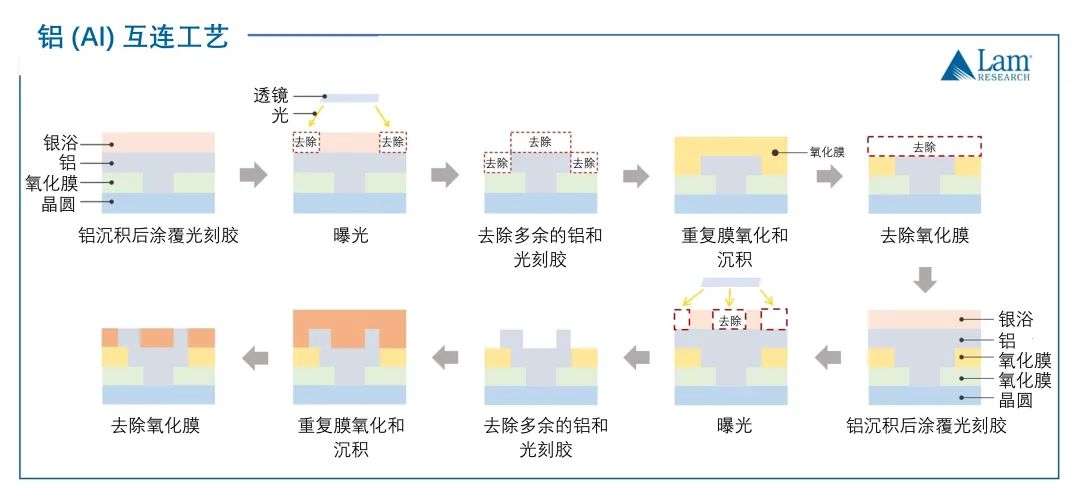

互 连

要实现电与信号的发送与接收,还要把通过沉积构建的晶体元件连接起来。用于半导体的金属需要满足以下条件:低电阻率、热化学稳定性和高可靠性,同时还要低成本,所以互连工艺主要使用铝和铜这两种物质。随着半导体工艺提升和芯片尺寸的缩小,铝电路的连接速度和电气特性逐渐无法满足要求,铜已经替代铝成为互连工序的主要材料。

测 试

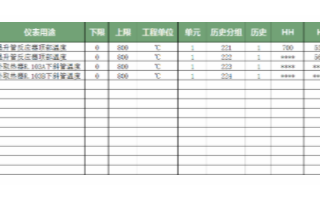

测试的主要目标是检验半导体芯片的质量是否达到一定标准,从而消除不良产品,并提高芯片的可靠性。此外,经测试有缺陷的产品不会进入封装步骤,有助于节省成本和时间。电气参数监控(EPM)是半导体芯片测试的第一步。该步骤将对半导体集成电路需要用到的每个器件(包括晶体管、电容器和二极管)进行测试,确保其电气参数达标。EPM的主要作用是提供测得的电气特性数据,用于提高半导体制造工艺的效率和产品性能。晶圆老化测试:将晶圆置于一定的温度和AC/DC电压下进行测试,由此找出其中可能在早期发生缺陷的产品,测试完成后,需要用探针卡将半导体芯片连接到测试装置,之后就可以对晶圆进行温度、速度和运动测试以检验相关半导体功能。

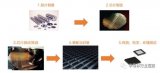

封 装

经过之前几道工艺的处理,现在的晶圆上已经形成数百片大小相等的方形芯片。接着,把这些小方片切好,便可以得到一颗颗用于各种设备上的芯片。当然,这些刚切割下来的小方片是很脆弱的,还不能交换电信号,需要进行封装后,才能形成芯片。封装是指在半导体芯片外部形成保护壳,并使得它们能够与外部交换电信号。整个封装制程分为五步,即晶圆锯切、单个晶片附着、互连、成型和封装测试。

芯片制造是个“点沙成金”的过程,一颗芯片从设计到诞生,经历了漫长的“旅行”。本文对芯片制造的基本步骤进行了简单梳理,实际上,芯片的制程要复杂得多,越先进的制程,就有着越复杂的工艺,每一步都凝结着人类智慧的结晶。

编辑:黄飞

电子发烧友App

电子发烧友App

评论