设备、材料和封装技术的进步都会导致问题。

汽车供应链上的企业遍布全球,越来越多的企业将自身的非核心业务外包给第三方企业,因而汽车供应链的结构也更加复杂化。但是,汽车供应链日益全球化,复杂化,多级化,精益化的特点,以及车企和供应链对精益生产的追求和运营的精细化,导致供应链本身的弹性不足,这增加了汽车供应链网络运营环境的不确定性。

对于每个新节点,都必须考虑额外的物理影响,但并非所有这些影响都具有相同的关键级别。这些影响里被更频繁提及的一种是自热。

所有设备都会消耗电力,当它们这样做时,它就会变成热量。“本质上,所有有源器件都会在载流子移动时产生热量,从而为电流通过栅极创造通道,”西门子 EDA Calibre 设计解决方案集团 DRC 应用营销总监 John Ferguson 说。“在历史悠久的 CMOS 时代,这些影响在很大程度上是可控的,因为在栅极捕获的热量有一条相对简单的路径可以通过硅衬底消散。不幸的是,CMOS 方法最终遇到了物理限制,在这种情况下它无法继续在可靠运行的同时持续缩小尺寸。”

缩放比例也有影响。“直到 20 世纪 90 年代,这个问题还不是问题,”Synopsys TCAD 产品组的研究员 Victor Moroz 说。“那是因为人们能够降低电源电压,这确实有助于降低功耗。但一旦人们发现技术的局限性,就无法将电源电压降低到远低于 0.7V 左右。”

自热与活动有关。Cadence 产品管理总监 Jay Madiraju 表示:“芯片最活跃部分的自热效应最高,这给设计人员带来了额外的瓶颈。”“当电路运行时,设备和互连的温度会根据活动量增加。当设备在运行过程中消耗功率时,它会产生热量。类似地,对于金属互连,温度升高将由在互连中流动的电流通过电阻损耗产生热量(即焦耳热)引起。这两个因素都会导致产生热量。”

收缩使事情变得更糟。“随着设备和电线的几何尺寸减小,电流密度增加,”Lightelligence 的物理设计负责人 Rob Kuhn 说。“这加剧了自热及其对性能和可靠性的相关影响。同样在高级节点中,finFET 和纳米线器件会进一步增加自热,因为导热性会降低并且热量会长时间滞留在器件附近。”

材料有影响。“制造器件所用材料的变化导致热效应进一步增加,”Cadence 的 Madiraju 说。“例如,低 K 电介质比以前的金属间电介质具有更高的热阻。自热开始成为 65nm 以下传统节点设计的一个问题,并且随着特征尺寸的缩小而变得更具挑战性,特别是对于先进节点工艺,即 finFET 设计。”

形状也会产生问题。Ansys 研发总监 Tianhao Zhang 表示:“FinFET 新型三维结构的自热效应比平面器件更为显著。”“此外,finFET 结构中使用的材料的导热性差,以及难以从被介电材料包围的隔离鳍片散热到基板,导致 finFET 器件的温度更高。反过来,这会对互连线造成更高的热耦合效应。”

虽然缩放有助于解决一些问题,但其他问题会变得更糟。Synopsys 的 Moroz 说:“自 finFET 推出以来,功率密度变得足够大,人们注意到并开始担心它。”“晶体管密度每年增加大约 10% 到 15%。一个晶体管的功耗降低很慢,因为人们在一点一点地改进技术。当你减少几何形状时,电容也会减少。功耗主要与电容有关,因为所有电路都在切换。无论何时切换,都必须为电容充电,而该电容来自你要切换的下一个晶体管。每次给它充电或放电时,能量都会沿着其他组件(电线)传递。因此,当你减小晶体管尺寸时,晶体管电容会减小,从而帮助降低功耗。而且因为它们更小,它们之间的电线变得更短,这也有帮助。但它跟不上密度的提高,总的来说你会看到你的功率密度在不断增加。”

当设备产生热量时,热量会通过封装、电路板和散热器散发出去。西门子的 Ferguson 说:“新材料和与硅散热器直接相互作用最少的非常薄的层增加了热阻。”“这使得散热变得更加困难。因此,设备被迫在更高且可能增加的温度负载下工作。这些高温会影响器件的阈值电压和性能,最终导致可靠性挑战。3D-IC 设计的趋势可能会进一步加剧这个问题,进一步增加总散热路径。”

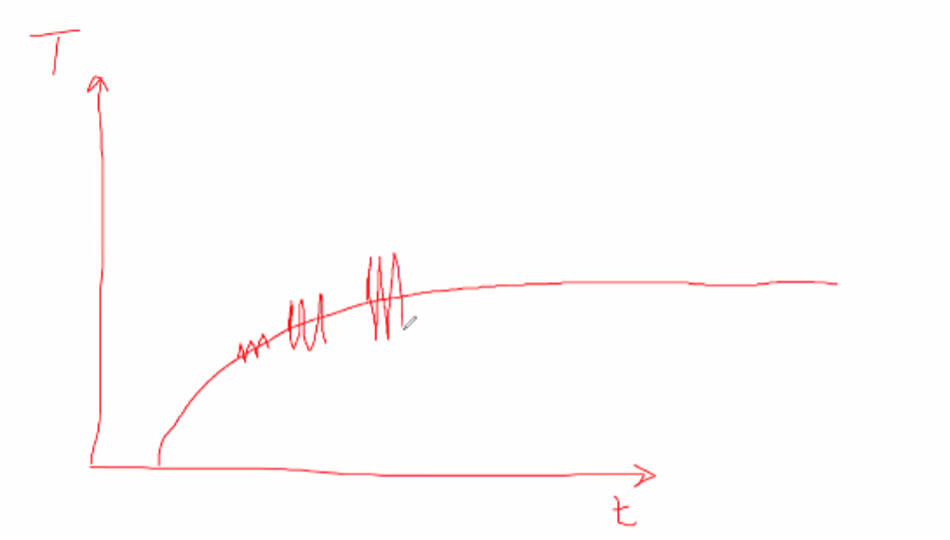

热量的产生和散热必须平衡。“考虑图 1(下图),”Moroz说。“在某个时候,你开始操作设备,温度会上升,直到它饱和并在这个平衡点变得稳定。这是因为你必须管理芯片的功率预算,以免整个芯片过热。如果查看单个开关,并从一个平面晶体管(在左侧)开始,它会打开然后关闭。在局部,晶体管温度会先高后低,再高又低。当人们改用 finFET(中)时,总体上没有任何变化,因为它仍然取决于你的功率预算和电路活动以及封装的散热能力。但是finFET有一个窄鳍,与平面相比,它的导热和散热能力不如平面,因此局部温度会升高。现在人们正在改用环栅(右),热量更难从它们中逸出,因为它们很小并且被不导电的东西包围着。所以在本地,有一个更大的问题。但对于芯片规模,没有任何改变。”

图 1:芯片温度和自热。

热量是芯片的杀手。即使温度没有高到足以毁坏设备,该设备也会受到长期影响。“对于设备而言,自热会影响迁移率和阈值电压,这反过来会限制设备性能并增加功耗,”Lightelligence的 Kuhn 说。“热载流子注入、随时间变化的电介质击穿 (TDDB) 和负偏置温度不稳定性 (NBTI) 会降低设备的长期可靠性。电线的固有电阻随着温度的升高而增加,这会通过减慢数据传输来影响芯片性能。随着时间的推移,自热还会加速电迁移效应,从而导致芯片故障。随着技术的进步,这两种趋势都会恶化。”

行动计划

与所有问题一样,越早了解问题,处理起来就越容易,成本也就越低。过早老化设备的问题不仅需要对设计采取纠正措施,还需要成本更高的现场更换有缺陷的部件。

Ferguson概述了三个总体原则:

对设备行为的热影响进行建模,以准确模拟预制造

使用任何和所有方法来减少总热影响

寻找替代的消散路径

“由于对芯片可靠性和性能的高度不利影响,对任何芯片或系统级封装 (SiP) 的热流进行建模至关重要,”Kuhn 说。“Ansys 和 Cadence 等公司提供的工具在这一领域变得越来越重要,因为它们使设计人员能够识别可靠性和性能问题,并通过增加导线尺寸(降低电阻)和提高基板导热性等技术来缓解这些问题”

所有分析都从模型开始。Cadence 高级产品经理 Art Schaldenbrand 表示:“设备建模[CMC] 已经认识到考虑自热的必要性,最近的设备模型 BSIM-C 和 BSIM-I 包括自热效应。”“这些模型连同模拟器的增强功能,可以计算设备和互连中消耗的功率。代工厂通常会为高级节点工艺提供具有自加热功能的模型。设计人员在使用 SPICE 仿真时可以考虑自热对其设计的影响,从而深入了解电路性能由于其操作而发生的变化。虽然设计人员可以在仿真中包含自热效应,但存在仿真性能成本,因此他们需要在如何分析热效应方面具有战略意义。

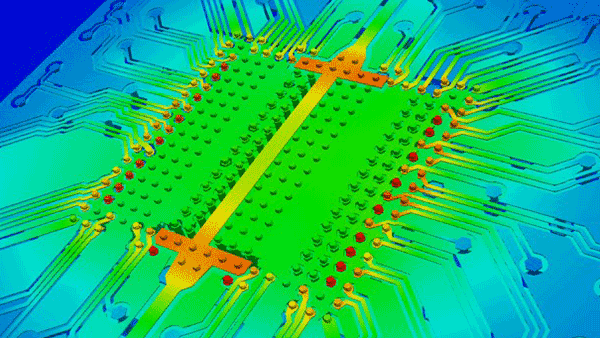

图 2:IC 封装互连结构的温度曲线。来源:Cadence

其他简化可能导致悲观的结果。“芯片上均匀的最坏情况环境温度通常过于悲观,”Ansys 的 Zhang 说。“要获得准确、高分辨率的结果,甚至基于金属层的环境温度,以及自热是分析电路可靠性所必需的。”

模拟晶体管自热是否足够?“你产生的热量与阻力成正比,”Moroz说。“对于电线,每微米会有几十欧姆。如果查看信号网,它就是将开关连接到下一个开关的电线。这通常是几微米长,而该网的电阻将是几百欧姆。一个晶体管,它有两种状态。两个阶段之间有一个瞬态,但两个状态是开和关。在关闭状态下,它具有兆欧姆电阻。在开启状态下,通常它具有几千欧姆的电阻。它支配着导线电阻。所以,如果一根电线是 100 欧姆,而你的开关是 10 千欧姆,那么电线会产生热量,但要少 100 倍。”

虽然信号线的自热本身可能不是问题,但热耦合会增加这些温度。Ansys 的 Zhang 表示:“电线的更高温度对可靠性构成了挑战,因为为这些电线定义了更小的允许电流以满足预期的平均无故障时间 (MTTF)。”“这是电迁移造成的故障,随着时间的推移会产生不希望的开路或短路。”

电力网络中的电线有不同的问题。“电源网络比信号网络复杂得多,”Ansys 产品营销总监 Marc Swinnen 说。“信号线是点对点或多点的,但电力网是网格。你无法使用相同的求解器来求解它。你必须使用类似SPICE 的电路模拟器。网络很大。在一个有 500 亿个晶体管的芯片上,你有 500 亿个电源和接地点需要连接。这比整个美国的电网还要复杂。每一小段电线都必须建模为一个电阻器,所以有数千亿个电阻器,必须减少数量才能模拟它。只有这样才能准确判断电流流向何处以及每个点的电压。EM 分析是免费的——这是一个可靠性问题,但你需要知道流过所有电线的电流。这也与温度有关,因此需要了解全球温度,而这取决于散热器和环境。但是整个芯片的温度各不相同。过去它被认为是整个芯片的单一温度,但现在我们需要进行热建模并包括焦耳自热。”

减少供暖影响的最直接方法是减少活动。这通常被称为暗硅。“高端服务器封装每平方厘米可耗散约 50 瓦,”Moroz说。“关键是你在芯片上使用一小部分开关,不要超过它。否则,它会过热。如果你看看今天的技术,你可以用大约 1% 的活动因子来实现这种功耗。这听起来可能很糟糕,但它正在变得更糟,并且在一点一点地下降,每年下降 5% 或 10%。”

这一切都始于早期的系统分析。“了解你的功率预算始于复杂的芯片-封装-电路板协同设计,”Zhang 说。“后期的热问题会导致大的 ECO 循环、难以解决的问题,甚至是设计失败。为了克服这个问题,应在早期设计阶段考虑热效应,包括热感知功能块放置和热热点评估。这种考虑不仅有助于产生最佳设计,还有助于降低自热影响并提高整体设计可靠性。”

散热变得越来越困难,尤其是对于多芯片系统。“你有一些凸点将芯片连接到电路板,”Moroz说。“然后有一些散热器可以帮助你散热。中间有硅,它是一个很好的导热体,所以各处的热量会很均匀,你就等着封装散热。现在,如果拿起那块芯片,开始在上面堆东西,这种材料的热导率是多少?如果它是电介质,那就是个问题,因为它是热逃逸的额外屏障,所以必须确保电介质没有那么糟糕。”

结论

自热可能不是当今电路设计人员面临的最大问题,但问题已经增长到足以引起人们的关注,而且它们在未来只会变得更糟。新设备、新材料和新封装技术都在加速这个问题,如果最大活性因子继续下降,任何封装中都会面临这个问题。

编辑:黄飞

电子发烧友App

电子发烧友App

评论