高性能计算、人工智能等应用推动芯片的技术节点不断向前迈进,导致设计、制造的难度 和成本问题凸显,针对这一问题,Chiplet 技术应运而生。Chiplet 技术是将复杂的系统级芯片按 IP 功 能切分成能够复用的“小芯片 (芯粒)”,然后将执行存储和处理等功能的小芯片以超高密度扇出型封 装、2.5D 和 3D 高端性能封装进行重新组装,以实现高性能计算对高带宽、高性能的要求。介绍了上 述封装的多样化形式和通信协议,分析其重要的电连接结构与工艺难点,及其在可靠性方面的一些问题。

引言

高性能计算、人工智能、5G 通信、数据中心和云计 算的快速发展使芯片的技术节点不断向前推进,单颗 芯片上集成的晶体管数目已超过百亿级。与此同时, 将更多功能集成在单颗芯片的难度不断增大,设计与 制造的成本不断上升。与 90 nm 技术节点相比,3 nm技术节点的投资成本增加了 35~40 倍,仅英特尔 (Intel)、台积电(TSMC)和三星(Samsung)3 家头部企 业参与其中。5 nm 技术节点的设计成本超过 5 亿美 金,约是 28 nm 的 10 倍。为解决上述问题,出现了 Chiplet 概念。

Chiplet 作为一种设计概念,指将单颗集成复杂功 能的片上系统级芯片(SoC)离散成多颗特定功能的小 芯片(Chiplet,又称“芯粒”),再采用封装技术将其整合 在一起,构成多功能的异构系统级封装(SiP),以持续 提高器件算力,缩短产品开发周期,提升产品良率,降 低整体成本。近年来,受限于高端设备和材料的能力 等,以 Chiplet 方式将处理芯片与存储芯片封装集成的 技术越来越重要。目前,TSMC、Intel、Samsung 等均已 发布相关产品,通过高密度(≥16 /mm2)和窄节距(≤ 130 μm)的输入 / 输出接口(I/O)为处理芯片与存储芯 片提供定制化的封装,以应对高性能计算、人工智能、 数据处理等前沿行业的要求。市场研究公司 Yole 根 据产品的终端应用特点,将为追求最优计算性能而采 用的先进封装平台技术归类为高端性能封装,高端性 能封装主要包括超高密度扇出型封装(UHD FO)、嵌 入硅桥技术、2.5D 硅转接板技术、3D 存储堆叠和混合 键合技术。加入封测行业交流群,加VX:tuoke08。2021—2026 年,全球封装市场总额预计将 达到 960 亿美元,复合年增长率保持在 3.8%。同时, 先进封装的营收将超过传统封装。而以 FO、2.5D 和 3D 封装为代表的高端性能封装,在人工智能、5G 通信 和高性能计算等产业的推动下,其复合年增长率将超 过 10%,呈现高速增长的态势。

本文介绍了高端性能封装的主要技术形式,剖析 了其结构的特点,分析了其在设计、工艺和可靠性测 试方面所面临的挑战。

2 高端性能封装的结构

高端性能封装主要以追求最优化计算性能为目的,其结构主要以 UHD FO、2.5D 和 3D 先进封装为 主。在上述封装结构中,决定封装形式的主要因素为 价格、封装密度和性能等。

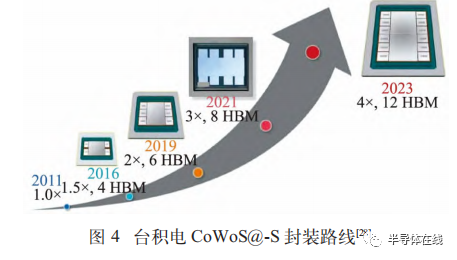

由 TSMC 在先进封装上的主要业务可知,推动高 端性能封装的主要项目为高性能计算与高带宽存储, 其代表结构为基于硅转接板的芯片在晶圆基板上的 封装(CoWoS@-S),是一种典型的 2.5D 封装结构。该 结构将处理芯片和存储芯片平铺在硅转接板上,采用 线宽 / 线间距为 0.4 μm /0.4 μm 的金属布线将其互 连。TSMC 突破光罩对硅转接板面积的限制,结合集成 芯片的数量,制定了其在 2.5D 封装上的发展路线。 Intel 和 Samsung 在 2.5D 封装上,也具有类似的封装结构。对于 2.5D 封装而言,硅转接板可提供亚微米 级高密度布线,能够显著提升多芯片的组装密度。随 着高带宽存储芯片的数据传输效率逐步提升,采用 2.5D 封装连接存储芯片和处理器芯片将成为主流的 选择。然而,硅转接板采用前道晶圆制造的设备和工 艺,制作成本相对昂贵。为此,一些企业在 FO 封装的 基础上进一步深耕,开发出多样化的结构,以满足一 些稍低端产品的需求。

FO 通过晶圆重构技术,将多颗相同或不同的芯 片灵活组合起来,以实现多芯片集成的目的。在此基 础上,FO 采用高密度布线有机层、硅桥和高速基板等 来提升器件的性能,衍生出了 2D、2.1D、2.2D 和 2.3D 封装结构,以实现超高密度 I/O 的连接。由于 FO 主要采用高分子材料来制造芯片间的微米级布线,其 自身的线宽 / 间距的尺寸极限也相对明显。为进一步 缩小 FO 封装的布线尺寸,新的设备与材料有待开发, 同时,封装成本也将大大提高。因此,FO 封装主要应 用在性能相对较低的存储器与处理器芯片上。

在高端性能封装中,处理芯片和存储芯片对高带 宽、低延迟有严格的要求,3D 封装是最理想的方案。目 前,常见的 3D 封装结构为存储芯片间垂直互连以及 存储芯片与逻辑芯片间的连接。在上述结构中,除采 用微凸点的芯片堆叠(C2C)和晶圆上芯片(C2W)工艺 外,基于硅通孔和混合键合(HB)的无凸点工艺实现了 异构异质芯片间的最短距离互连,将器件性能提至最 优,其投资成本也最高。预计在 2023 年,TSMC 采 用 HB 的集成芯片系统封装(SoIC)将率先实现量产。

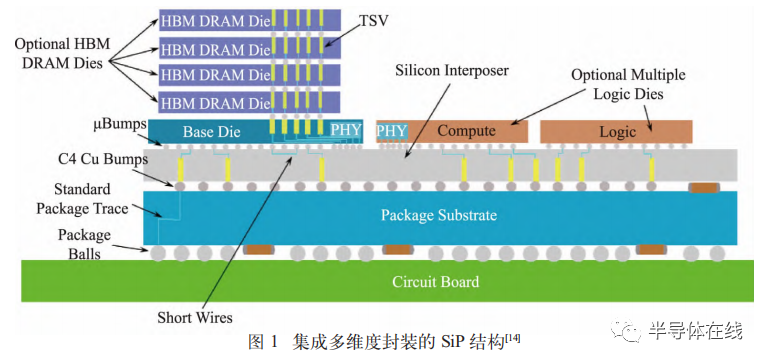

随着高端性能封装技术的发展,不同维度封装结 构间的界限将变得模糊,将其集合成一个系统的 SiP 会变得普遍,图 1 为集成多维度封装的 SiP 结构示意 图。例如 Intel 的最新产品 Ponte Vecchio 集成了嵌入 式多芯片互连桥接技术(EMIB)和逻辑晶圆 3D 堆叠 技术(Foveros);TSMC 的 SoIC 也可与 CoWoS 和集成 扇出型叠层封装(InFO-PoP)相结合并共同使用。上述 结构可以实现器件对性能的极致追求,同时,多颗处 理芯片的集成也为器件的热耗散带来巨大挑战。

3 高端性能封装的通信协议与设计

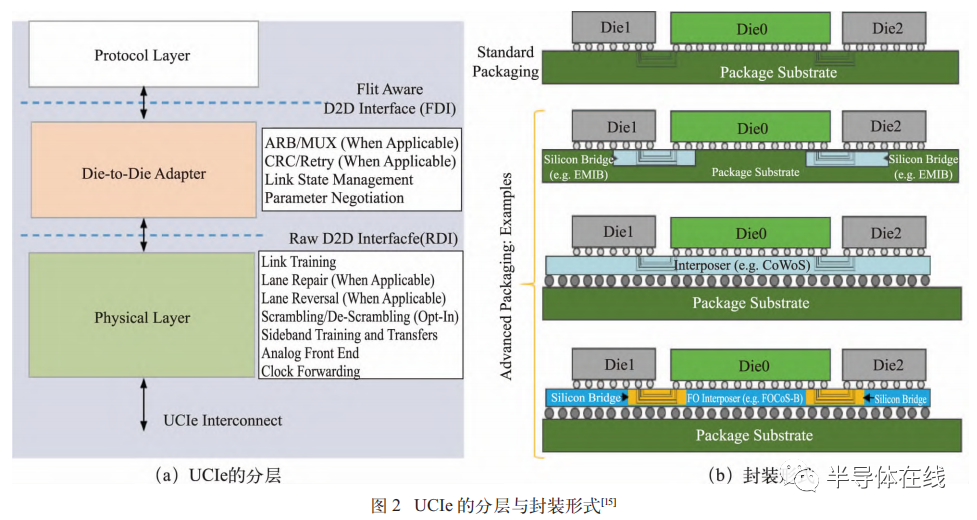

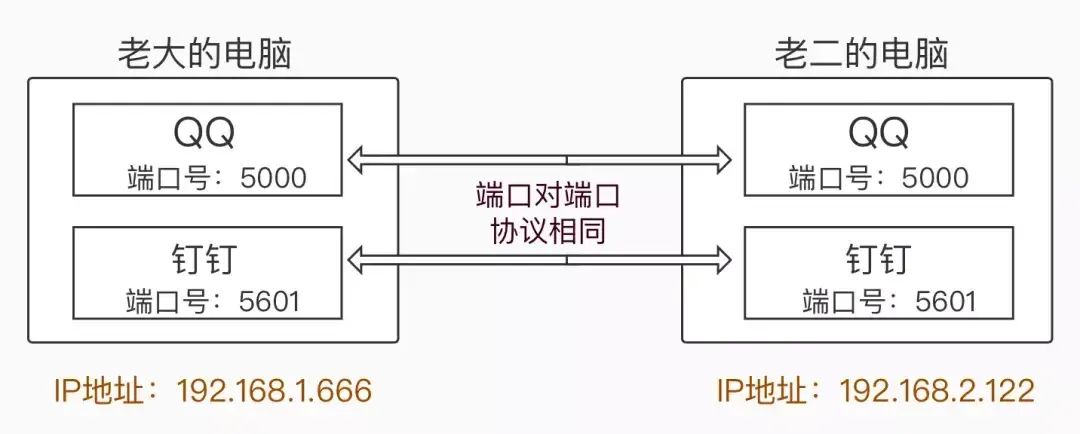

在高端性能封装结构中,多颗特定功能的芯片(Die)被集成在单个系统之中,上述芯片的连接已成为 迫切需要解决的问题。Intel 公司开发了一种开放性的 通用小芯片互连技术(UCIe),为异构的小芯片间提供 了高带宽、低延迟、高电源效率和高性价比的封装连接。该标准结合外围元器件互连总线标准(PCIe)、计 算链接协议(CXL)和软件基础设施来确保互操作性, 使得设计者能够对不同来源的芯片进行封装,UCIe 的 分层与封装形式如图 2 所示。

UCIe 技术标准提供了协议层、适配器和物理层。芯片与芯片间的适配器为 Chiplet 提供链路状态管理 和参数协商。物理层提供电信号、时钟、链路训练、边 带、电路架构和封装互连通道等。上述技术适用于标 准的 2D 封装和先进的 2.5D 封装。在先进的高端性能 封装中,处理芯片对信道宽度最为敏感,其与存储芯 片的数据发射与接收端沿芯片的边缘放置,双向的导 线长度也保持一致,这样不仅简化了电路设计,还大 大降低了信道带宽的损耗。随着处理芯片对带宽要求 的进一步提升,存储芯片的 3D 封装得到发展,与之相 应的 UCIe 标准还需不断升级,扩展到 3D 封装互连。

在国内,中国计算机互连技术联盟联合数+家企 业和科研院所制定了应用计算机系统芯片内、芯片 间、系统间互连技术的协议规范和标准,即《小芯片接 口总线技术要求》。该标准描述了处理芯片、人工智 能芯片、网络处理器和网络交换芯片等应用场景的小 芯片接口总线技术要求,通过对链路层、适配层、物理 层进行详细定义,实现小芯片之间的互连互通。上述 标准于 2022 年 12 月发布,为 Chiplet 的芯片设计和封 装打下了基础,其在高端性能封装中的应用尚未有报道。

4 高端性能封装的电连接结构与工艺

传统的通信协议可用于规定芯片封装的 I/O 设 置,其中,最常用的是 PCIe。芯片间的带宽速率每 4 年 增加 1 倍,迫使芯片需要更多的 I/O,与之相应的封装 互连结构需要逐年缩小。在高端性能封装中,芯片的 I/O 数目随着芯片技术节点的推进不断增多,与之相 应的连接结构主要为凸点、高密度布线和中介层。

4.1 高端性能封装的凸点结构

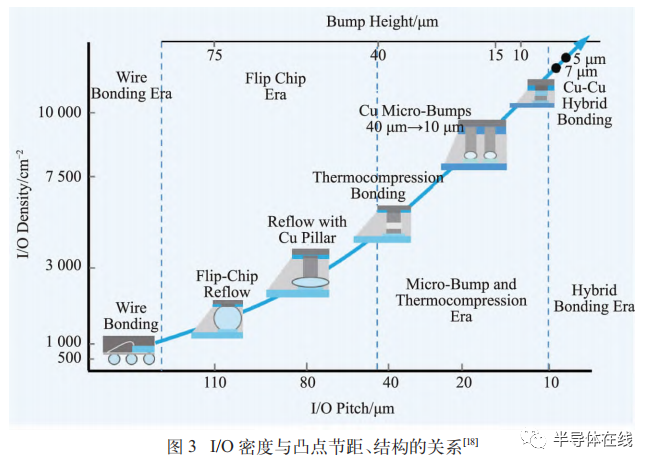

I/O 密度与凸点节距、结构的关系如图 3 所示,传 统的可控塌陷芯片连接焊球已无法满足高端性能封 装对高密度 I/O 的要求,取而代之的是节距小于 100μm 的微凸点。目前,常用的微凸点连接结构有铜-锡-铜、 镍-锡-镍、铜-锡-镍、铜-镍-锡-镍-铜和铜-铜。在 热压键合工艺中,微凸点的最小节距甚至可以缩小至 10 μm,混合键合工艺又使凸点节距小于 10 μm。除 晶圆间的混合键合外,C2C 和 C2W 混合键合技术在 近年来受到青睐。除可获得最优的电性能外,该技术 可选择已知合格芯片进行贴片,以提升整体良率,降 低制造成本。由于 C2C 和 C2W 混合技术涉及晶圆切 割,如何保护化学机械抛光后的芯片表面免受污染、 同时提升键合界面的强度问题仍需解决。已有的报道 在切割过程中采用光刻胶遮住芯片表面,再采用等离 子体进行后处理,产品的封装良率尚无法满足工业批 量生产的要求,上述问题有待更多的研究。

4.2 高端性能封装的高密度布线

在高密度布线方面,2.5D 与 3D 封装可以与前道 晶圆制造共用已成熟的制程,其线宽 / 间距在微米级 以下,达到最高的布线密度。以 FO 为基础的 2D、 2.1D、2.2D 和 2.3D 封装更接近封测企业的制程。FO 将芯片埋入模塑料中以重构晶圆,大量的模塑料不仅 不利于器件的散热,还与芯片间存在热失配的问题, 导致晶圆发生严重的翘曲,同时,包裹金属布线的高 分子介电层又加剧了上述现象,给工艺带来了较大挑战。除晶圆翘曲外,模塑料在成形过程中收缩,带动 芯片偏离设定位置,造成曝光偏移,不利于高密度布 线的制作,需要新的设备投入。作为 FO 封装的重要 连接结构,高密度布线在工艺上亦存在较高难度。特 别在多层布线的制作过程中,底层布线的拱起妨碍上 层光刻胶的曝光和刻蚀,造成布线缺陷。金属布线在 电镀后的种子层过刻蚀亦会造成其与介电层的剥离。目前,在 FO 封装结构中,4 层布线宽度 / 间距为 5 μm / 5 μm 的产品已进入量产阶段,同时,布线宽度 / 间距 的尺寸极限为 1 μm /1 μm,层数最多为 6 层,难以满 足更高 I/O 密度的芯片间连接。据报道,有学者采用 聚酰亚胺的大马士革工艺来制作亚微米布线,提升介 电层层数,上述研究尚未在量产中广泛应用。

4.3 高端性能封装的中介层

在高端性能封装中,中介层作为重要的连接结 构,可大幅提高芯片的集成度。目前,中介层按材料成 分分为有机中介层与无机中介层。其中,有机中介层 主要采用高分子材料制作高密度布线,将其置于芯片 与基板之间,作为 2.5D 硅转接板的一种廉价的替代方 案,同时降低了在基板上制造细线宽 / 窄间距布线的 难度,如 Samsung 开发出的制板级封装转接板和TSMC 基于 FO 的集成基板。

无机中介层包括硅桥、硅转接板和玻璃转接板。在高带宽存储芯片和处理芯片间,存在局部的高密度 连接。Intel 根据上述结构特点,开发出硅桥结构,将其 埋入基板,仅连接高密度 I/O 部分,其余的布线连接由基板完成。部分企业则将硅桥与 FO 封装相结合,开 发出新的封装结构。据日月光的报道,与布线宽度 / 间 距为 0.8 μm /0.8 μm 的 2.5D 封装相比,采用布线线宽/ 间距为 2 μm /2 μm 的嵌入硅桥的扇出型基板上芯片 封装(FOCoS-B)表现出更优的电性能。在 2.5D 封装 中,硅转接板为芯片平面互连提供了媒介。台积电 CoWoS@-S 封装路线如图 4 所示,按照 TSMC 推出的 存储芯片与逻辑芯片的组合方式,2023 年硅转接板的 平面面积将达到 2011 年转接板面积的 4 倍,如何将大 尺寸的转接板贴在基板之上而无贴片偏移和虚焊等 问题尚待解决。另外,硅作为一种半导体材料,不利 于信号的传输与完整性保持。TSMC 通过在硅转接板 上制作电容以弥补上述不足,但金属布线形成的电容 容量有限,无法满足广泛的应用需求。近年来,有学 者提出采用绝缘材料如玻璃替换硅,而在玻璃转接板 上制作多层亚微米级布线并提高集成度仍需要进一步探索。

5 高端性能封装的可靠性

在高端性能封装中,产品常常采用叠层结构,且 存在大量用于信号连接的微结构,这使得封装体具有 多材料、多界面和尺寸跨度大等特点,其在热、力和电 学方面均存在较大的挑战。

5.1 高端性能封装中的热失配问题

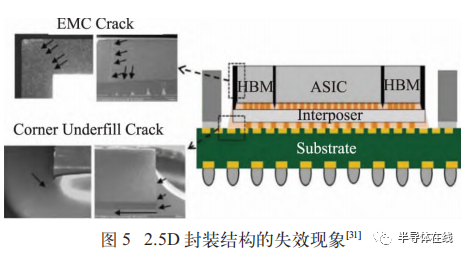

在高端性能封装中,芯片主材硅、金属和高分子 材料间的热失配问题普遍存在,由此导致封装结构在 边角处出现焊球疲劳、模塑料开裂和底填料界面分层 等现象,2.5D 封装结构的失效现象如图 5 所示。在 上述问题中,FO 封装在降低焊球热疲劳方面具有优势,大量的模塑料使得结构的热膨胀系数增大至接近 基板的水平,两者在热胀冷缩过程中保持协调变形, 焊球的应力降低,使得结构在可靠性测试时表现良好。同时,模塑料的比重小,降低了焊球在振动与跌 落过程中的惯性,有助于封装结构在上述测试时保持 完整。相比于 FO 封装,2.5D 和 3D 封装的叠层结构自 身比重大,不仅不利于散热,而且其与基板间协调变 形的难度增加了,不断增大的 2.5D 硅转接板尺寸加剧 了该现象。此外,采用模塑料对 FO、2.5D 和 3D 封装产 品进行外保护,硅芯片与模塑料间会由于热失配导致 模塑料开裂,事先使用有限元工具对模塑料的材料进 行选择是一种合适的解决方案。

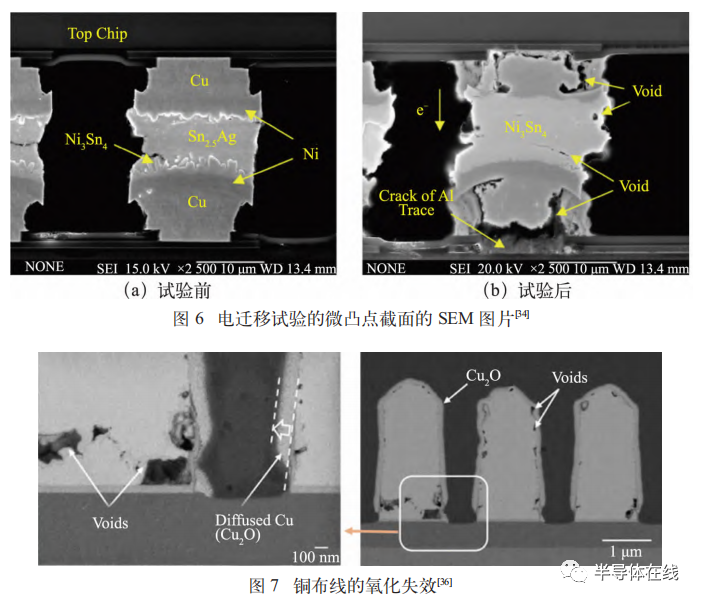

5.2 微结构的热电迁移

随着封装尺寸的不断缩小,微凸点和高密度布线 作为高端性能封装的重要电连接结构,其热电迁移问 题日益突出。在高性能产品的 2.5D 和 3D 封装中,微 凸点的直径(10~20 μm)比传统的焊球缩小一个数量 级。在 0.05 A 的小电流条件下,通过结构横截面的电 流密度约为 104A/cm2,接近锡层电迁移发生的阈值。此外,在产品服役过程中,结构中的锡、银将完全转化 为金属间化合物,造成体积收缩和柯肯达尔孔洞,加 速结构的失效,电迁移试验的微凸点截面的 SEM 图 片如图6 所示。

与微凸点的热电迁移相似,处理芯片与高带宽存 储芯片间的高密度布线亦存在上述问题,且处理芯片 工作时温度高达 100 ℃,其与存储芯片间的温度梯度 加速了上述现象的发生。在 FO 封装中,金属铜布线被 包裹在高分子钝化层中,使得其表面发生氧化、生成 氧化铜,铜布线的氧化失效如图 7 所示。在铜氧化的 过程中,铜不断向表面迁移,使得铜与氧化铜界面处 存在大量孔洞。在高温和大电流的作用下,上述氧化 现象更加明显,形成的大量孔洞严重影响布线强度与信号传输。一些研究采用非有机材料在铜表面形成保护层,将铜与高分子材料隔离,防止其氧化,由此导致 的新工艺增加了额外的制造成本。

5.3 封装体的散热问题

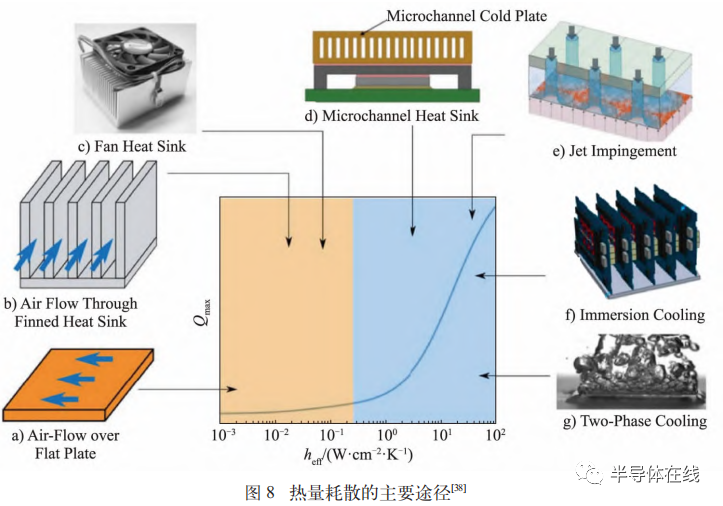

为追求最优的计算性能,处理芯片的技术节点不 断向前推进,集成的晶体管数量激增,与此同时,封装 的集成度进一步提高,要求封装体能够为处理芯片提 供热流密度高达 1 000 W/cm2的热量耗散能力。在高 端性能封装中,UHD FO、2.5D 和 3D 封装最终与基板贴合 , 一 般的组装 方 式 为 倒 装 芯 片 球 栅 阵 列 (FCBGA)。该封装的主要散热途径为背部热沉,一些 学者通过优化其设计,采用水冷、气液 2 相、风冷等方 式进行散热,优化结构的最大热耗散功率(Qmax)与有 效传热系数(heff)间的关系,以满足不同产品的应用需 求,热量耗散的主要途径如图 8 所示。

在 FCBGA 结构中,影响散热的另一重要因素为 热界面材料的选择。相比于传统的硅质材料,低熔点的金属材料更受到青睐,如铟、铟-银、锡和液态金属, 上述材料具有较大的导热系数,能够及时传递处理芯片工作时的热量。然而,基板焊球的回流焊会使这 些低熔点的材料再熔化,由此导致的孔洞与外溢问题 尚待有效解决。为进一步满足散热的需求,更加优质 的热界面材料有待开发,如石墨。除上述热沉和热界 面材料的选择外,有研究者也通过优化逻辑芯片与存 储芯片的叠层方式、FCBGA 的空腔大小等方式获得部分热性能的改进。

6 结束语

高性能计算、人工智能、云计算、数据中心和 5G 通信等领域的快速发展推动芯片技术向高性能、高带 宽的方向发展,由此导致单颗 SoC 的技术节点不断向 前推进,集成功能愈发复杂,制造成本不断攀升。一些 厂商将 SoC 的存储单元与处理单元分离出来,再经由 UHD FO、2.5D 和 3D 封装方式进行重新组合,以实现最优的计算性能。高端性能封装能够较好地满足处理 芯片日益增长的 I/O 密度、散热能力等的要求,有望得 到更多的关注和研究。

编辑:黄飞

电子发烧友App

电子发烧友App

评论