摘要:射频前端模块是无线通信的核心,滤波器作为射频前端的关键器件,可将带外干扰和噪声滤除以保留特定频段内的信号,满足射频系统的通讯要求。本文总结了声表面波滤波器工作原理及其传统封装技术,提出了一种圆片级互连封装技术,采用曝光显影、电镀及印刷等工艺实现了芯片焊盘上铜金属层和焊球的形成,避免了芯片核心功能区IDT的损伤。对封装前后电性及上基板可靠性测试,结果表明该封装方案满足声表面波滤波器封装需要。本技术在声表面波滤波器封装方面有广阔的应用前景,适用于批量生产。

引言

手机终端通信模块主要由天线、射频前端模块、射频收发模块、基带信号处理等组成。射频前端模块介于天线和射频收发模块之间,是智能移动互连领域的重要组成部分。射频前端器件主要包含:滤波器(Filter)、低噪声放大器(Low Noise Amplifier,LNA)、功率放大器(Power Amplifier,PA)、射频开关(RF Switch)、天线调谐开关(RF Antenna Switch)、双工器(Duplexer)等。射频滤波器由电容、电感、电阻等元件组成,并将特定频率外的信号滤除,保留特定频段内的信号。目前,手机常用滤波器产品主要包含:声表面波滤波器(Surface Acoustic Wave Filter,SAW Filter)、固贴式薄膜体声波滤波器(SMR Bulk Acoustic Wave Filter)、薄膜腔体谐振滤波器(FilmBulk Acoustic Resonator,FBAR)、滤波器模组,如DiFEM(分集接收模组,集成射频开关和滤波器)、LFEM(集成射频开关、滤波器及低噪声放大器)等。

目前,射频滤波器是射频前端领域中占比最高的产品。伴随频段数的增多,滤波器价值在3G终端中占比33%提升到全网通LTE终端的57%。而到5G时代,滤波器应用量将进一步提升,并已经超越PA成为整个射频前端模块市场中最重要的组成部分。

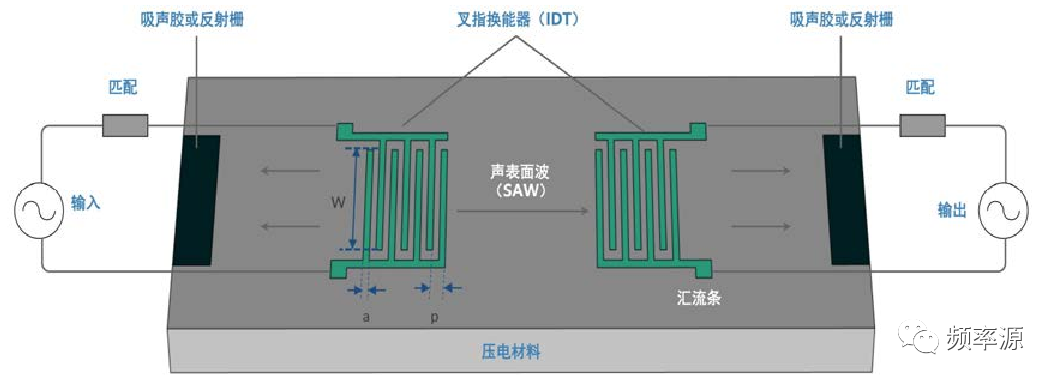

射频滤波器可分为SAW和BAW滤波器两种。SAW滤波器是一种沿着固体表面传播声波,它是由压电材料和叉指换能器(Interdigital transducer,IDT)组成。IDT作为SAW滤波器的核心功能区,其主要作用在于能量转换,即在输入端将电信号转换成声波信号,在输出端将接收的声波信号转变成电信号输出。两种信号之间的转换依赖压电材料,其特性是受到外界压力时会发生变形,使晶体内部原子间的距离发生变化,打破了原来正负电荷平衡,使晶体表面产生电压。当晶体两端受到电压时,晶体也会产生形变。SAW滤波器常用压电材料有钽酸锂(LiTaO3)、铌酸锂(LiNaO3)、石英(SiO2)等。

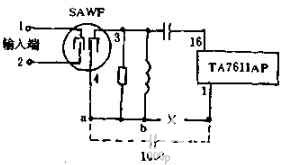

目前,SAW filter主要封装形式是金属封装、陶瓷封装,倒装焊封装和圆片级三维封装。倒装焊技术的引入,摒弃了传统点焊技术,降低了封装体总厚度,同时也使得整个封装过程从表面贴装器件(Surface Mounted Devices,SMD)进入芯片尺寸级封装(Chip Scale Package,CSP),主要封装流程是:在划片前先对器件焊盘上进行铜金属层和焊球的制作,然后划片倒装焊接到PCB基板或陶瓷基板上,并将树脂膜以热压方式压合到基板上,此时器件表面已形成包裹封装,最后划片将器件分离形成最终产品。凸块是定向生长于芯片表面,与芯片焊盘直接相连或间接相连的具有金属导电特性的凸起物,由金凸块(Gold Bump)、焊球凸块(Solder Bump)和铜柱凸块(Pillar Bump)组成。金凸块由底部金属层(Under Bump Metallization,UBM)以及电镀金组成,加工价格昂贵,用于液晶屏驱动芯片或玻璃基板的电互连;铜柱凸块由电镀铜柱和焊球组成,可完全替代焊球凸块在倒装封装中使用,且铜具有良好的电、热学性能,可弥补焊球凸块在电学和热学性能上的问题。本文即在SAW滤波器焊盘上制备铜金属层及焊球,并在整个封装过程中保证IDT不受污染和腐蚀,同时在选用基板材料时,需保证基板材料的热膨胀系数与LiTaO3接近,避免因热膨胀系数差别过大而导致热失配情况,降低失效率。

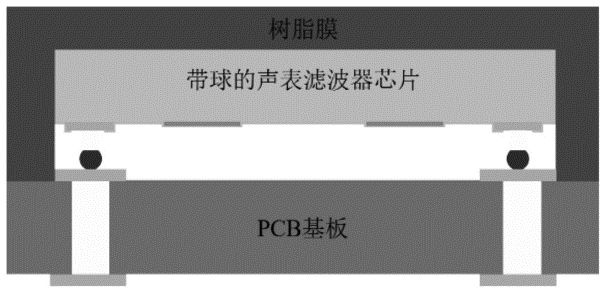

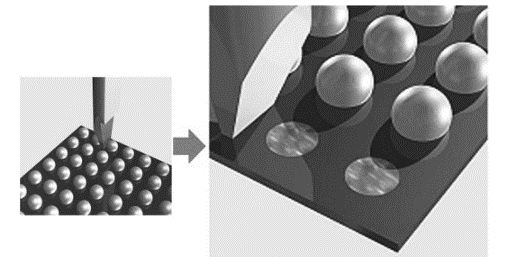

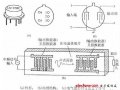

图1所示为SAW滤波器封装的整体结构图。基于CSP封装技术的SAW滤波器主要由以下几部分组成:(1)树脂膜,主要成分是环氧树脂,可将芯片包裹密封,起到保护作用;(2)带球的SAW滤波器芯片,由铜金属层及焊球组成。而本文中将详细介绍铜金属层及焊球的形成过程,且保证形成过程中未对IDT造成损伤,实现封装前后电性与可靠性测试;(3)基板,在整个封装结构中起到物理支撑作用和电路连接作用。

图1 倒装焊接工艺的SAW滤波器标准结构

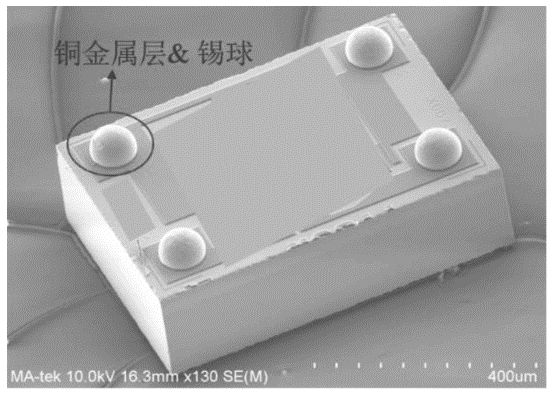

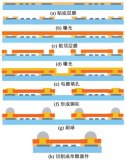

本文针对芯片焊盘上铜金属层及焊球的形成过程,提出了一种圆片级互连封装技术,首先使用一种光刻胶水,经曝光显影、种子层Ti/Cu沉积、电镀、去胶、刻蚀及印刷完成了SAW滤波器焊盘上铜金属层的制作,如图 2 所示。并实际测试了封装前后滤波器的频率变化在0.5 MHz以内,可认为该封装方案对滤波器的性能不受影响。

图2 圆片级互连封装中铜金属层和焊球

1 圆片级互连封装互连工艺步骤

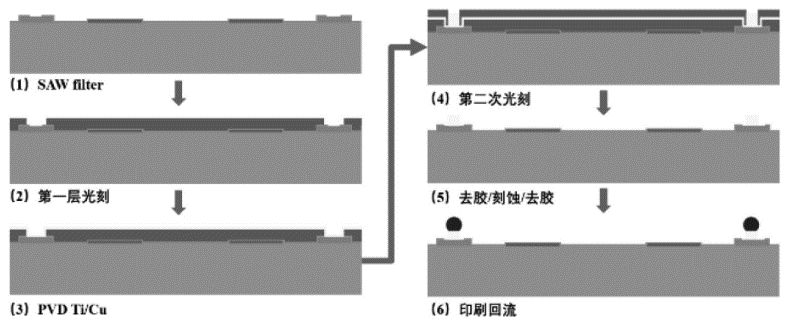

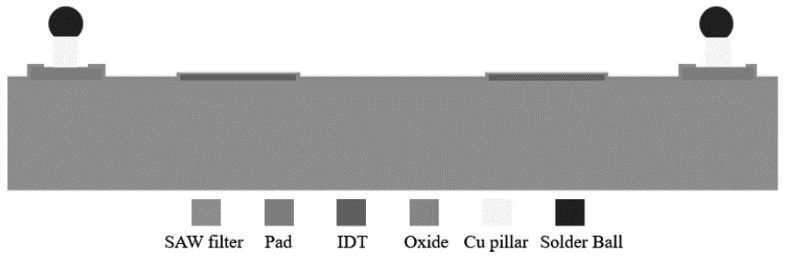

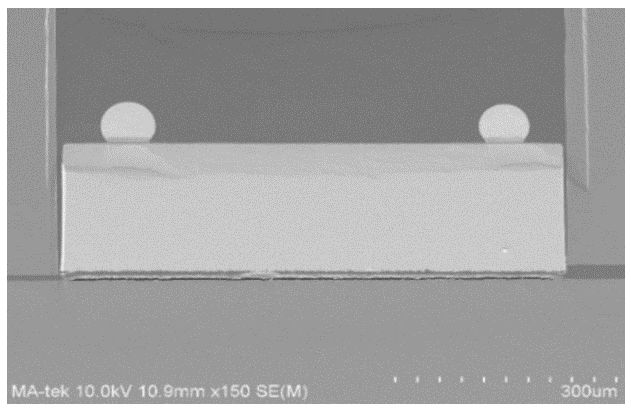

本技术采用一种圆片级互连封装路线,如图3所示,其简要封装工艺流程为:圆片来料清洗→第一层光刻→种子层Ti/Cu沉积→第二层光刻→电镀→去胶/刻蚀/去胶→印刷回流形成焊球。图4为单颗SAW滤波器封装截面图。

图3 圆片级互连封装技术流程图

图4 SAW滤波器圆片级互连封装截面图

1.1 来料圆片前处理过程

圆片级互连封装技术是对整个圆片进行加工,有利于对所有芯片进行一次性封装,可批量生产。同时,来料圆片在不同加工厂加工及运输,表面可能会附着较大颗粒物,需彻底清洗。颗粒物的存在会影响后续工艺及滤波器性能。因此,来料圆片先使用单片清洗机,配合高压氮气水枪,可有效地将圆片表面附着颗粒清除干净,最后置于无氧烤箱120℃烘烤60min以彻底去除水汽,同时避免了芯片表面金属线路不被氧化。

1.2 焊球底部金属铜层形成过程

在SAW滤波器焊盘上制作铜金属层,需保证芯片IDT不被污染。从成本和精度综合考虑,封装详细流程如图3(2)-(5)所示,主要细分为以下四个小步:

第一层光刻,所使用的光刻胶须保证不伤害芯片IDT。首先,通过旋涂约为6 μm的光刻胶,配合热板150℃下烤5 min。旋涂时,需保证胶水在圆片上的均匀性,整体厚度变化量不超过1 μm,并加以烘烤的目的是去除光刻胶中大部分溶剂,稳定光刻胶曝光特性。随后进行的曝光、显影等工艺,在芯片焊盘上露出电镀开口区。其中,光刻参数是关键的,如果曝光参数设置不合理,焊盘底部会存在光刻的显影残留,导致电镀金属不连续。

溅射种子层,在溅射种子层之前,圆片先经过等离子体清洗以彻底去除焊盘表面有机物颗粒,并在第一层光刻上产生一定粗糙度为种子层的良好附着创造有利条件。在PVD设备中,圆片需要先在高温下脱气(Degas),然后在氧、氩等离子环境中进一步轰击以去除表层有机物、氧化物等杂质,最后再分别溅射一层厚度为100 nm和300 nm的钛层和铜层。

第二层光刻,使用第一层相同光刻胶,主要作用是光刻露出电镀区,且光刻胶厚度应大于后续所需铜金属层的厚度值,并保证焊盘开口处不存在光刻胶的显影残留,如图5所示。

图5 第二层光刻后焊盘无显影不洁

电镀工序,即在种子层露出区域制作铜金属层。金属层厚度取决于圆片上受镀面积、电镀时间和电流大小等。在电镀过程中,圆片浸泡在含有铜离子的药水中并接通电源阴极,药水的另一端放置磷铜阳极。通电后,圆片表面开始析出一层铜金属薄膜。电镀药水含有五水硫酸铜及其他添加剂,如使电流密度较大区域镀层平滑的光亮剂,有利于降低表面张力的润湿剂。

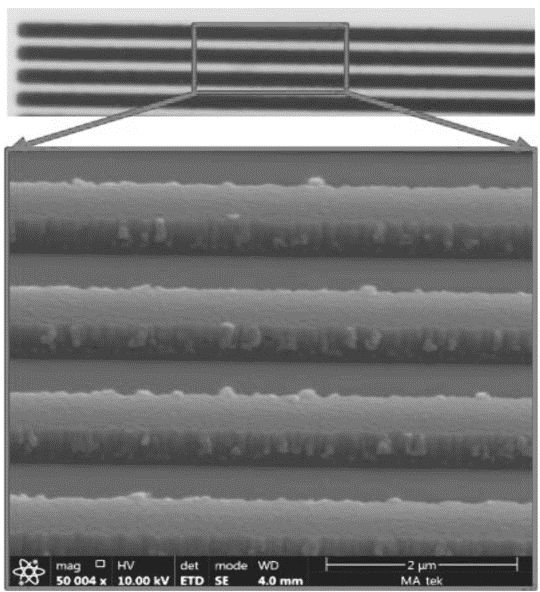

去胶/刻蚀/去胶:完成电镀工序后,需在圆片表面去除掉多余的光刻胶及铜层、钛层。去第二层光刻胶时,需保证该层光刻胶被完全剥离干净,否则在后续刻蚀种子层时存在光刻胶未去除干净影响刻蚀效果。去除最后一层光刻胶后,芯片功能区IDT裸露,需观察芯片IDT是否损伤,如图6所示,IDT上金属线条均未被腐蚀,表明铜金属层制作过程满足SAW滤波器封装要求。

图6 SEM下IDT金属线条未被腐蚀

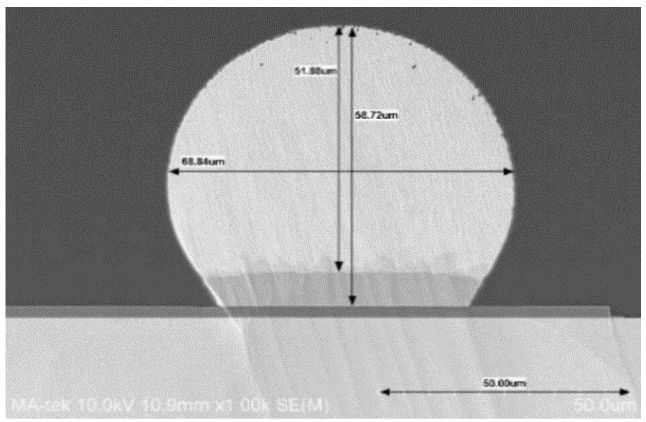

1.3 焊球形成过程

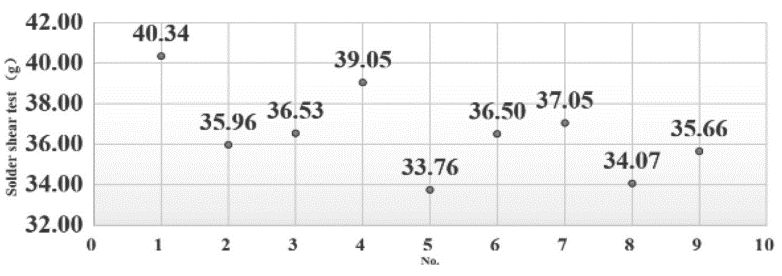

涂覆锡膏、回流工艺,锡膏通过印刷方式涂覆在铜金属层上,并经回流炉短暂高温形成焊球。锡膏中混有助焊剂,主要起到润湿、降低表面张力以及去除氧化层的作用,并在回流炉中挥发散去。根据锡膏的融化温度范围,回流过程中的最高温度是250℃,经回流后焊球形貌如图7、8所示,焊球未出现空洞,在圆片不同方位上随机选取 9 颗焊球,通过光学显微镜分别测量了焊球的直径和高度,结果表明焊球高度在60±10μm范围内,直径在75±10 μm范围内,均满足后续芯片倒扣在基板上的封装要求。针对焊球与焊盘的结合力,还需进行剪切力测试,测试原理如图9所示,剪切探头距离铜凸点30 μm,剪切速度10 μm/s,剪切探头上抬高度14 μm,在圆片的不同方向上随机选取9颗焊球,推力测试结果分布如图10所示,结果表明全部焊球推力都超过30g,焊球与焊盘结合力符合封装要求。

图7 SEM下SAW滤波器圆片级互连封装截面图

图8 SEM下焊球截面图

图9 剪切力测试示意图

图10 焊球剪切力测试分布图

2 SAW滤波器性能性测试

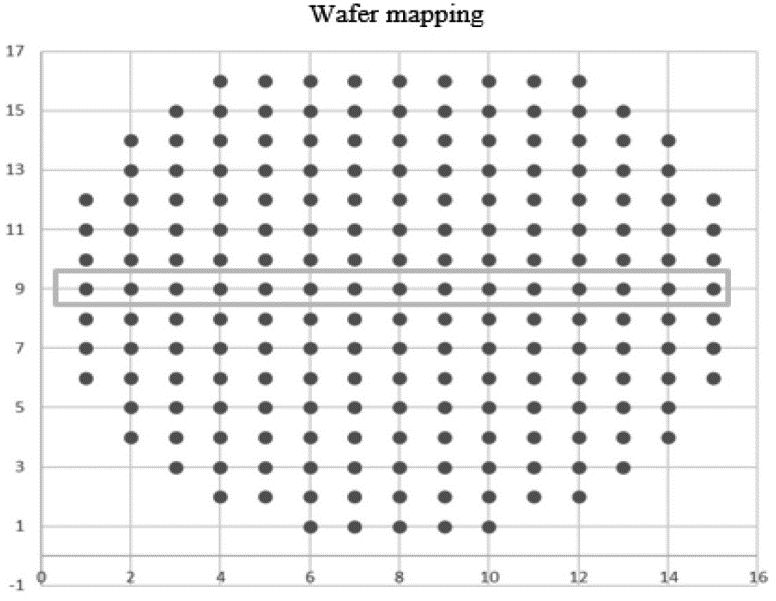

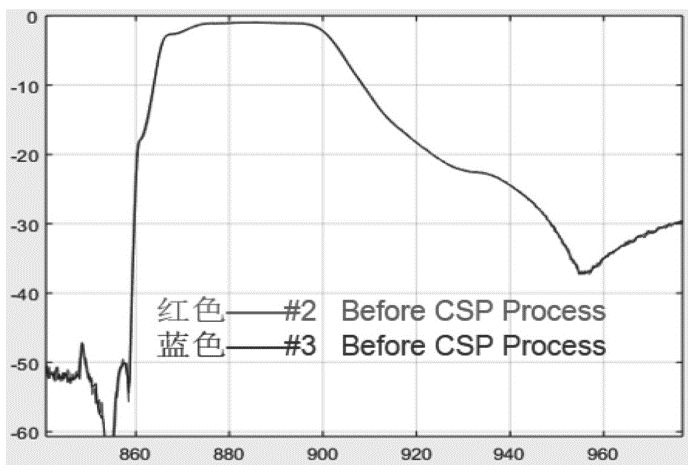

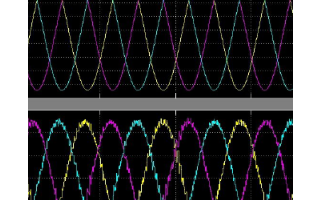

将植球后的芯片上基板可靠性试验前,需对封装后谐振器频率进行电性测试,对比封装前后频率变化,得出封装是否会对滤波器的性能造成影响。取圆片中间谐振器芯片进行测试,如图11框中所示。测试结果表明,如图12所示,封装前后谐振器的频率变化在0.5 MHz以内,可认为该封装方案对谐振器性能无影响。

图11 选取测试数据点(框中所示)

图12 封装前后谐振器频率变化

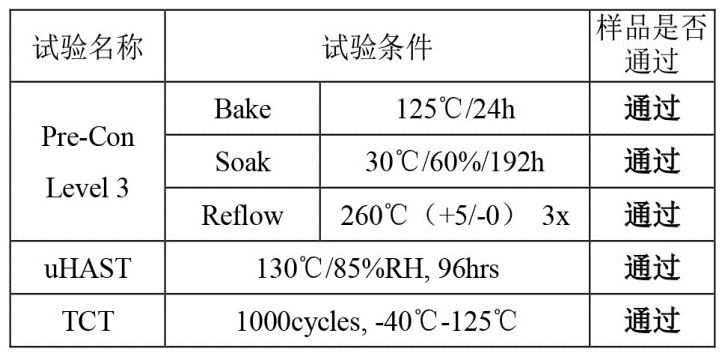

对谐振器性能测试完成后,再选取80颗标准样品(Golden Sample)上基板进行可靠性试验。在进行可靠性试验前,一般需要对样品进行预处理(Pre-Condition,Pre-Con),其目的是模拟器件在封装后进行运输、组装和存储所受到外界温度、湿度的影响。预处理过程参照JEDEC J-STD-020D标准,将测试良好的芯片分别在125℃下烘烤24 h以彻底去除封装过程中的水分、然后分别浸入30%、60%湿气环境192 h,最后样品在高温260℃炉中回流3次。在预处理后,样品分别还进行高加速温湿度及偏压测试(ubias Highly Accelerated Stress Test,uHAST)和温度循环测试(Temperature Cycling Test,TCT)试验,如表1所示为相对应的试验项目及条件。

表1 可靠性试验条件及结果

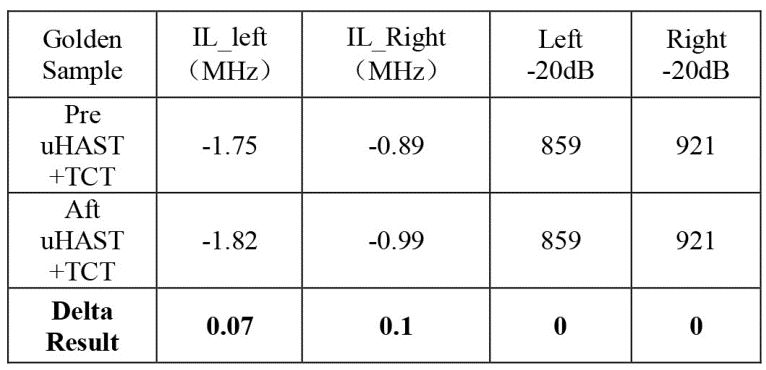

uHAST试验参数为110℃/85%RH,96h。TCT试验参数为-45℃-125℃,循环1000次。通过对比uHAST+TCT试验前后样品的测试数据差值,如果通带内IL差值均<0.1 dB,左边-20dB和右边-20dB处的频率偏移量均<1MHz,定为通过性能测试。假设将通带内IL差值变化量|X|>0.1dB,-20dB处频率偏移量>2MHz,定为失效标准。根据表2结果,测试了80颗芯片,结果均通过了可靠性测试。

表2 可靠性试验结果表征

3 结论

本文提出了一种SAW滤波器圆片级互连封装技术,完成了SAW滤波器芯片焊盘上铜金属层和焊球的制作。主要结论如下:

(1)结合SAW滤波器的封装工艺,成功制备了尺寸为712 μm × 512 μm × 270 μm的CSP形式的SAW滤波器样品,封装面积与芯片面积相当,占比近1:1,有利于集成化应用。

(2)该圆片级互连封装工艺过程未对IDT造成损伤,不影响SAW的传播及滤波器的性能;

(3)通过对SAW滤波器封装前后电性及上基板可靠性测试,验证了CSP封装方案满足SAW滤波器的封装需求。

审核编辑:刘清

电子发烧友App

电子发烧友App

评论