上个月,IFS(Intel Foundry Services)和Arm达成协议,计划优化Arm的IP,以适应Intel即将推出的18A工艺(1.8nm)。这次合作将主要关注移动领域的设计,并将进行DTCO(design technology co-optimization)和STCO(system technology co-optimization),这意味着Arm的IP将为Intel即将推出的工艺节点和该公司的先进封装技术进行优化。

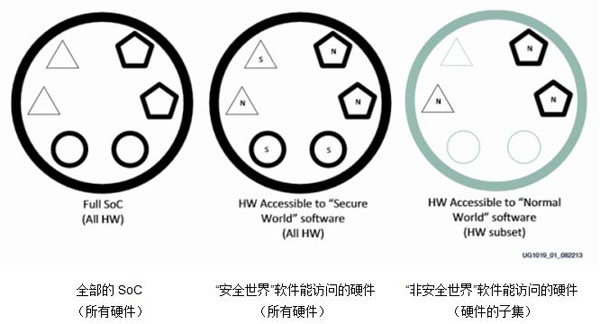

IFS和Arm将共同优化Arm的IP,使用DTCO方式为Intel的18A工艺优化性能、功耗和成本。这次合作的关键成果之一将是开发一个“基于Arm的移动SoC、芯片技术演示,以及芯片设计参考平台”,这是一个相当广泛的定义。 与此同时,Intel和Arm确认工作已经开始。 Intel的一位发言人表示,“这项工作将验证Arm SoC设计在Intel 18A工艺中的性能、功耗和面积利用率。” Arm的一位发言人解释道,“我们正在构建定制IP,以确保基于Arm的SoC设计的最佳功耗、性能和面积。通过这次公告,我们为我们的IP客户提供了基于Arm的SoC设计的另一个可选项。”

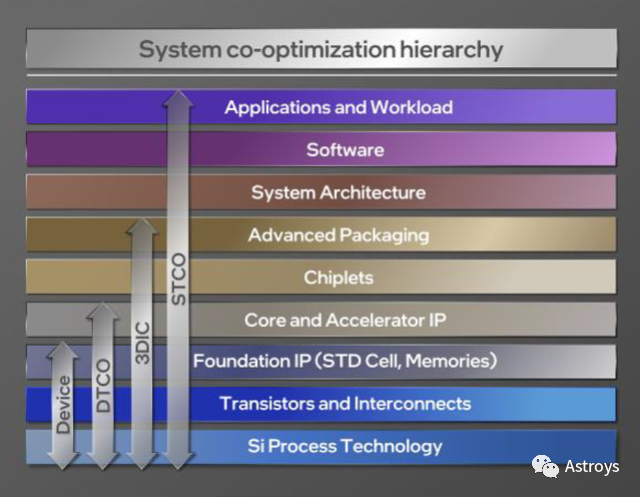

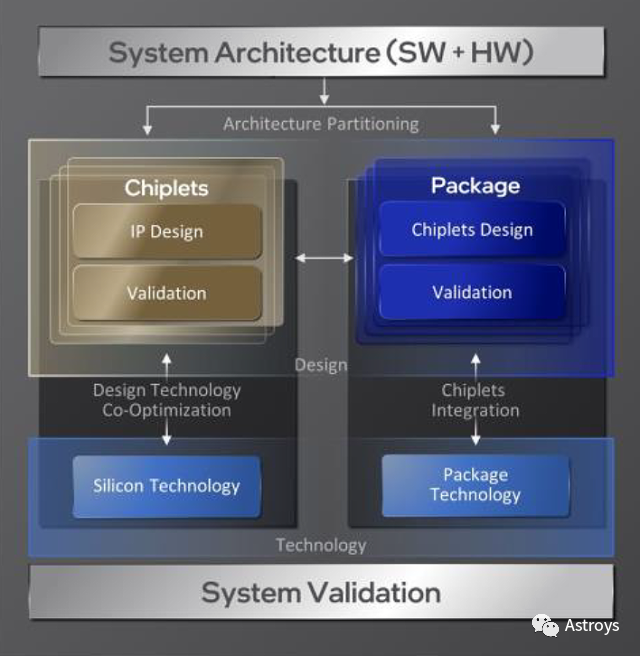

STCO的层次结构。设备优化、DTCO、3DIC和STCO之间的差异。

寻找新客户

虽然最初几代合作将主要关注移动SoC项目和部分Arm IP(例如,Cortex-A CPU IP,Mali GPU IP等),但两家公司表示,合作范围可能会扩展到汽车、航空航天、数据中心(例如,Neoverse)、IoT和政府应用。虽然“政府应用”是一个相当模糊的词,但要记住,Intel的18A已经被美国国防部选中,所以或许对于Arm的授权公司来说,用优化的Arm IP来满足美军的需求会稍微容易一些。 与此同时,IFS-Arm公告重要性的普遍性不容低估,因为它确保IFS将能够生产基于优化的Arm IP的SoC,就像竞争对手TSMC和Samsung代工厂一样。 另一方面,Arm需要确保其内核可以通过尽可能多的芯片公司在尽可能多的工艺制程上生产。 More Than Moore的首席分析师Ian Cutress说:“Arm需要确保其内核在尽可能多的工艺节点上得到验证,但对于Intel来说,这给他们提供了一个面向许多Arm生态系统玩家的卖点。

TSMC在这方面做得就非常好。Intel需要可以可以按数量级增长的客户群,而对于Arm来说,这只是‘另一步’。” Real World Tech的总裁兼MLPerf的联席主席David Kanter说:“IFS希望尽可能多地拥有IP,以便客户能够构建产品。在IFS上可用的IP越多,获客的阻力就越小。” Tirias Research的首席分析师Jim McGregor表示:“这有助于将IFS与行业的需求对齐,而这个焦点是性能与能效。而且这样会让代工市场更加充分竞争。” 目前,合作的范围仅限于移动SoC,可能多少有些困惑,因为Intel近年来在数据中心以及大芯片上都投入了较多关注。但这对Arm和IFS来说都是非常有意义的,因为智能手机SoC是Arm最大的收入来源之一,也是IFS的一个好机会。 Cutress说:“现在,因为Softbank和IPO,Arm正在限制它正在进行的项目,所以它正在挑选和选择最有利的机会。移动SoC是一个好的目标,因为IFS实际上只有高性能节点可以提供,且基板尺寸小(~100-150mm2),相比大的,700mm2的数据中心芯片对产量提升更有利。汽车领域的芯片并不总是需要领先的节点,所以移动SoC是很好的选择。如果我们看TSMC,其收入的34%来自智能手机,44%来自HPC,所以IFS-Arm追求移动IP的验证是有意义的。”

不仅仅是移动领域

Intel认为其18A工艺在性能、功耗和晶体管密度方面将具有无可争议的领先优势。该公司最初计划其18A工艺将是第一个使用ASML的High-NA Twinscan EXE EUV扫描器的技术,预计在2025年的某个时候达到0.55的数值孔径,但最终,该公司透露,在2024年下半年,它可以使用现有的0.33-NA EUV工具进行双模曝光,而不是使用下一代设备。同时,为了降低EUV双模曝光与优化20A和18A的成本,该公司将采用Applied Materials的Centura Sculpta塑形工具。

如果Intel能够用其18A制程提供最高的性能效率和晶体管密度,并且能提供良好的财务条件,fabless将倾向于使用它。此外,借助优化的标准Arm IP,这种工艺对SoC开发人员来说会非常有吸引力。 Kanter指出,“支持Arm核的目标是,这些内核被广泛用于各种产品,并成为许多SoC的‘标准构建模块’”。

虽然这次公告内容非常笼统,但这次合作承诺为Arm的授权者提供很多可能性,包括已经宣布计划使用Intel 18A制程的Qualcomm,但未透露是为了哪类的产品。MTK是另一家注册使用IFS产能的主要移动SoC供应商,但它尚未对Intel的1.8nm节点表现出兴趣。分析师表示,IFS-Arm公告的其他不太明显的受益者可能还有其他公司。

Cutress表示:“Qualcomm已经表达了兴趣,但是在一家公司开始付款并投资设计团队之前,我还是持怀疑态度。MTK已经表达了兴趣,但迄今为止,其它移动SoC供应商的兴趣还不大。其他几个主要的玩家,Apple在Intel成为领导者之前不可能;Samsung,可能有点奇怪,但不是不可能;Unisoc,可能是解决中美贸易难题的一种方式。” Qualcomm已经在其Snapdragon SoC中使用了定制的基于Arm的大核,未来几年,该公司计划在一系列产品中采用高度定制的Nuvia开发的Arm微架构。因此,它不太可能对标准的高性能Arm Cortex感兴趣,但它仍然可以利用为Intel的18A优化的Arm技术。 Kanter说:“以Qualcomm为代表,许多移动SoC都喜欢在手机或服务器中使用较小的内核。在移动领域中,MTK倾向于在他们的产品线中使用标准的Arm核。” Tirias Research的McGregor说:“Qualcomm是显而易见的受益者,但Apple也可能从中受益。MTK与Intel在modem领域有合作,也可能从中受益。Google可能从中受益。其他考虑自制芯片的手机OEM也可能从中受益。”

实际上,有很多非移动应用(从汽车到数据中心的各种应用)都可以从优化为Intel 18A节点的标准Arm核中受益。 Cutress说:“那里也有很多你可能没有想到的像移动SoC一样的ASIC:IPMI芯片、ACAPs Xilinx/硬化的FPGA,控制器等。对汽车信息娱乐芯片的要求并不那么高。” Kanter说:“Arm IP在汽车信息娱乐中可能很有用。只需看看GM对安卓的采用情况。Android在Arm上运行得最好。” McGregor说:“移动细分市场只是冰山一角。CE和嵌入式市场的Arm组件更多。” 实际上,他说,IFS和Arm的合作可能会迅速扩展到更具挑战性的数据中心应用。 McGregor补充说:“他们可以很快地扩展它。你必须记住,Intel已经采用Arm授权很多年了。Intel熟悉这种架构。唯一的限制是需求。如果机会出现,我相信我们会看到这些产品在Intel运行,尽管他们会与其他Intel产品竞争。”

DTCO遇见GAA和背面PDN

谈到晶圆厂,DTCO方法已经存在一段时间,所以IFS绝对不是首个引入DTCO的。实际上,大部分Intel自家的CPU内核都是针对特定生产节点构建的,这是在频率和功耗方面展现出DTCO优势的良好示例,尽管是在IDM中,所以Intel对此方法一点也不陌生。

Intel的18A制程将是公司第二个(继20A之后)采用GAA晶体管的节点,Intel称其为RibbonFET,以及采用PDN(power delivery network),被Intel命名为PowerVia。Intel的20A和18A是两种既为Intel自身也为IFS客户开发的制程。此外,两者都为DTCO提供了丰富的选项。

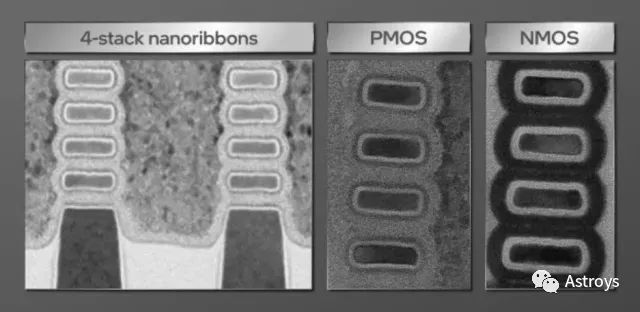

Intel的RibbonFET GAA晶体管架构堆叠了四个纳米带,以实现与多个鳍片相同的驱动电流,但占用的空间较小。(来源:Intel)

与平面晶体管和FinFET相比,GAAFET提供了几个关键优势,如显著减小的漏电流,因为栅极环绕着通道的四个侧面。

此外,在GAA晶体管中,可以改变特定工艺或甚至特定芯片设计中纳米片的宽度,从而进行性能(宽度增加)、能耗(宽度减小)和芯片面积的微调。

对于移动SoC设计,GAA晶体管的漏电流减少是无可争议的好处。为移动设计进一步定制晶体管架构可能会在功耗和性能方面带来额外的好处。与此同时,调整标准单元,开发为移动定制的库并在Intel的18A上实现Arm IP,应该能在晶体管级别进一步优化性能、功耗、面积和成本。但IFS和Arm尚未确认与晶体管设计优化相关的任何具体细节。

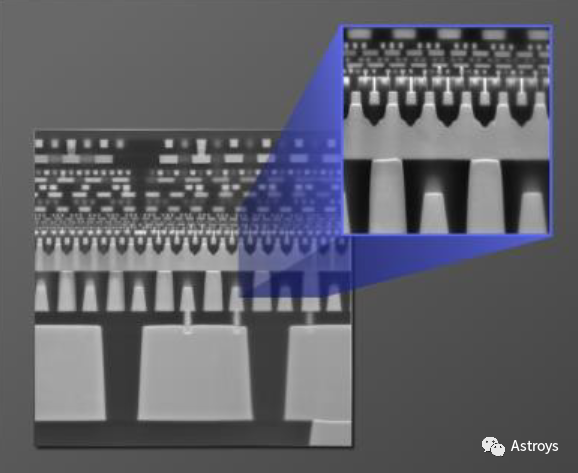

由于接触电阻增加和IR下降,导致能量损失、性能降低和高温,向更薄的节点供电已经成为一种挑战。背面PDN(PowerVia)将电源线从数据I/O线路移开,简化了连接性并使PDN更加成熟。

Intel的背面PDN,PowerVia,它将电源线和信号线分开并缩小标准单元的大小。电源线放在晶体管层下方,位于晶片的背面。(来源:Intel)

Intel的发言人说:“总的来说,通过消除对晶圆正面进行电源布线的需求,我们可以腾出更多的资源来优化信号布线并减少延迟。这使我们可以根据产品需求,优化性能、功耗或面积。”

供电通常会因芯片设计的不同而有所差异。

例如,用户端和数据中心处理器的CPU都是为满足不同的性能要求而定制的,因此,它们需要不同的PDN。服务器处理器能够稳定地处理重型工作负载,并在需求达到峰值时可以短暂提高其时钟速度。

另一方面,用户端CPU通常被优化以应对突发行为,因为它们通常保持处于非活动状态或工作负载较低。但当启动资源密集型工作负载时,这些处理器需要快速(在微秒内)从非活动状态提升到最大速度,有时甚至超过最大速度,以确保用户体验的顺畅。智能手机SoC设计针对更快速地响应需求,因此它们需要自己的PDN设计。

与Intel可能针对更广泛应用而设计的标准PowerVia PDN相比,针对智能手机SoC的Arm IP优化PowerVia PDN可能会带来许多性能和功耗方面的优势。当然,IFS和Arm并未确认计划在当前的合作中为标准移动Arm IP定制RibbonFET和PowerVia。

Kanter解释说:“我预计Intel的GAA性能会超过其他代工厂的选项,部分原因在于采用了PowerVia(以及晶体管实施的差异)。因此,这可能会转化为更好的频率或者在相似频率下更低的功耗。Intel的PowerVia是20A和18A的一部分,因此我预计优化Arm IP的Intel工艺中会包括PowerVia。根据我看到的分析,PowerVia似乎很可能通过更好的供电提供小幅度的性能提升(比如说,3%到7%)和相当可观的面积减小(15%到20%)。”

Cutress附和说:“尽管IFS和Arm之间的合作将为计划采用Arm的移动IP的客户带来许多好处,但IFS愿意与每一个足够大的客户密切合作以提高PPA。”

他补充说:“在Arm中没有特定的东西意味着Intel的GAA会有好处;晶体管和架构是独立的。我认为IFS会尽其所能给予其主要客户额外的好处,特别是如果是大玩家(Apple、Qualcomm),不论是芯片还是架构。”

McGregor说他没有看到Arm相比其他架构有任何特定的好处:“半导体/晶体管设计的进步将对整个行业有益。”

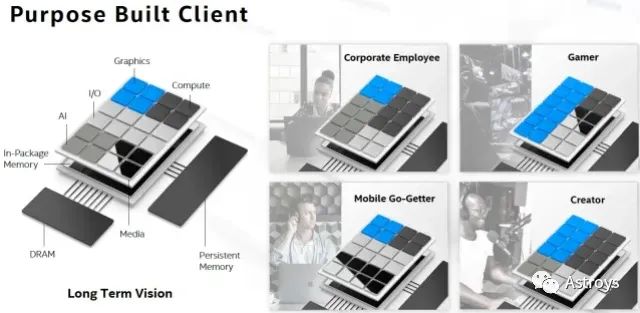

一个multi-daie用户端应用系统封装的例子(来源:Intel)

IFS和Arm在言论中提到的另一个细节是意图优化目标平台“从应用和软件,到封装和芯片”,基本上意味着STCO。尽管Intel承认EMIB(2.5D)和Foveros(3D)封装技术都在考虑范围内,但公司还没有准备分享任何其他细节。

Intel说:“合作会考虑到2.5D和3D封装技术。”

移动领域的SoC一直都是高度集成的,引入解耦设计将标志着行业的里程碑。尽管目前尚未明确Intel和Arm在这里打算做什么,因为声明的框架目前仅限于Intel的18A节点,而解耦设计则暗示了使用几个节点来优化成本。此外,分析师们指出,现在先进封装的成本非常高。

Cutress表示,过去两年,Qualcomm在IEEE会议上介绍了关于芯片策略和封装的主题,并补充说,“如果不是在智能手机上,那么在笔记本上肯定会发生。主要的争议点是成本,芯片封装仍然非常昂贵。”

Kanter表示,移动设备中的先进封装将取决于成本:“现在,大多数先进的封装技术实施起来相对昂贵。看看3D堆叠的成本增量。一旦好处变得更大,或者我们能够通过更成熟的工艺降低成本,这可能会促成更先进的封装。”

McGregor表示,解耦的移动SoC设计不会在近期内,“你必须记住,移动设备有尺寸、功率和成本的限制。因此,拥有单一芯片仍然有优势。至少在先进封装成本下降或多芯片的经济效益变化之前不会。”

实际上,Arm也表示,虽然移动SoC的解耦是可能的,但必须非常谨慎地评估。“有许多因素在起作用。移动领域的成本结构需要评估,重要的是,RTL需要进行优化,以确保可以充分利用解耦和封装技术。”

但Kanter表示,STCO可能不仅限于封装,还涉及从热管理到生产工艺的所有内容。

他说:“我认为STCO包含的内容不仅仅是封装。其中一部分是将热管理、供电和封装集成到整体制造工艺中。”

计算系统的系统技术共同优化(来源:英特尔)

广泛的地理布局

Intel预计IFS会拥有的一个优势是,它将在美国和欧洲都有18A的生产能力,这将使IFS的客户将供应链多样化。

因为目前的合作仅限于Arm的移动IP,而领先的移动SoC开发商位于美国(Apple,Qualcomm)、台湾(MTK)和中国(Unisoc),考虑到实际设备仍将在中国、印度或东南亚国家组装,所以还不清楚他们是否认为在美国或欧洲生产他们的SoC很重要。

然而,Kanter和McGregor表示,考虑到目前的地缘政治紧张局势,多元化的供应链本身可能是一个优势,所以在美国和欧洲制造18A节点的芯片是IFS将拥有的无可争议的王牌。

McGregor说:“在美国和欧洲都有生产能力是一个优势,特别是对军事/政府应用而言。”

编辑:黄飞

电子发烧友App

电子发烧友App

评论