电子发烧友网报道(文/吴子鹏)后摩尔定律时代,如何在不依赖价格昂贵的先进制程的情况下显著提升芯片的性能,成为行业共同关注的话题。此时,封装在整个产业中的战略地位凸显出来,从传统的倒装和晶圆级封装

2022-08-05 08:19:00 6763

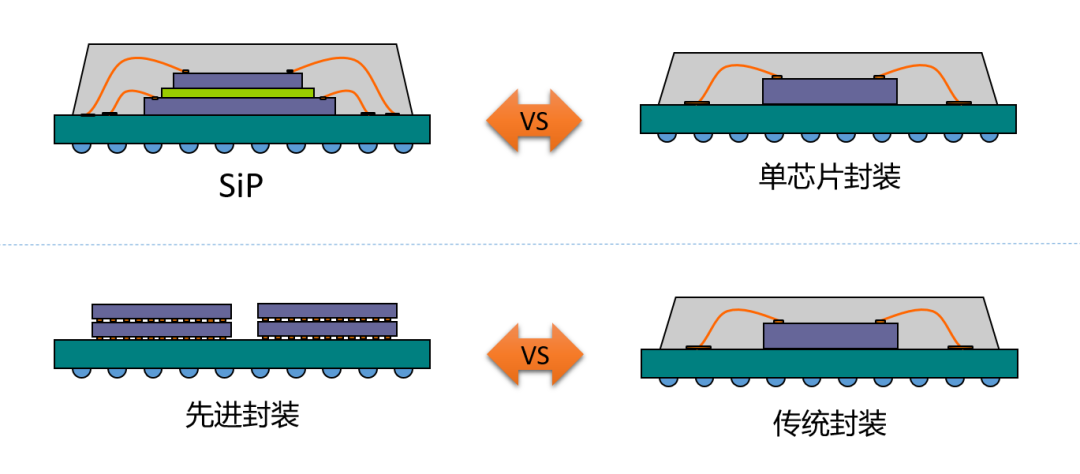

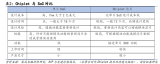

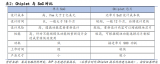

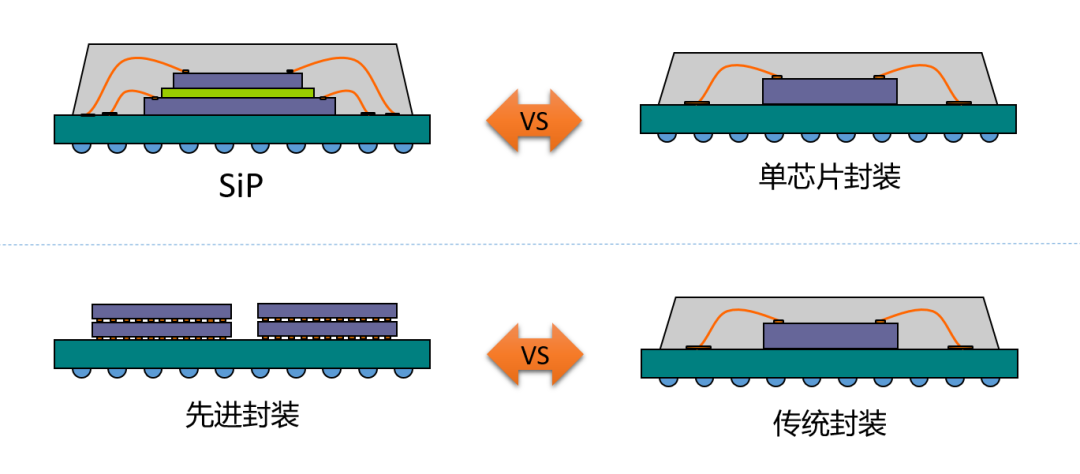

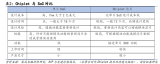

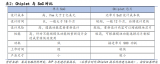

6763 SiP的关注点在于:系统在封装内的实现,所以系统是其重点关注的对象,和SiP系统级封装对应的为单芯片封装;先进封装的关注点在于:封装技术和工艺的先进性,所以先进性的是其重点关注的对象,和先进封装对应的是传统封装。

2021-03-15 10:31:53 8490

8490

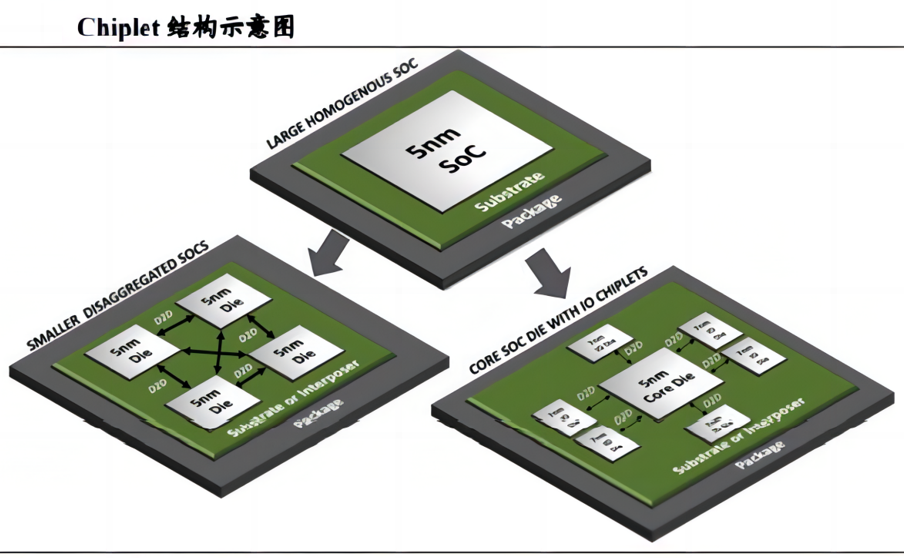

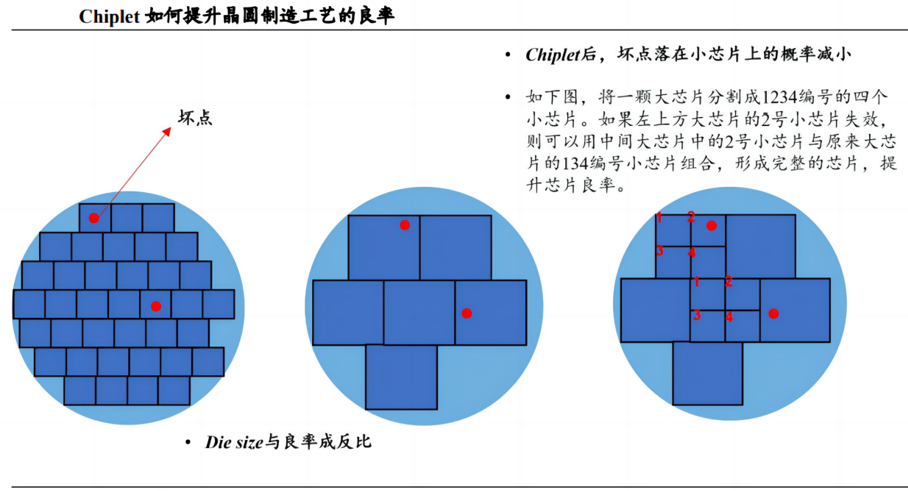

Chiplet可以使用更可靠和更便宜的技术制造。较小的硅片本身也不太容易产生制造缺陷。此外,Chiplet芯片也不需要采用同样的工艺,不同工艺制造的Chiplet可以通过先进封装技术集成在一起。

2022-10-06 06:25:00 18480

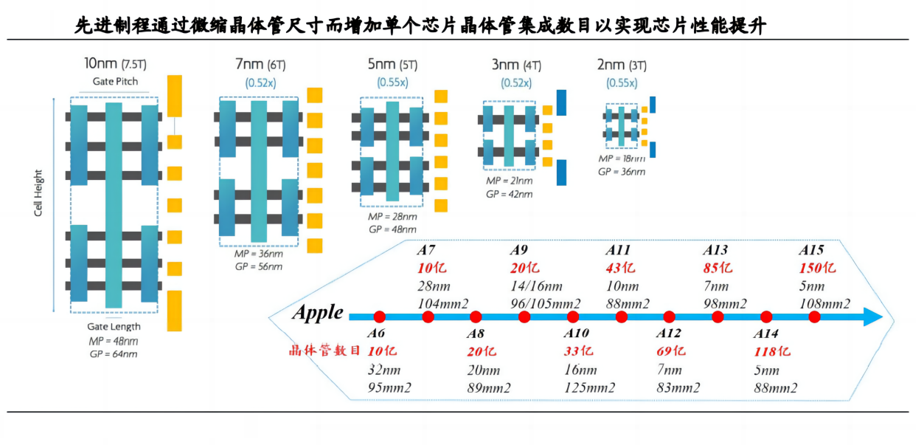

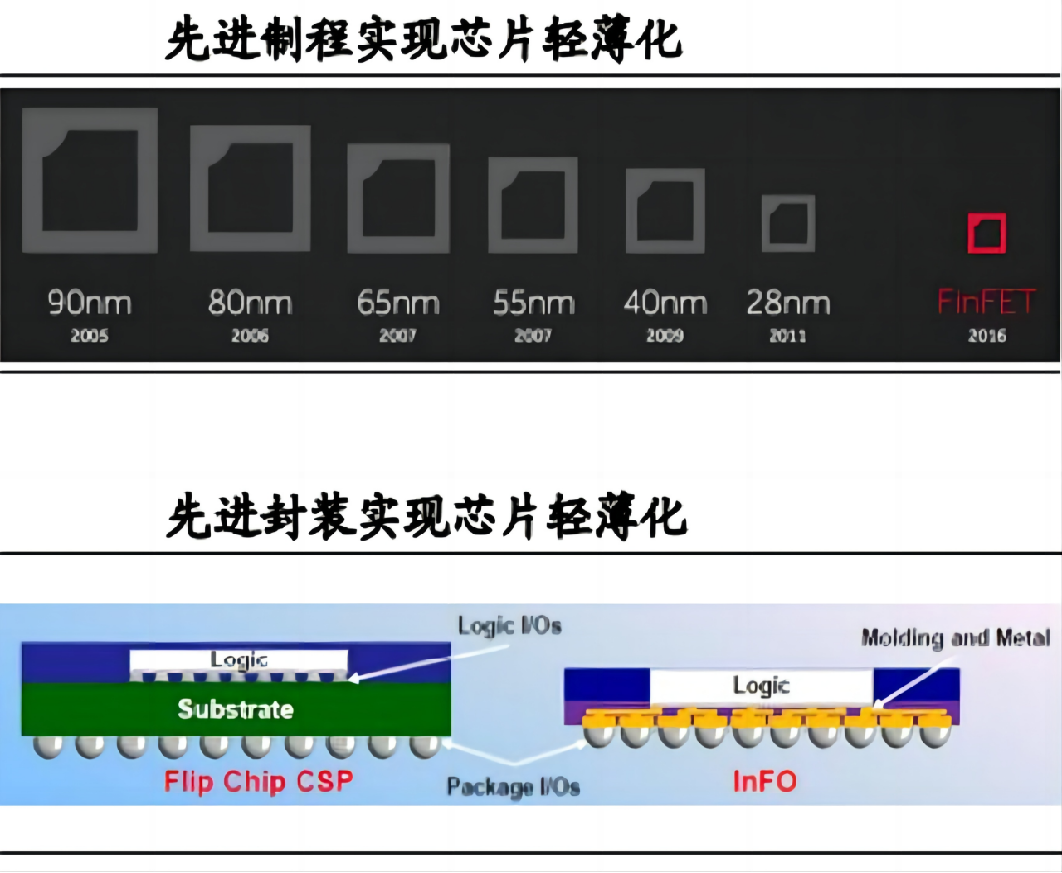

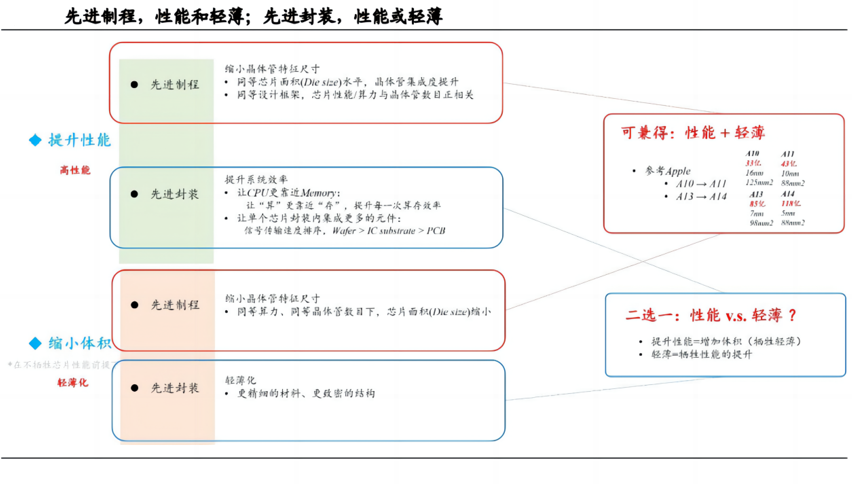

18480 芯片升级的两个永恒主题:性能、体积/面积。芯片技术的发展,推动着芯片朝着高性能和轻薄化两个方向提升。而先进制程和先进封装的进步,均能够使得芯片向着高性能和轻薄化前进。

2023-02-14 10:43:02 1538

1538

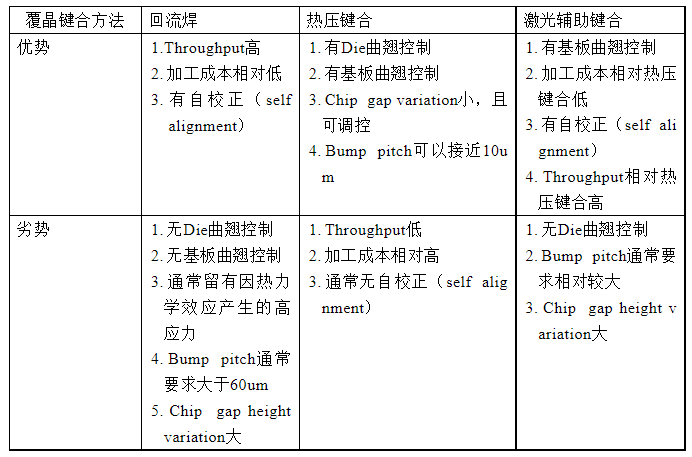

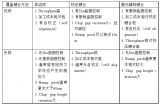

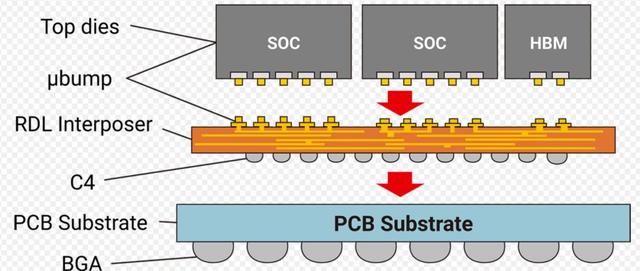

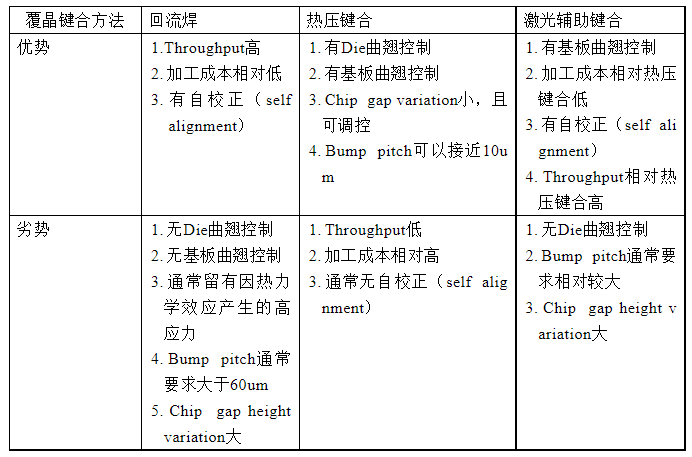

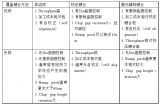

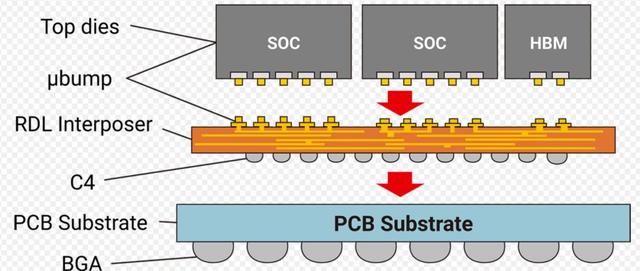

(858mm2)以及制程的缩小也变得非常艰难且性价比遇到挑战, 多芯片封装技术来到了舞台的中心成为进一步提升芯片性能的关键。 覆晶键合技术已然成为先进多芯片封装最重要的技术之一。

2023-04-19 09:42:52 1011

1011

(858mm2)以及制程的缩小也变得非常艰难且性价比遇到挑战, 多芯片封装技术来到了舞台的中心成为进一步提升芯片性能的关键。覆晶键合技术已然成为先进多芯片封装最重要的技术之一。

2023-05-11 10:24:38 615

615

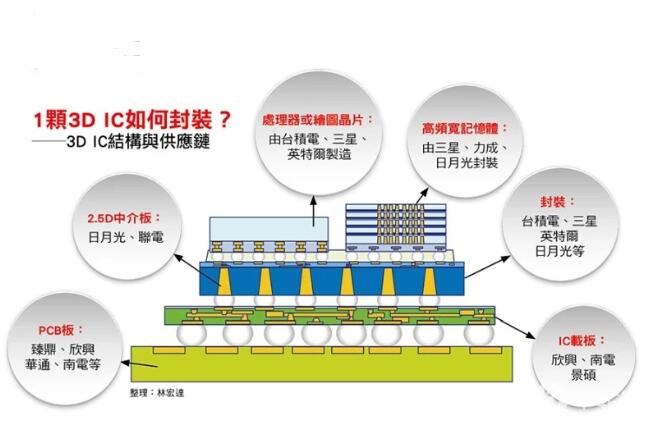

随着电子产品趋向于功能化、轻型化、小型化、低功耗和异质集成,以系统级封装(System in Package, siP)、圆片级封装( Wafer Level Package.WLP)、2.5D/3D 封装等为代表的先进封装技术越来越多地应用到电子产品中。

2023-05-11 14:39:38 451

451 先进封装是“超越摩尔”(More than Moore)时代的一大技术亮点。当芯片在每个工艺节点上的微缩越来越困难、也越来越昂贵之际,工程师们将多个芯片放入先进的封装中,就不必再费力缩小芯片了。本文将对先进封装技术中最常见的10个术语进行简单介绍。

2023-07-12 10:48:03 625

625

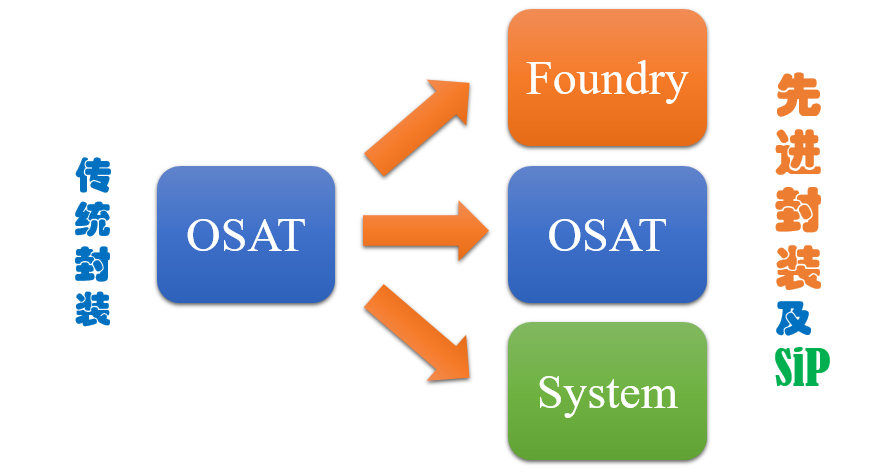

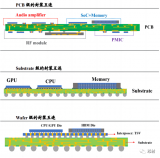

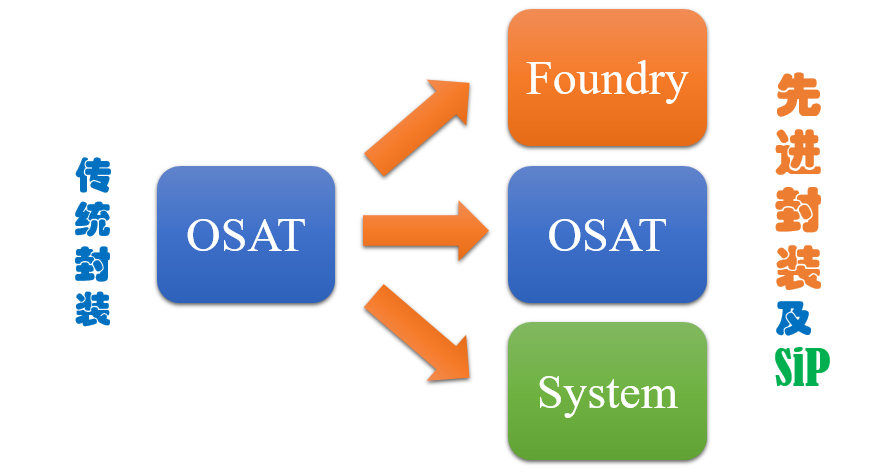

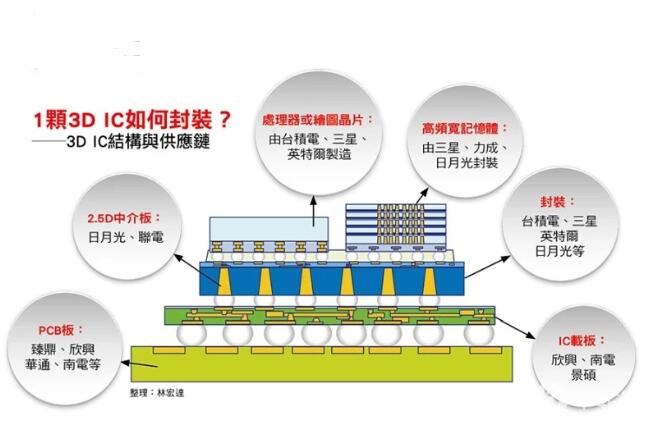

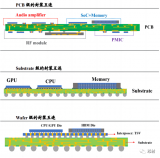

先进封装处于晶圆制造与封测的交叉区域 先进封装处于晶圆制造与封测制程中的交叉区域,涉及IDM、晶圆代工、封测厂商。先进封装要求在晶圆划片前融入封装工艺步骤,具体包括应用晶圆研磨薄化、重布线(RDL

2023-08-07 10:59:46 852

852

半导体器件有许多封装形式,按封装的外形、尺寸、结构分类可分为引脚插入型、表面贴装型和高级封装三类。从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进。总体说来

2023-08-28 09:37:11 1072

1072

Chiplet也称芯粒,通俗来说Chiplet模式是在摩尔定律趋缓下的半导体工艺发展方向之一,是将不同功能芯片裸片的拼搭

2023-09-28 11:43:07 653

653

随着晶圆级封装技术的不断提升,众多芯片设计及封测公司开始思考并尝试采用晶圆级封装技术替代传统封装。其中HRP(Heat Re-distribution Packaging)晶圆级先进封装

2023-11-30 09:23:24 1124

1124

说起传统封装,大家都会想到日月光ASE,安靠Amkor,长电JCET,华天HT,通富微电TF等这些封装大厂OSAT;说起先进封装,当今业界风头最盛的却是台积电TSMC,英特尔Intel,三星SAMSUNG等这些顶尖的半导体晶圆厂IC Foundry,这是为何呢?

2023-12-21 09:32:02 474

474

半导体器件有许多封装形式,按封装的外形、尺寸、结构分类可分为引脚插入型、表面贴装型和高级封装三类。从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进。总体说来,半导体

2024-01-16 09:54:34 606

606

最近,在先进封装领域又出现了一个新的名词“3.5D封装”,以前听惯了2.5D和3D封装,3.5D封装又有什么新的特点呢?还是仅仅是一个吸引关注度的噱头?

2024-01-23 16:13:29 496

496

摘 要:先进封装技术不断发展变化以适应各种半导体新工艺和材料的要求和挑战。在半导体封装外部形式变迁的基础上,着重阐述了半导体后端工序的关键一封装内部连接方式的发展趋势。分析了半导体前端制造工艺的发展

2018-11-23 17:03:35

。如比较小的阻抗值、较强的抗干扰能力、较小的信号失真等等。芯片的封装技术经历了好几代的变迁,从DIP、QFP、PGA、BGA到CSP再到MCM。技术指标和电器性能一代比一代先进。

2011-10-28 10:51:06

有人又将其称为圆片级-芯片尺寸封装(WLP-CSP),以晶圆圆片为加工对象,在晶圆上封装芯片。晶圆封装中最关键的工艺为晶圆键合,即是通过化学或物理的方法将两片晶圆结合在一起,以达到密封效果。如下

2021-02-23 16:35:18

先进封装发展背景晶圆级三维封装技术发展

2020-12-28 07:15:50

MPU6050有软件解算姿态和DMP解算姿态,他们各自的优缺点是什么呢?因为大家都知道的是DMP可以减轻MCU的负担,但我看了好几个微型四轴开源飞控的选择都是用软件解算,什么理由呢?

2019-05-29 04:36:05

的特性可通过改变其化学成分和工艺的控制调整来实现,不仅可作为封装的封盖材料,它也是各种微电子产品重要的承载基板;陶瓷封装的缺点:1)与塑料封装相比较,它的工艺温度较高,成本较高;2)工艺自动化与薄型化封装

2019-12-11 15:06:19

8~12 英寸先进封装技术专用匀胶设备沈阳芯源微电子设备有限公司沈阳芯源微电子设备有限公司研制的8~12 英寸先进封装技术专用匀胶设备获得“2007年中国半导体创新产

2009-12-14 10:42:38 8

8 论文综述了自 1990 年以来迅速发展的先进封装技术,包括球栅阵列封装(BGA)、芯片尺寸封装(CSP)、圆片级封装(WLP)、三维封装(3D)和系统封装(SiP)等项新技术;同时,叙述了我国封

2009-12-14 11:14:49 28

28 Siemens 业务部门 Mentor 今天宣布推出业内最全面和高效的针对先进 IC 封装设计的解决方案 — Xpedition 高密度先进封装 (HDAP) 流程。

2017-06-27 14:52:20 1777

1777 SiP和Chiplet也是长电科技重点发展的技术。“目前我们重点发展几种类型的先进封装技术。首先就是系统级封装(SiP),随着5G的部署加快,这类封装技术的应用范围将越来越广泛。其次是应用于

2020-09-17 17:43:20 9167

9167 什么是COB封装? COB的优缺点是啥子? 什么是绑定IC? Altiumdesigner 里面 如何绘制? 官方解答:COB封装即chip On board,就是将裸芯片用导电或非导电胶粘附在互连

2020-09-29 11:15:00 11051

11051 (Waferlevelpackage),2.5D封装(interposer,RDL等),3D封装(TSV)等先进封装技术。 ▌ SoC vs.SiP ►SoC:全称System-on-chip,系统级芯片

2020-10-21 11:03:11 28156

28156

今日,长电科技中国区研发中心副总经理李宗怿在中国集成电路设计业2020年会--封装与测试分论坛上发表了主题为《先进封装的协同设计与集成开发》的演讲。

2020-12-11 15:24:38 3063

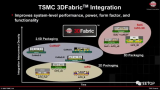

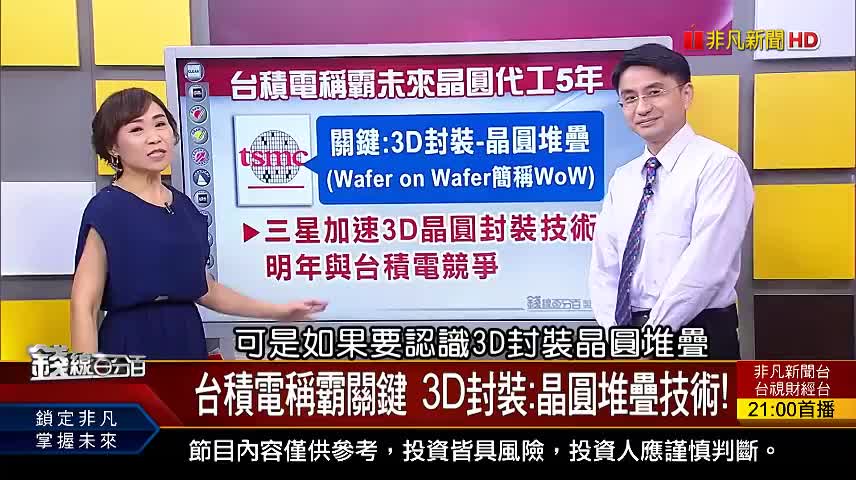

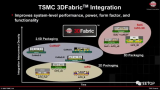

3063 台积电和三星于先进封装的战火再起。2020年,三星推出3D封装技术品牌X-Cube,宣称在7纳米芯片可直接堆上SRAM内存,企图在先进封装拉近与台积电的距离。几天之后,台积电总裁魏哲家现身,宣布推出自有先进封装品牌3D Fabric,台积电最新的SoIC(系统集成芯片)备受瞩目。

2021-01-04 10:37:09 1269

1269

据彭博社今日下午报道,继赴美建设5nm晶圆代工厂后,全球晶圆代工龙头台积电正计划赴日本建设先进封装厂。如果消息属实,这将是台积电首座位于海外的封测厂。

2021-01-06 12:06:16 1804

1804 作为华天集团晶圆级先进封装基地,华天昆山2008年6月落户昆山开发区,研发的晶圆级传感器封装技术、扇出型封装技术、超薄超小型晶圆级封装、晶圆级无源器件制造技术目前已达到世界领先水平。

2021-01-09 10:16:09 4166

4166 近日,蒋尚义在回归中芯国际之后首次公开亮相,出席了第二届中国芯创年会,并发表演讲。 据科创板日报报道,蒋尚义此次演讲提出了多个观点,如摩尔定律的进展已接近物理极限;后摩尔时代的发展趋势是研发先进封装

2021-01-19 10:25:02 2859

2859 先进封装大部分是利用「晶圆厂」的技术,直接在晶圆上进行,由于这种技术更适合晶圆厂来做,因此台积电大部分的先进封装都是自己做的。

2021-02-22 11:45:21 2200

2200

一项技术能从相对狭窄的专业领域变得广为人知,有历史的原因,也离不开著名公司的推波助澜,把SiP带给大众的是苹果(Apple),而先进封装能引起公众广泛关注则是因为台积电(TSMC)。 苹果

2021-04-01 16:07:24 32556

32556

最近,先进封装技术在台湾地区掀起了新一波热潮,焦点企业是AMD和台积电。 AMD宣布携手台积电,开发出了3D chiplet技术,并且将于今年年底量产相应芯片。AMD总裁兼CEO苏姿丰表示,该封装

2021-06-18 11:17:26 1999

1999 最近,关于台积电的先进封装有很多讨论,让我们透过他们的财报和最新的技术峰会来对这家晶圆代工巨头的封装进行深入的介绍。 资料显示,在张忠谋于2011年重返公司之后,就下定决定要做先进封装。而1994

2021-06-18 16:11:50 3699

3699 在之前举办的Computex上,AMD发布了其实验性的产品,即基于3D Chiplet技术的3D V-Cache。该技术使用台积电的3D Fabric先进封装技术,成功地将包含有64MB L3

2021-06-21 17:56:57 3244

3244 先进封装技术FC/WLCSP的应用与发展分析。

2022-05-06 15:19:12 24

24 端

子引出互连等 3 种先进互连技术及其封装工艺的优缺点,讨论了功率电子模块封装及互连技术所面临的问题与挑战。

2022-05-06 15:15:55 6

6 2021年对于先进封装行业来说是丰收一年,现在包括5G、汽车信息娱乐/ADAS、人工智能、数据中心和可穿戴应用在内的大趋势继续迫使芯片向先进封装发展。2021年先进封装市场总收入为321亿美元,预计

2022-06-13 14:01:24 2047

2047 通富微电、华天科技也表示已储备Chiplet相关技术。Chiplet是先进封装技术之一,除此以外,先进封装概念股也受到市场关注。4连板大港股份表示已储备TSV、micro-bumping(微凸点)和RDL等先进封装核心技术。

2022-08-08 12:01:23 1048

1048 因此,该行业已转向使用chiplet来组合更大的封装,以继续满足计算需求。将芯片分解成许多chiplet并超过标线限制(光刻工具的图案化限制的物理限制)将实现持续缩放,但这种范例仍然存在问题。即使

2022-08-24 09:46:33 1935

1935 墙”和“功能墙”)制约,以芯粒(Chiplet)异质集成为核心的先进封装技术,将成为集成电路发展的关键路径和突破口。文章概述近年来国际上具有“里程碑”意义的先进封装技术,阐述中国大陆先进封装领域发展的现状与优势,分析中国大陆先进封装关键技术与世界先进水平的差距,最后对未来中国大陆先进封装发展提出建议。

2022-12-28 14:16:29 3295

3295 Chiplet 封装领域,目前呈现出百花齐放的局面。Chiplet 的核心是实现芯片间的高速互 联,同时兼顾多芯片互联后的重新布线。

2023-01-05 10:15:28 955

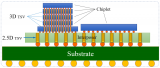

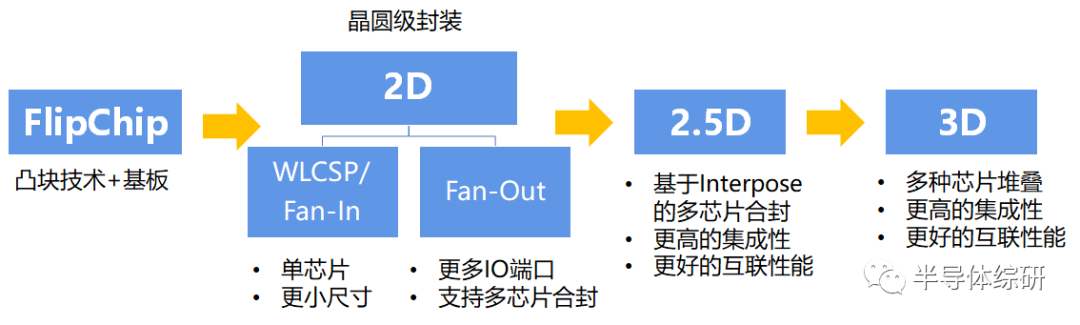

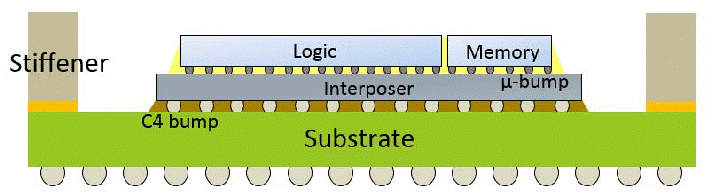

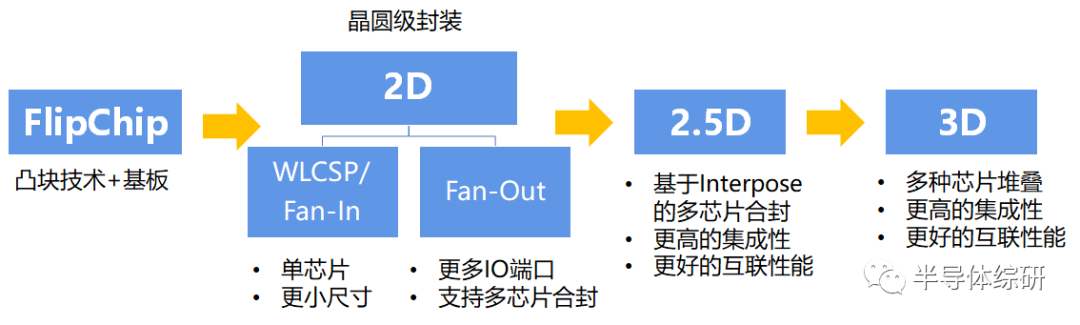

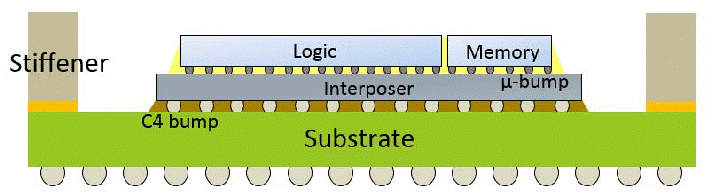

955 采用了先进的设计思路和先进的集成工艺、缩短引线互连长度,对芯片进行系统级封装的重构,并且能有效提高系统功能密度的封装。现阶段的先进封装是指:倒装焊(FlipChip)、晶圆级封装(WLP)、2.5D封装(Interposer、RDL)、3D封装(TSV)

2023-01-13 10:58:41 1220

1220 随着集成电路制程工艺逼近物理尺寸极限,2.5D/3D封装,芯粒(Chiplet)、晶上系统(SoW)等先进封装成为了提高芯片集成度的新方向,并推动EDA方法学创新。这也使得芯片设计不再是单芯片的问题,而逐渐演变成多芯片系统工程。

2023-01-29 09:31:01 595

595 Promex Industries 首席执行官 Dick Otte对先进封装中材料特性的未知数、对键合的影响,以及为什么环境因素在复杂的异质封装中如此重要等问题进行回答。以下是本次谈话的节选。

2023-01-29 11:00:40 380

380 SiP是一个非常宽泛的概念,广义上看,它囊括了几乎所有多芯片封装技术,但就最先进SiP封装技术而言,主要包括 2.5D/3D Fan-out(扇出)、Embedded、2.5D/3D Integration,以及异构Chiplet封装技术。

2023-03-20 09:51:54 1037

1037

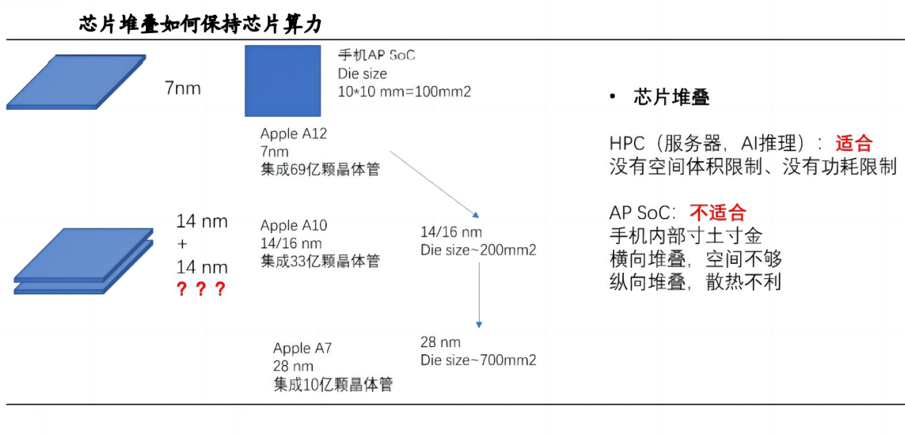

难以在全球化的先进制程中分一杯羹,手机、HPC等需要先进制程的芯片供应受到严重阻碍,亟需另辟蹊径。而先进封装/Chiplet等技术,能够一定程度弥补先进制程的缺失,用面积和堆叠换取算力和性能。

2023-04-15 09:48:56 1953

1953 来源:Cadence楷登 2023年4月26日,楷登电子近日宣布基于台积电 3nm(N3E)工艺技术的 Cadence® 16G UCIe™ 2.5D 先进封装 IP 成功流片。该 IP 采用

2023-04-27 16:35:40 452

452

Chiplet即小芯片之意,指在晶圆端将原本一颗“大”芯片(Die)拆解成几个“小”芯片(Die),因单个拆解后的“小”芯片在功能上是不完整的,需通过封装,重新将各个“小”芯片组合起来,功能上还原

2023-05-15 11:41:29 1457

1457

SiP系统级封装(System in Package),先进封装HDAP(High Density Advanced Package),两者都是当今芯片封装技术的热点,受到整个半导体产业链的高度关注

2023-05-19 09:54:26 1326

1326

台积电对外传内部要扩充CoWoS产能的传言也相当低调,以“不评论市场传闻”回应,并强调公司今年4月时于法说会中提及,关于先进封装产能的扩充(包括CoWoS)均仍在评估中,目前没有更新回应,间接证实公司短期内暂无扩产动作。

2023-06-08 14:27:11 643

643 先进封装是对应于先进圆晶制程而衍生出来的概念,一般指将不同系统集成到同一封装内以实现更高效系统效率的封装技术。

2023-06-13 11:33:24 282

282

一、核心结论 1、先进制程受限,先进封装/Chiplet提升算力,必有取舍。在技术可获得的前提下,提升芯片性能,先进制程升级是首选,先进封装则锦上添花。 2、大功耗、高算力的场景,先进封装

2023-06-13 11:38:05 747

747

随着摩尔定律的放缓以及前沿节点复杂性和成本的增加,先进封装正在成为将多个裸片集成到单个封装中的关键解决方案,并有可能结合成熟和先进的节点。

2023-06-16 17:50:09 340

340

Fab 6 是台积电首个一体式先进封装测试工厂,是台积电不断增加的封装投资的一部分。该晶圆厂已准备好量产台积电 SoIC 封装技术。请记住,当台积电说量产时,他们指的是 Apple iPhone 尺寸的量产,而不是工程样品或内部产品。

2023-06-19 11:25:56 219

219

紧密相连。在业界,先进封装技术与传统封装技术以是否焊线来区分。先进封装技术包括FCBGA、FCQFN、2.5D/3D、WLCSP、Fan-Out等非焊线形式。先进

2022-04-08 16:31:15 641

641

先进的半导体封装既不是常规操作,目前成本也是相当高的。但如果可以实现规模化,那么该行业可能会触发一场chiplet革命,使IP供应商可以销售芯片,颠覆半导体供应链。

2023-06-21 08:56:39 190

190 Chiplet俗称“芯粒”或“小芯片组”,通过将原来集成于同一 SoC 中的各个元件分拆,独立 为多个具特定功能的 Chiplet,分开制造后再通过先进封装技术将彼此互联,最终集成封装 为一个系统芯片。

2023-06-25 15:12:20 1345

1345

组合成为特定功能的大系统。那么半导体Chiplet技术分别有哪些优点和缺点呢? 一、核心结论 1. 先进制程受限,先进封装/Chiplet提升算力,必有取舍。 在技术可获得的前提下,提升芯片性能,先进制程升级是首选,先进封装则锦上添花。 2. 大功耗、高算

2023-06-25 16:35:15 1686

1686

在异质异构的世界里,chiplet是“生产关系”,是决定如何拆分及组合芯粒的方式与规则;先进封装技术是“生产力”,通过堆叠、拼接等方法实现不同芯粒的互连。先进封装技术已成为实现异质异构的重要前提。

2023-06-26 17:14:57 601

601 Chiplet 俗称“芯粒”或“小芯片组”,通过将原来集成于同一 SoC 中的各个元件分拆,独立 为多个具特定功能的 Chiplet,分开制造后再通过先进封装技术将彼此互联,最终集成封装 为一个系统芯片。

2023-07-04 10:23:22 630

630

AI订单激增,影响传至先进封装市场。

2023-07-05 18:19:37 776

776

Chiplet,就是小芯片/芯粒,是通过将原来集成于同一系统单晶片中的各个元件分拆,独立为多个具特定功能的Chiplet,分开制造后再透过先进封装技术将彼此互联,最终集成封装为一系统晶片组。

2023-07-06 11:28:23 522

522

提及先进封装,台积电的CoWoS和InFO、三星的X-Cube以及英特尔的EMIB等晶圆级封装是如今最为人所熟知的方案。在Chiplet热潮的带动下,这些晶圆级封装技术扶持着逼近极限的摩尔定律继续向前,巨大的市场机遇面前,传统的封测厂商也开始钻研晶圆级技术,意图分一杯羹。

2023-07-11 16:19:09 443

443 Chiplet技术是一种利用先进封装方法将不同工艺/功能的芯片进行异质集成的技术。这种技术设计的核心思想是先分后合,即先将单芯片中的功能块拆分出来,再通过先进封装模块将其集成为大的单芯片。

2023-07-17 09:21:50 2309

2309

根据 LexisNexis 的数据,中国台湾芯片制造商台积电开发了最广泛的先进芯片封装专利库,其次是三星电子和英特尔。

2023-08-03 17:27:17 1067

1067 level package),2.5D封装(interposer,RDL等),3D封装(TSV)等先进封装技术。

2023-08-05 09:54:29 398

398

先进封装处于晶圆制造与封测制程中的交叉区域,涉及IDM、晶圆代工、封测厂商,市场格局较为集中,前6 大厂商份额合计超过80%。全球主要的 6 家厂商,包括 2 家 IDM 厂商(英特尔、三星),一家

2023-08-11 09:11:48 456

456

半导体器件有许多封装形式,按封装的外形、尺寸、结构分类可分为引脚插入型、表面贴装型和高级封装三类。从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进。

2023-08-11 09:43:43 1796

1796

半导体器件有许多封装形式,按封装的外形、尺寸、结构分类可分为引脚插入型、表面贴装型和高级封装三类。从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进。

2023-08-14 09:59:17 1086

1086

面对人工智能相关需求的激增,台积电已无法满足先进封装服务的需求,并一直在快速扩大产能,其中包括在台湾投资近 900 亿新台币(28.1 亿美元)的新工厂。

2023-09-20 17:31:00 669

669 先进封装增速高于整体封装,将成为全球封装市场主要增量。根据Yole的数据,全球封装市场规模稳步增长,2021 年全球封装 市场规模 约达 777 亿美元。其中,先进封装全球市场规模约 350 亿美元,占比约 45%, 2025 年,先进封装在全部封装市场的 占比将增长至 49.4%。

2023-09-22 10:43:18 1189

1189

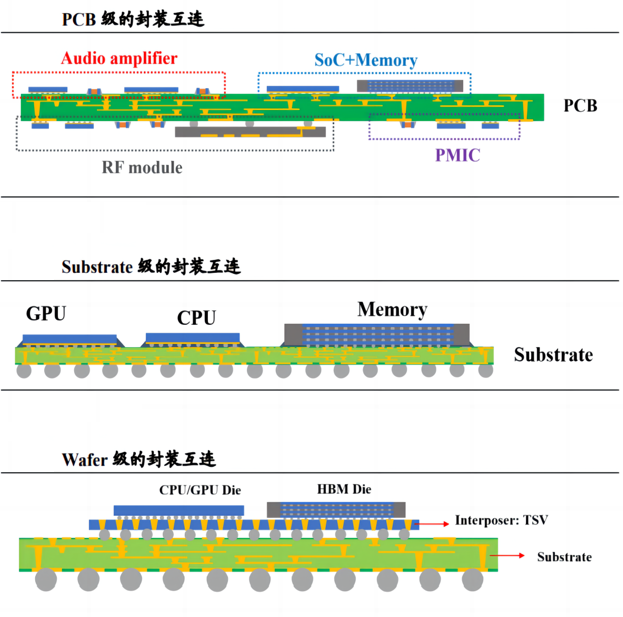

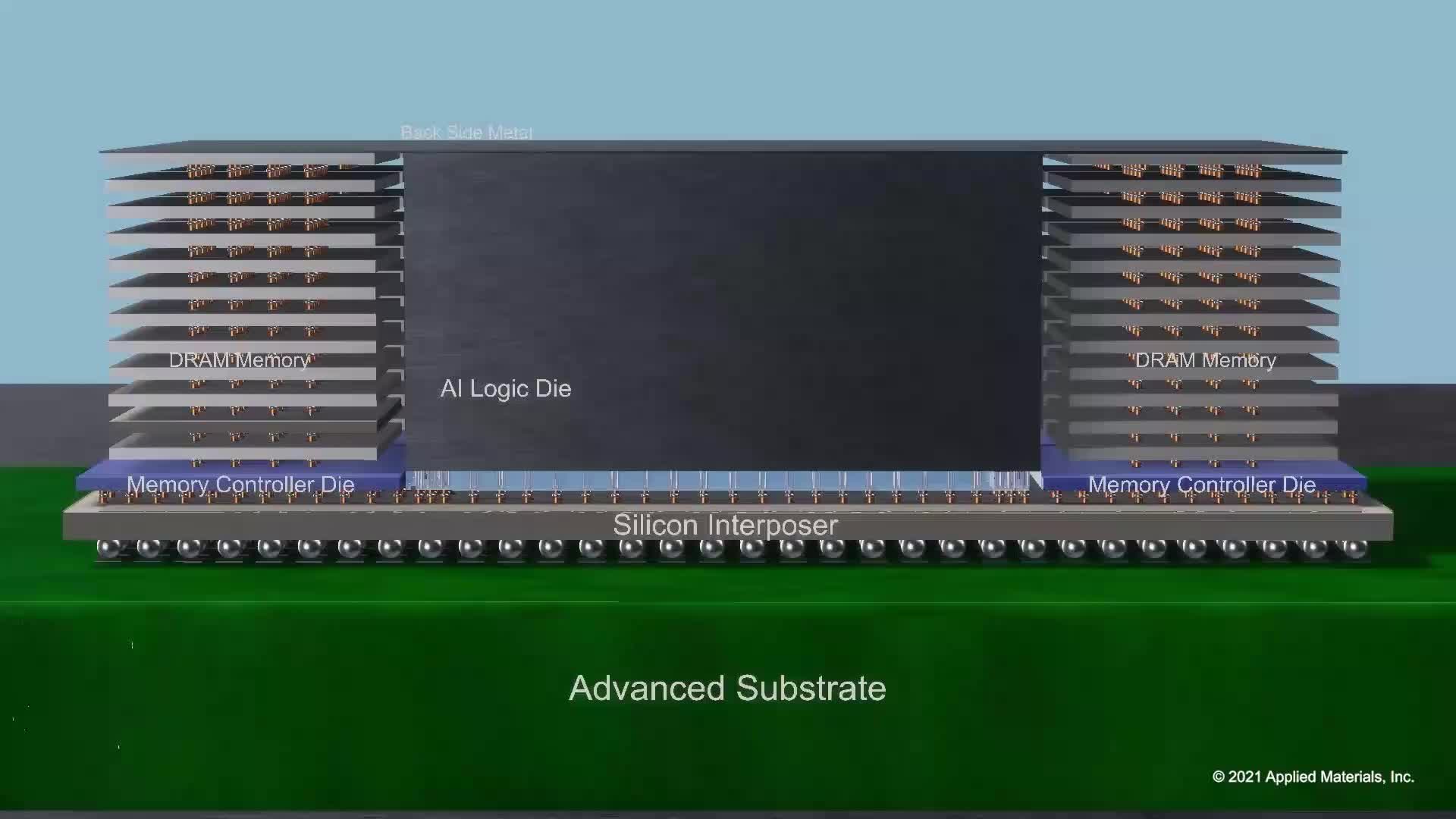

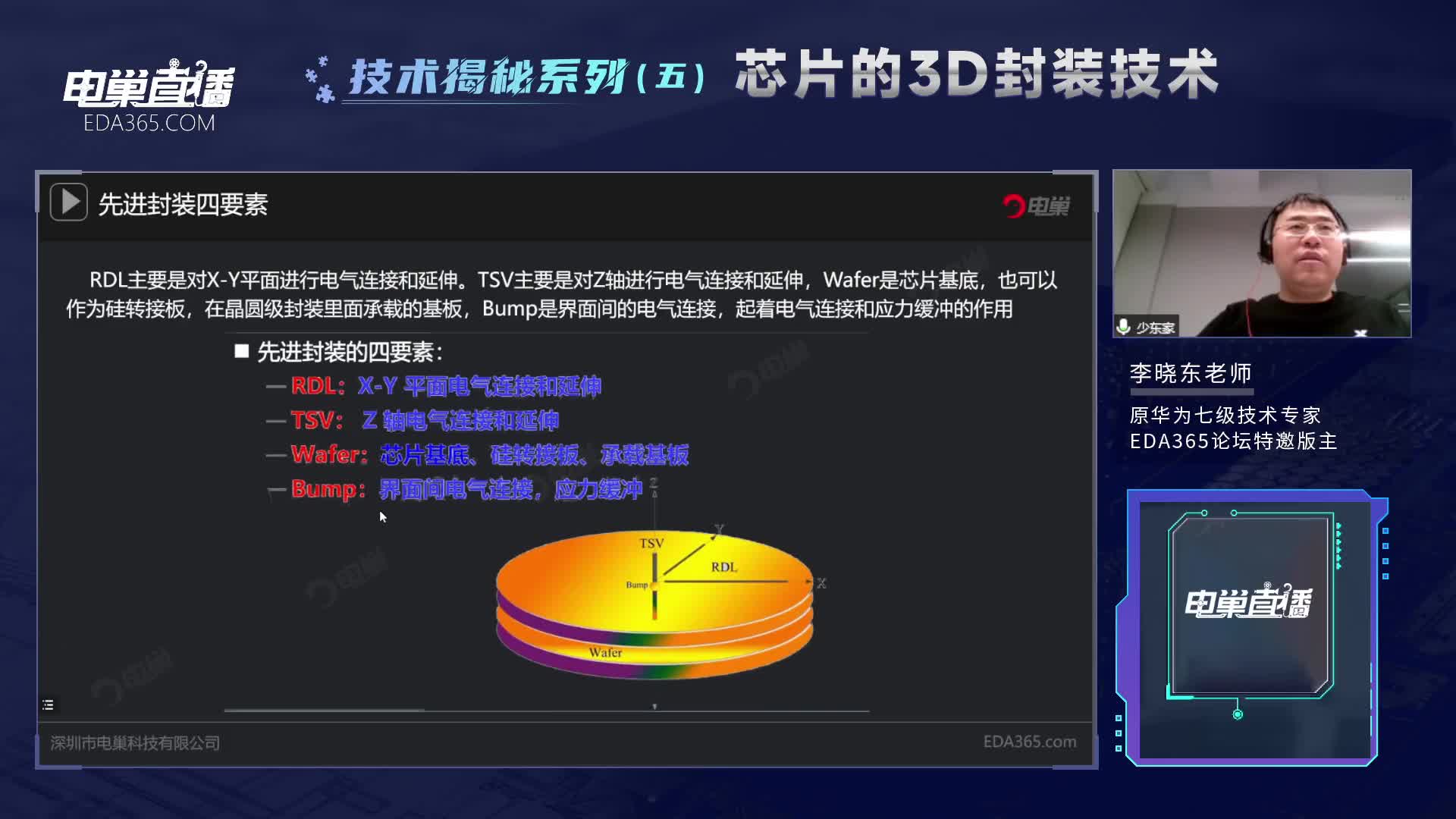

先进封装技术以SiP、WLP、2.5D/3D为三大发展重点。先进封装核心技术包括Bumping凸点、RDL重布线、硅中介层和TSV通孔等,依托这些技术的组合各厂商发展出了满足多样化需求的封装解决方案,SiP系统级封装、WLP晶圆级封装、2.5D/3D封装为三大发展重点。

2023-09-28 15:29:37 1614

1614

Chiplet主流封装技术都有哪些? 随着处理器和芯片设计的发展,芯片的封装技术也在不断地更新和改进。Chiplet是一种新型的封装技术,它可以将不同的芯片功能模块制造在不同的芯片中,并通过

2023-09-28 16:41:00 1347

1347 此时先进封装开始崭露头角,以苹果和台积电为代表,开启了一场新的革命,其主要分为两大类,一种是基于XY平面延伸的先进封装技术,主要通过RDL进行信号的延伸和互连;第二种则是基于Z轴延伸的先进封装技术,主要通过TSV进行信号延伸和互连。

2023-10-10 17:04:30 573

573

半导体产品在由二维向三维发展,从技术发展方向半导体产品出现了系统级封装(SiP)等新的封装方式,从技术实现方法出现了倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelpackage),2.5D封装(interposer,RDL等),3D封装(TSV)等先进封装技术。

2023-10-31 09:16:29 836

836

我们为什么需要了解一些先进封装?

2023-11-23 16:32:06 281

281

先进封装基本术语

2023-11-24 14:53:10 362

362

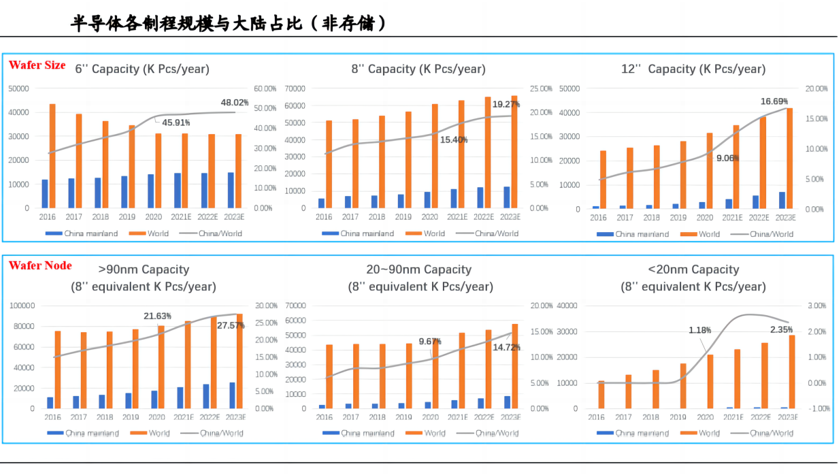

相比于晶圆制造,中国大陆封测环节较为成熟,占据全球封测接近40%的份额,但中国大陆先进封装的渗透率较低,2022年仅为14%,低于全球45%的渗透率。在制程工艺受到外部制裁的背景下

2023-11-25 15:44:25 740

740 、主流技术和应用场景,以及面临的挑战和问题。进而提出采用Chiplet技术,将不同的功能模块独立集成为独立的Chiplet,并融合在一个AI芯片上,从而实现更高的计算能力。该设计不仅允许独立开发和升级各个模块,还可在封装过程中将它们巧妙组合起

2023-12-08 10:28:07 281

281

先进的封装技术可以将多个半导体芯片和组件集成到高性能的系统中。随着摩尔定律的缩小趋势面临极限,先进封装为持续改善计算性能、节能和功能提供了一条途径。但是,与亚洲相比,美国目前在先进封装技术方面落后

2023-12-14 10:27:14 383

383

作为全球领先的芯片封测企业,长电科技深刻理解先进的封装设计能力对于确保半导体行业的产品性能、功能和成本至关重要。大规模高密度的集成电路为产品设计提供了极大的灵活性。例如Chiplet等前沿技术包含

2023-12-18 11:11:46 390

390 中国半导体行业协会副秘书长兼封测分会秘书长徐冬梅受邀出席大会并致辞,她表示,本次大会立足本土、协同全球,重点关注异构集成Chiplet技术、先进封装与SiP的最新进展,聚焦于HPC、AI、汽车等关键应用领域,是Chiplet生态圈的一次重要聚会。

2023-12-29 16:36:34 311

311 组件。这种技术的核心思想是将大型集成电路拆分成更小、更模块化的部分,以便更灵活地设计、制造和组装芯片。Chiplet技术可以突破单芯片光刻面积的瓶颈,减少对先进工艺制程的依赖,提高芯片的性能并降低制造成本。

2024-01-08 09:22:08 656

656 芯片的先进封装是一种超越摩尔定律的重要技术,它可以提供更好的兼容性和更高的连接密度,使得系统集成度的提高不再局限于同一颗芯片。

2024-01-16 14:53:51 302

302 level package),2.5D封装(interposer,RDL等),3D封装(TSV)等先进封装技术。 审核编辑 黄宇

2024-02-21 10:34:20 178

178

因为AI芯片需求的大爆发,台积电先进封装产能供不应求,而且产能供不应求的状况可能延续到2025年;这是台积电总裁魏哲家在法人说明会上透露的。 而且台积电一直持续的扩张先进封装产能,但是依然不能满足AI的强劲需求;这在一定程度会使得其他相关封装厂商因为接受转单而受益。

2024-01-22 18:48:08 565

565 )和集成电路的飞速发展,人工智能芯片逐渐成为全球科技竞争的焦点。在后摩尔时代,AI 芯片的算力提升和功耗降低越来越依靠具有硅通孔、微凸点、异构集成、Chiplet等技术特点的先进封装技术。从 AI 芯片的分类与特点出发,对国内外典型先进封装技术

2024-03-04 18:19:18 582

582

台积电计划在嘉义科学园区投资超过5000亿元新台币,建设六座先进封装厂,这一举措无疑将对半导体产业产生深远影响。

2024-03-20 11:28:14 335

335 Bump Metrology system—BOKI_1000在半导体行业中,Bump、RDL、TSV、Wafer合称先进封装的四要素,其中Bump起着界面互联和应力缓冲的作用。Bump是一种金属凸

2023-09-06 14:26:09

电子发烧友App

电子发烧友App

评论