CoWoS封装技术

CoWoS背景

“封测厂已经跟不上晶圆代工的脚步了,摩尔定律都开始告急了,我们与其在里面干着急,不如做到外面去”,2011年,台积电的余振华面对媒体如是说。2011年,台积电宣布将会做先进封装。经过两年时间,台积电开发出了CoWoS技术。但由于价格昂贵,只有Xilinx使用,为了拿下苹果这个客户,台积电开发出了一种精简的设计,能够将CoWoS结构尽量简化,并且价格压到原来的五分之一。这个技术就是后来的InFO技术。

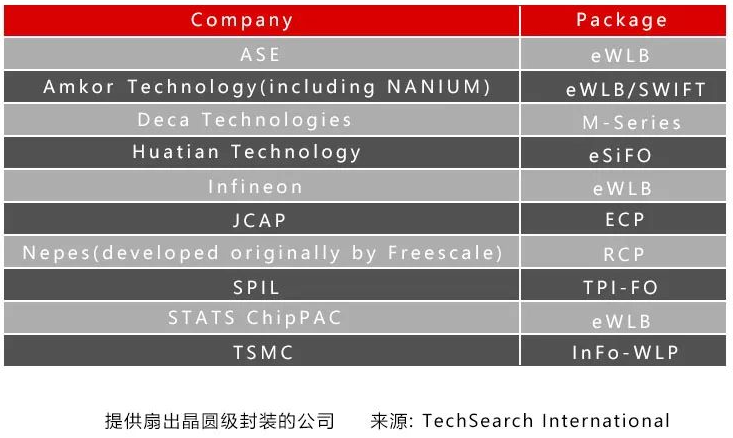

自此,台积电的先进封装分成了两部分,更为经济的InFO封装技术,成为收集客户采用的首选,这也是台积电拿下苹果这个客户的原因。而专注于高阶客户市场的CoWoS技术也因为人工智能的发展,得到进一步发展与应用。

2012年台积电在与赛灵思合作推出Virtex-7 HT系列FPGA的过程中(由4颗28nm FPGA芯片并排安装在硅中介层)便开发了TSV、μBump及RDL技术,并将这一系列技术命名为CoWoS(Chip-on-Wafer-on-Substrate)[3]。随后公司研发出InFO封装,大幅降低了封装体积[4]。2018年,台积电又公布了系统整合单芯片(SoIC)技术,标志着台积电已具备直接为客户生产3DIC的能力。

CoWoS技术

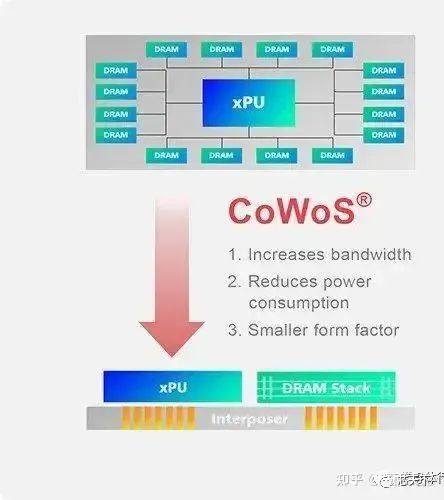

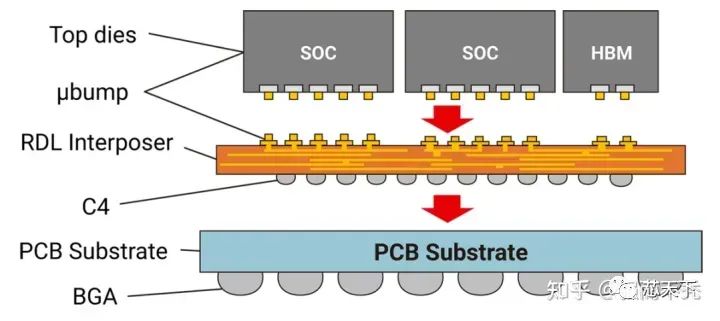

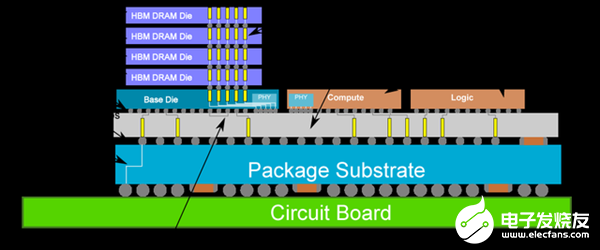

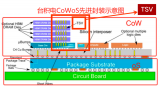

CoWoS 技术概念,简单来说是先将半导体芯片(像是处理器、记忆体等),一同放在硅中介层上,再透过Chip on Wafer(CoW)的封装制程连接至底层基板上。换言之,也就是先将芯片通过Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把CoW 芯片与基板连接,整合成CoWoS;利用这种封装模式,使得多颗芯片可以封装到一起,透过Si Interposer 互联,达到了封装体积小,功耗低,引脚少的效果。

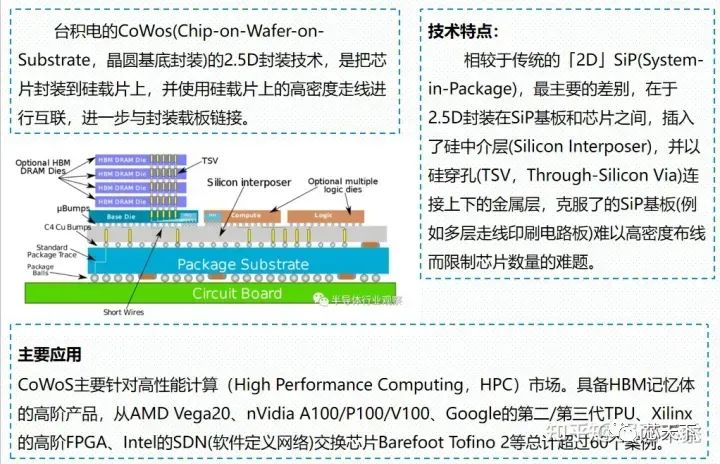

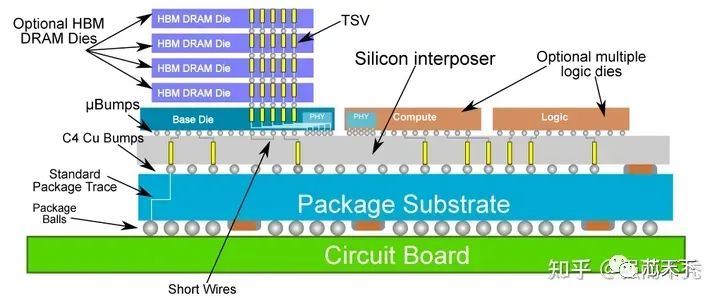

2.5D封装:所谓的2.5D 封装,主要的概念是将处理器、记忆体或是其他的芯片,并列排在硅中介板(Silicon Interposer)上,先经由微凸块(Micro Bump)连结,让硅中介板之内金属线可连接不同芯片的电子讯号;接着再透过硅穿孔(TSV)来连结下方的金属凸块(Solder Bump),再经由导线载板连结外部金属球,实现芯片、芯片与封装基板之间更紧密的互连。

· RDL(Redistributionlayer,再分布层):在晶圆水平上,触点再分布可以很高效的进行。再分布层用于使连线路径重新规划,落到我们希望的区域,也可以获得更高的触点密度。再分布的过程,实际上是在原本的晶圆上又加了一层或几层。首先淀积的是一层电介质用于隔离,接着我们会使原本的触点裸露,再淀积新的金属层来实现重新布局布线。UBM在这里会被用到,作用是支撑焊锡球或者其他材料的接触球。

· 中介层(Interposer):指的是焊锡球和晶粒之间导电层。它的作用是扩大连接面,使一个连接改线到我们想要的地方。与再分布层作用类似。

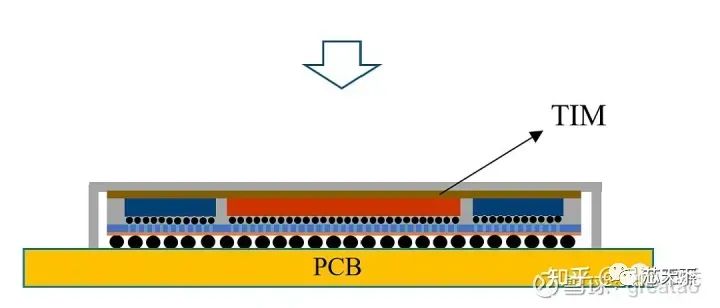

· TIM:热界面材料 (hermal interface material:TIM) 薄膜通常包含在高级封装中,以帮助降低从有源die到周围环境的总热阻。(对于非常高功率的器件,通常应用两层 TIM 材料层——die和封装盖之间的内层以及封装和散热器之间的一层。)

CoWoS(Chip On Wafer On Substrate)是一种2.5D的整合生产技术,先将芯片通过Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把CoW芯片与基板(Substrate)连接,整合成CoWoS。

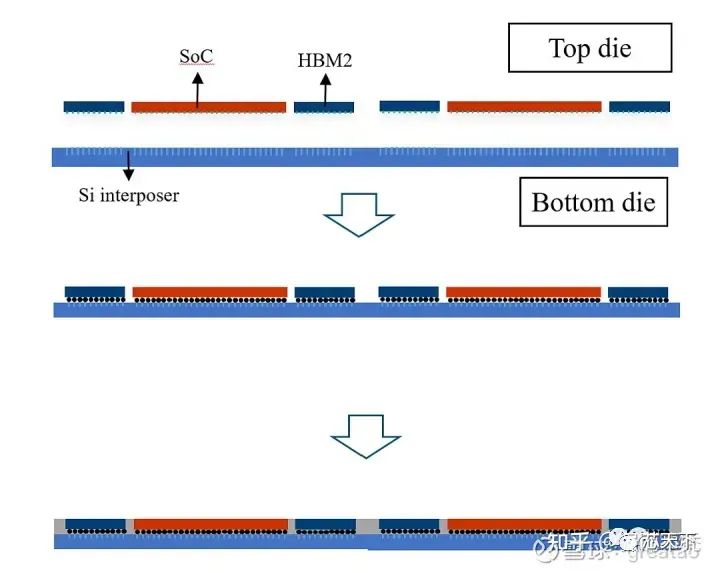

CoWoS process Flow如下:

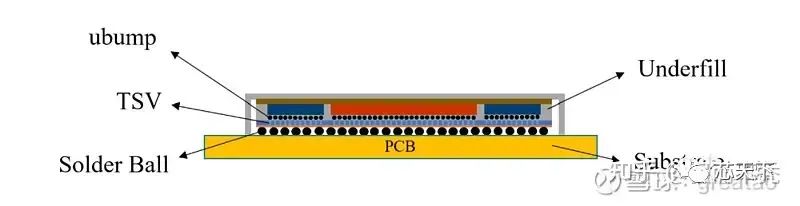

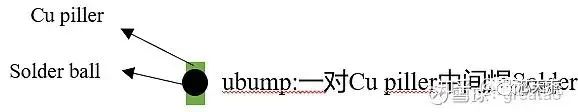

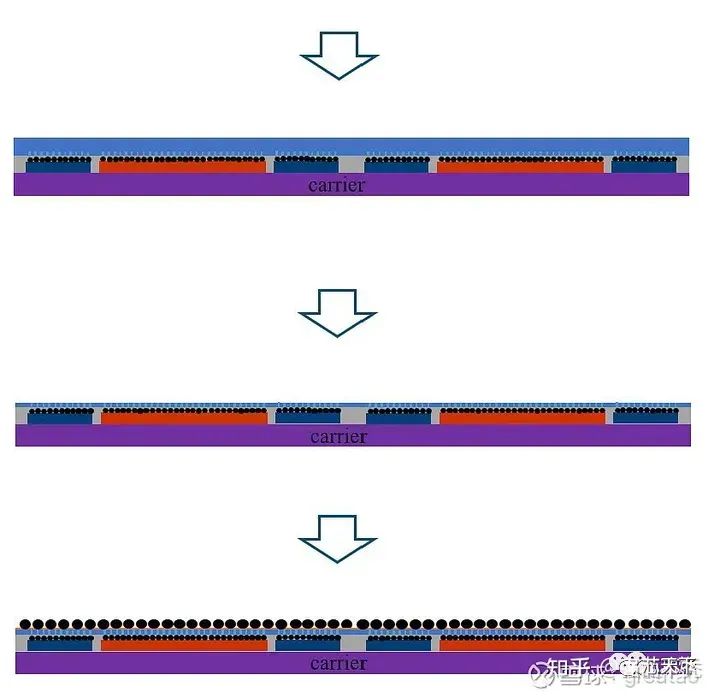

先将芯片通过Si interposer与下面的wafer堆叠在一起,其中连接部分叫ubump,是一对Cu piller中间焊Solder,填入underfill保护芯片与连接的结构

将芯片连接在载板上,然后进行CMP将Si interposer减薄,接着加入RDL与Solder ball。

将wafer从载板上转移到胶带上,切割wafer,将芯片从胶带上取下来倒置安装在基板上。

最后加上保护结构并使用热界面金属(TIM)填充保护盖与芯片中间的空隙。

CoWoS封装结构简图

CoWoS封装技术发展

(1)CoWoS—S

CoWoS平台为高性能计算应用提供了同类最佳的性能和最高的集成密度。这种晶圆级系统集成平台提供了广泛的内插器尺寸、HBM立方体数量和封装尺寸。它可以实现比2倍掩模版尺寸(或约1,700mm2)更大的内插器,将领先的SoC芯片与四个以上的HBM2/HBM2E立方体集成在一起。

CoWoS—R

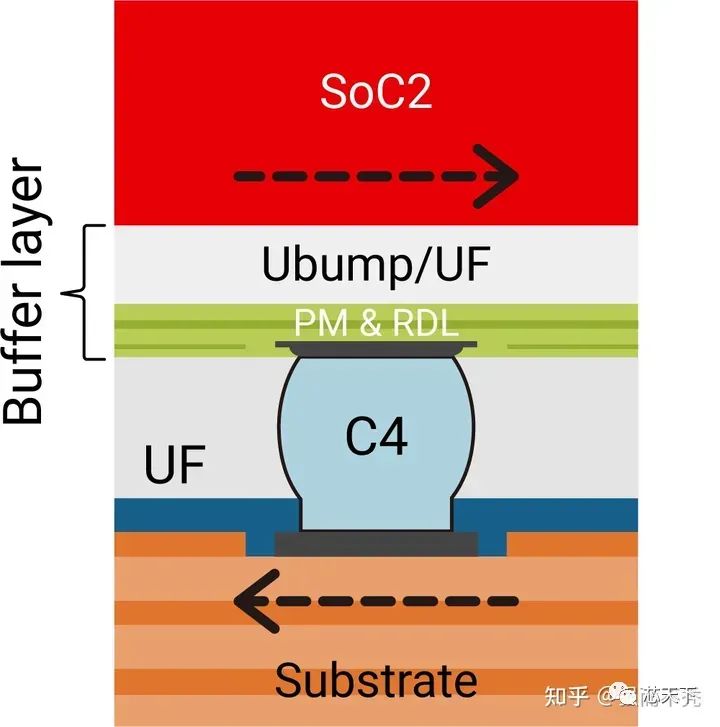

CoWoS-R是CoWoS高级封装家族的一员,利用InFO技术利用RDL内插器并服务于小芯片之间的互连,尤其是在HBM(高带宽存储器)和SoC异构集成方面。RDL内插器由聚合物和铜迹线组成,在机械上相对灵活。这种灵活性增强了C4关节的完整性,并允许新的封装可以扩大其规模,以满足更复杂的功能需求。

CoWoS-R技术的主要特点包括:

1.RDL内插器最多由6L铜层组成,用于最小布线。间距为4微米(2微米线宽/间距)。

2.RDL互连提供了良好的信号和电源完整性性能,路由线路的RC值更低,以实现高传输数据速率。带有六个RDL互连的共面GSGSG和层间接地屏蔽提供了出色的电气性能。

3.由于SoC和相应衬底之间的CTE失配,RDL层和C4/UF层提供了良好的缓冲效果。C4凸起使应变能密度大大降低。

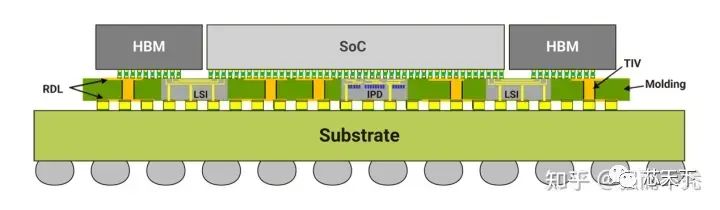

CoWoS—L

CoWoS-L作为CoWoS平台中的最后一个芯片级封装之一,结合了CoWoS-S和InFO技术的优点,使用内插器与LSI (Local Silicon Interconnect)芯片提供了最灵活的集成,用于管芯到管芯的互连,RDL层用于功率和信号传递。该产品从1.5倍掩模版插入器尺寸开始,具有1倍SoC+4倍HBM立方体,并将进一步扩展外壳至更大尺寸,以集成更多芯片。

CoWoS-L服务的主要特点包括:

1.大规模集成电路芯片,用于通过多层亚微米铜线实现高布线密度的管芯间互连。大规模集成电路芯片可以在每个产品中采用多种连接架构(例如,SoC到SoC、SoC到小芯片、SoC到HBM等),也可以在多个产品中重复使用。相应的金属类型、层数和间距与CoWoS-S的产品一致

2.基于模制的内插器在正面和背面都具有宽间距的RDL层,并且用于信号和功率传输的TIV(直通内插器通路)在高速传输中提供了低损耗的高频信号。

3.能够在片上系统芯片的正下方集成额外的元件,例如独立的IPD(集成无源器件),以更好的PI/SI支持其信号通信。

芯片的布局设计,遂成为延续摩尔定律的新解方,异构整合(Heterogeneous Integration Design Architecture System,HIDAS)概念便应运而生,同时成为IC 芯片的创新动能。

所谓的异构整合,广义而言,就是将两种不同的芯片,例如记忆体+逻辑芯片、光电+电子元件等,透过封装、3D 堆叠等技术整合在一起。换句话说,将两种不同制程、不同性质的芯片整合在一起,都可称为是异构整合。

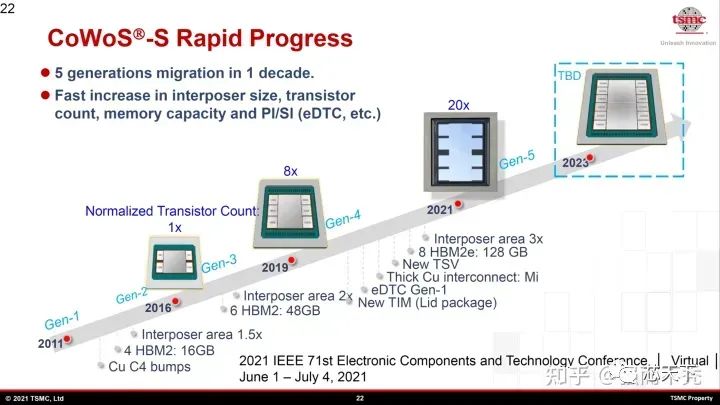

图 CoWoS 封装技术的路线图

相比第三代技术,第五代CoWoS-S的晶体管数量将增加20倍,中介层面积也会提升3倍。第五代封装技术还将封装8个128G的HBM2e内存和2颗大型SoC内核。

2010 年开始 2.5D Interposer 的研发,2011 年推出 2.5D Interposer 技术 CoWoS(Chip on Wafer on Substrate)。第一代 CoWoS 采用 65 纳米工艺,线宽可以达到 0.25µm,实现 4 层布线,为 FPGA、GPU 等高性能产品的集成提供解决方案。

真正引爆 CoWoS 的产品是人工智能(AI)芯片。2016 年,英伟达(Nvidia)推出首款采用 CoWoS 封装的绘图芯片 GP100,为全球 AI 热潮拉开序幕;2017 年 Google 在 AlphaGo 中使用的 TPU 2.0 也采用 CoWoS 封装;2017 年英特尔(Intel)的 Nervana 也不例外的交由台积电代工,采用 CoWoS 封装。因成本高昂而坐冷板凳多年 CoWoS 封测产能在 2017 年首度扩充。

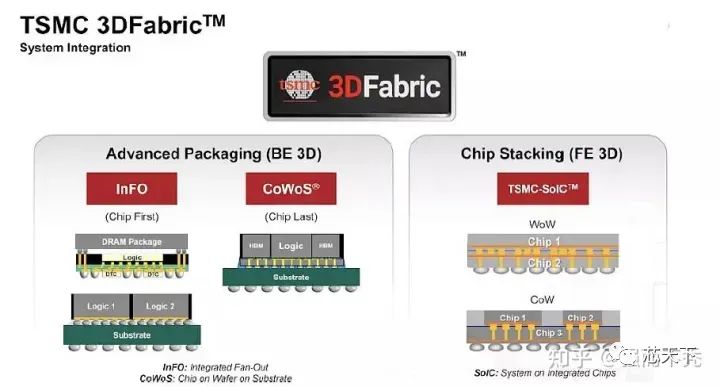

4、3D Fabric

去年,台积电将他们的 2.5D 和 3D 封装产品合并为一个单一的、全面的品牌3DFabric。

其中,2.5D封装技术CoWoS可分为 CoWoS 和 InFO 系列。台积电的3D封装技术则是SoIC。

据台积电介绍,公司的3D 封装与 SoIC 平台相关联,该平台使用堆叠芯片和直接焊盘键合,面对面或面对背方向 -表示为 SoIC 晶圆上芯片(chip on wafer)。硅通孔(TSV) 通过 3D 堆栈中的die提供连接。

编辑:黄飞

电子发烧友App

电子发烧友App

评论