高密度扇出型封装技术满足了移动手机封装的外形尺寸与性能要求,因此获得了技术界的广泛关注。

2020-07-13 15:03:21 858

858

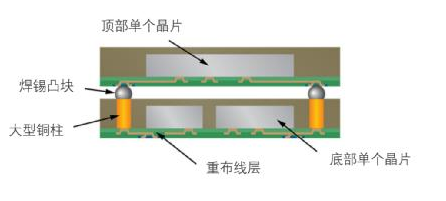

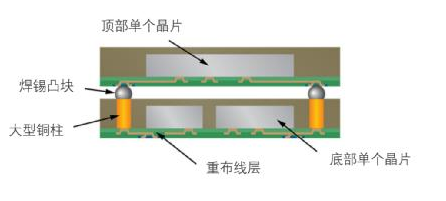

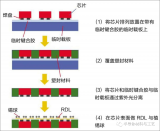

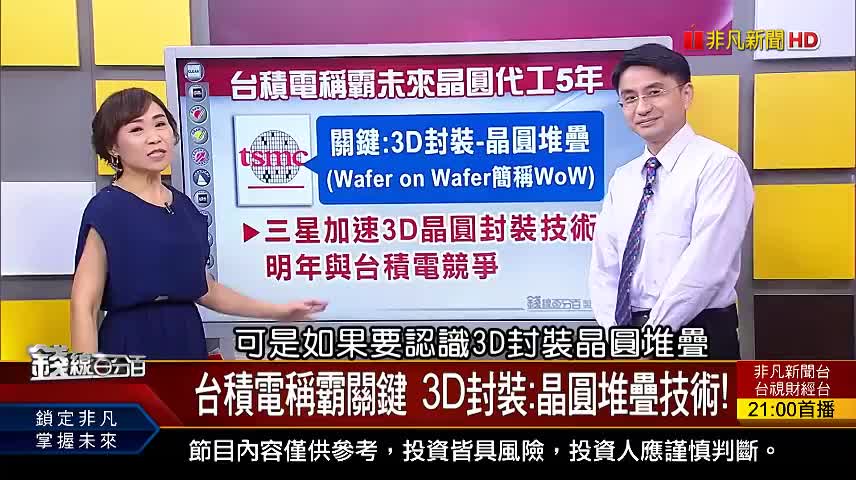

扇出型圆片级封装(FoWLP)是圆园片级封装中的一种。相对于传统封装圆片级封装具有不需要引线框、基板等介质的特点,因此可以实现更轻、薄短、小的封装。扇出型圆片级封装也可以支持多芯片、2.5D/3D

2023-05-08 10:33:17 1071

1071

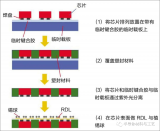

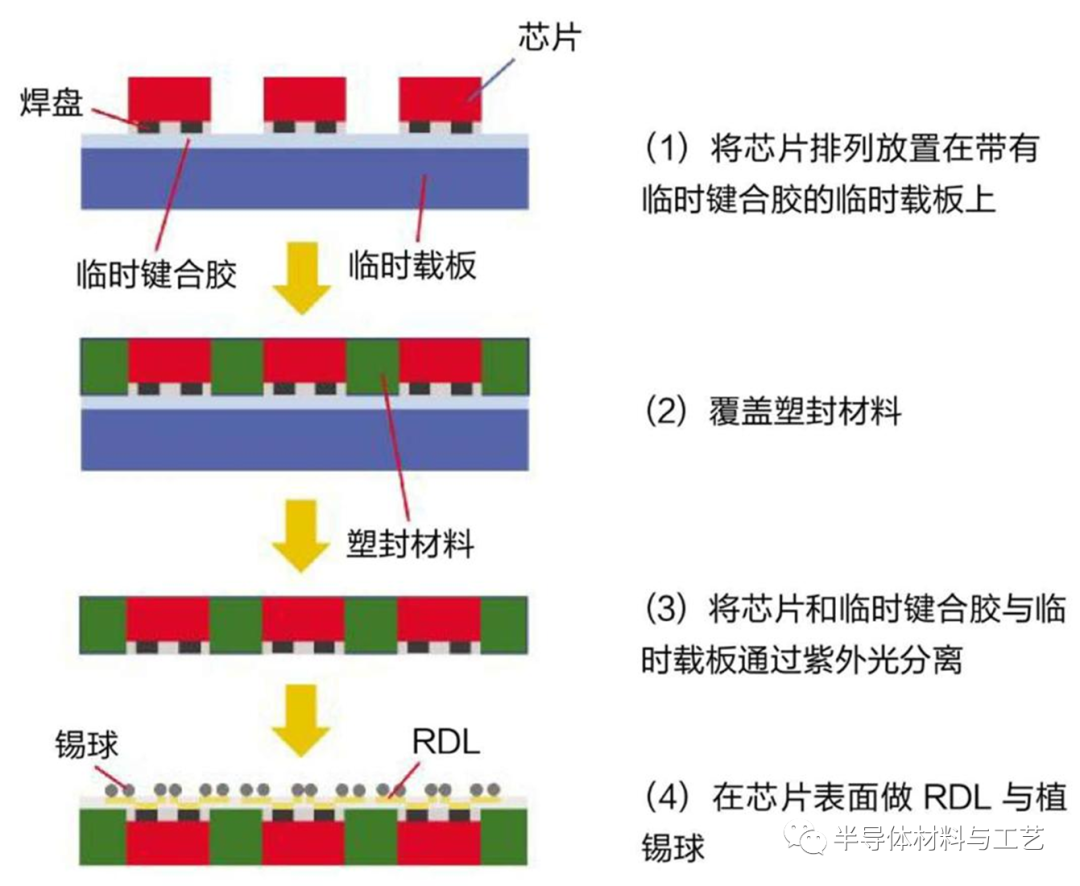

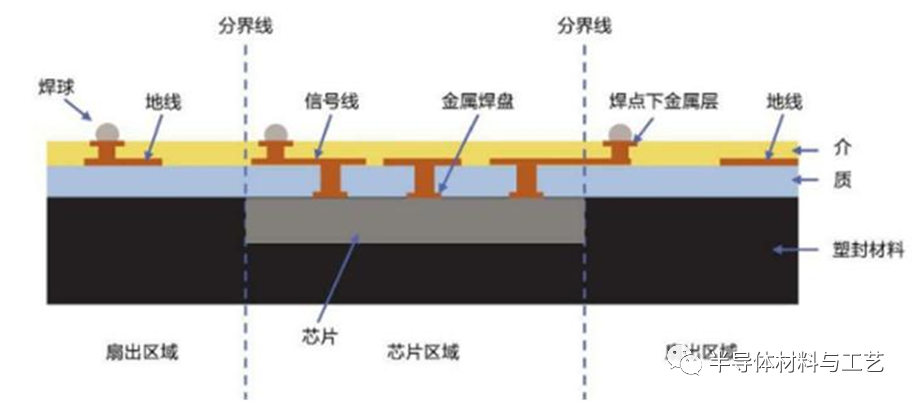

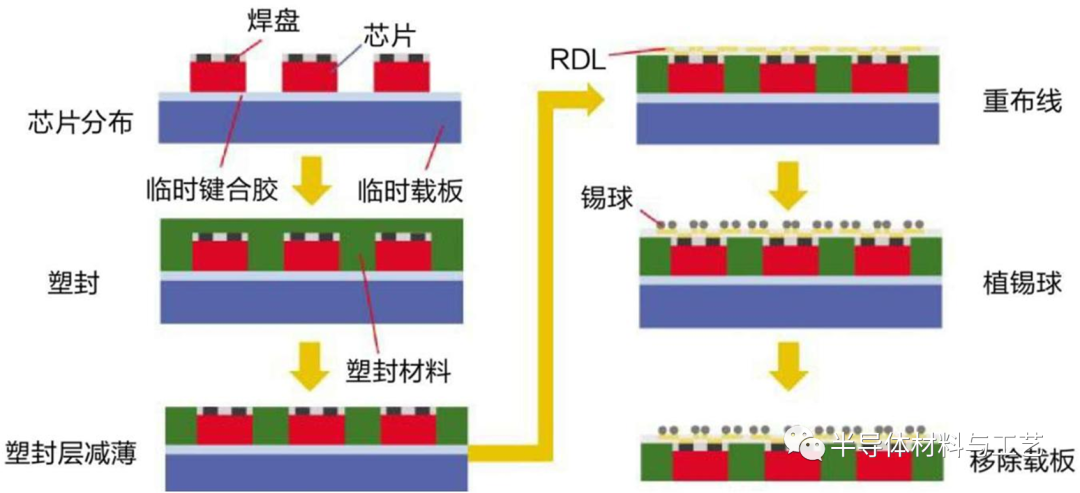

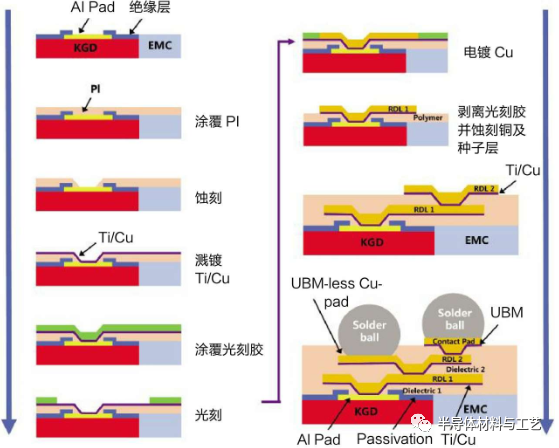

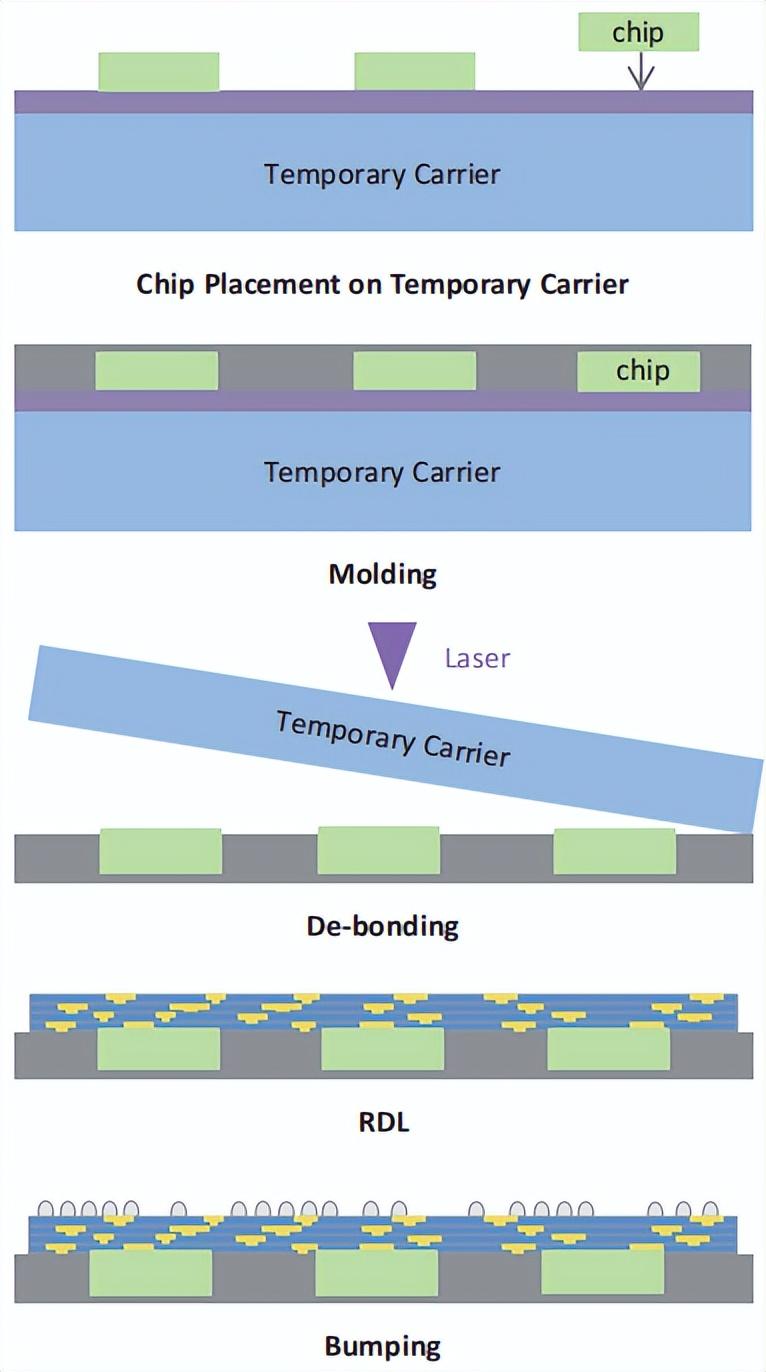

扇出型晶圆级封装技术采取在芯片尺寸以外的区域做I/O接点的布线设计,提高I/O接点数量。采用RDL工艺让芯片可以使用的布线区域增加,充分利用到芯片的有效面积,达到降低成本的目的。扇出型封装技术完成芯片锡球连接后,不需要使用封装载板便可直接焊接在印刷线路板上,这样可以缩短信号传输距离,提高电学性能。

2023-09-25 09:38:05 756

756

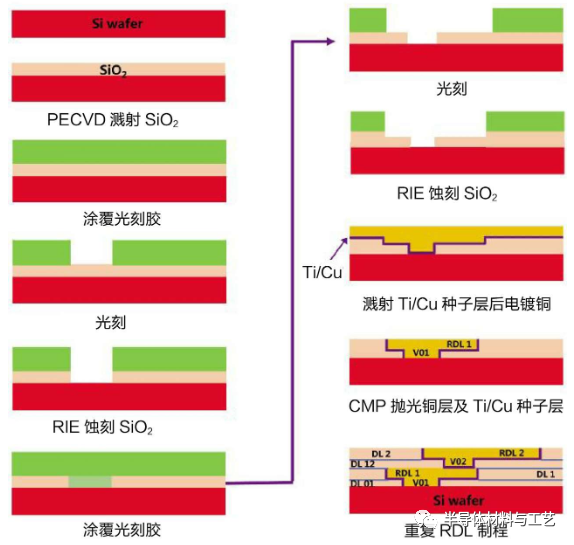

扇出型封装一般是指,晶圆级/面板级封装情境下,封装面积与die不一样,且不需要基板的封装,也就是我们常说的FOWLP/FOPLP。扇出型封装的核心要素就是芯片上的RDL重布线层(可参考下面图表说明

2023-11-27 16:02:01 2459

2459

本文的目的是了解为什么Deca的扇出技术最近被高通用于其PMIC扇入WLP die的保护层。严格的说,这仍旧是一个扇入die与侧壁钝化所做的扇出封装。因此,本文的第一部分将描述扇入式WLP市场以及

2019-07-05 14:21:31 7031

7031 。该方法与晶圆微调法相似,通过调整输入级上的电阻器来校正失调电压。但是在这种应用实例中,调整工作是在器件最终封装后完成。调整方法通常是在最后封装级制造测试过程中将数字信号应用于输出。微调完成后,微调

2018-09-18 07:56:15

有人又将其称为圆片级-芯片尺寸封装(WLP-CSP),以晶圆圆片为加工对象,在晶圆上封装芯片。晶圆封装中最关键的工艺为晶圆键合,即是通过化学或物理的方法将两片晶圆结合在一起,以达到密封效果。如下

2021-02-23 16:35:18

晶圆级封装技术Wafer Level Package Technology Board Mounting Application Note for 0.800mm pitch

2009-06-12 23:57:22

晶圆级封装技术源自于倒装芯片。晶圆级封装的开发主要是由集成器件制造厂家(IBM)率先启动。1964年,美国IBM公司在其M360计算器中最先采用了FCOB焊料凸点倒装芯片器件。

2020-03-06 09:02:23

晶圆级封装类型及涉及的产品

2015-07-11 18:21:31

晶圆级CSP的返修工艺包括哪几个步骤?晶圆级CSP对返修设备的要求是什么?

2021-04-25 08:33:16

晶圆级CSP的元件如何重新贴装?怎么进行底部填充?

2021-04-25 06:31:58

细间距的晶圆级CSP时,将其当做倒装晶片并采用助焊剂浸蘸的方法进行组装,以取代传统的焊膏印刷组装,如图2所示,首先将晶圆级CSP浸蘸在设定厚度的助焊剂薄膜中,然后贴装,再回流焊接,最后底部填充(如果有要求)。关于锡膏装配和助焊剂装配的优缺点。图1 工艺流程1——锡膏装配图2 工艺流程2——助焊剂装配

2018-09-06 16:24:04

晶圆级CSP装配回流焊接工艺控制,看完你就懂了

2021-04-25 06:28:40

; ·尺寸和位置精度受阻焊膜窗口的影响,不适合密间距元件的装配。 NSMD焊盘的尺寸和位置不受阻焊膜窗口的影响,在焊盘和阻焊膜之间有一定空隙,如图2和图3所示。对于 密间距晶圆级CSP,印刷电路板上的焊盘

2018-09-06 16:32:27

晶圆级CSP的装配对贴装压力控制、贴装精度及稳定性、照相机和影像处理技术、吸嘴的选择、助焊剂应 用单元和供料器,以及板支撑及定位系统的要求类似倒装晶片对设备的要求。WLCSP贴装工艺的控制可以参

2018-09-06 16:32:18

先进封装发展背景晶圆级三维封装技术发展

2020-12-28 07:15:50

晶圆级芯片封装技术是对整片晶圆进行封装测试后再切割得到单个成品芯片的技术,封装后的芯片尺寸与裸片一致。

2019-09-18 09:02:14

在库存回补需求带动下,包括环球晶、台胜科、合晶、嘉晶等硅晶圆厂第二季下旬出货续旺,现货价出现明显上涨力道,合约价亦确认止跌回升。 新冠肺炎疫情对半导体材料的全球物流体系造成延迟影响,包括晶圆

2020-06-30 09:56:29

晶圆凸点模板技术和应用效果评价详细介绍了晶圆凸点目前的技术现状,应用效果,通过这篇文章可以快速全面了解晶圆凸点模板技术晶圆凸点模板技术和应用效果评价[hide][/hide]

2011-12-02 12:44:29

` 晶圆级封装是一项公认成熟的工艺,元器件供应商正寻求在更多应用中使用WLP,而支持WLP的技术也正快速走向成熟。随着元件供应商正积极转向WLP应用,其使用范围也在不断扩大。 目前有5种成熟

2011-12-01 14:33:02

`晶圆切割目的是什么?晶圆切割机原理是什么?一.晶圆切割目的晶圆切割的目的,主要是要将晶圆上的每一颗晶粒(Die)加以切割分离。首先要将晶圆(Wafer)的背面贴上一层胶带(Wafer Mount

2011-12-02 14:23:11

是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻

2011-12-01 15:43:10

圆比人造钻石便宜多了,感觉还是很划算的。硅的纯化I——通过化学反应将冶金级硅提纯以生成三氯硅烷硅的纯化II——利用西门子方法,通过三氯硅烷和氢气反应来生产电子级硅 二、制造晶棒晶体硅经过高温成型,采用

2019-09-17 09:05:06

`微晶片制造的四大基本阶段:晶圆制造(材料准备、长晶与制备晶圆)、积体电路制作,以及封装。晶圆制造过程简要分析[hide][/hide]`

2011-12-01 13:40:36

晶圆制造的基础知识,适合入门。

2014-06-11 19:26:35

所用的硅晶圆。) 通过使用化学、电路光刻制版技术,将晶体管蚀刻到硅晶圆之上,一旦蚀刻是完成,单个的芯片被一块块地从晶圆上切割下来。 在硅晶圆图示中,用黄点标出的地方是表示这个地方存在一定缺陷,或是

2011-12-01 16:16:40

晶圆是指硅半导体集成电路制作所用的硅晶片,由于其形状为圆形,故称为晶圆;在硅晶片上可加工制作成各种电路元件结构,而成为有特定电性功能之IC产品。晶圆的原始材料是硅,而地壳表面有用之不竭的二氧化硅

2011-12-01 14:53:05

`美国Tekscan公司研发的I-SCAN系统可以解决晶圆制作过程中抛光头与晶圆接触表面压力分布不均匀,导致高不良率出现的问题。在实验过程中只需要将目前世界上最薄的压力传感器(0.1mm)放置于抛光

2013-12-04 15:28:47

。您能否告诉我们您对晶圆探针去嵌入技术的可行性的看法? 以上来自于谷歌翻译 以下为原文We would like to characterize our co-planar wafer probes

2019-01-23 15:24:48

` 谁来阐述一下晶圆有什么用?`

2020-04-10 16:49:13

晶圆的制造过程是怎样的?

2021-06-18 07:55:24

,然后切割成一片一片薄薄的晶圆。会听到几寸的晶圆厂,如果硅晶圆的直径越大,代表著这座晶圆厂有较好的技术。另外还有scaling技术可以将电晶体与导线的尺寸缩小,这两种方式都可以在一片晶圆上,制作出更多

2011-09-07 10:42:07

`晶圆的结构是什么样的?1 晶格:晶圆制程结束后,晶圆的表面会形成许多格状物,成为晶格。经过切割器切割后成所谓的晶片 2 分割线:晶圆表面的晶格与晶格之间预留给切割器所需的空白部分即为分割线 3

2011-12-01 15:30:07

Plane):图中的剖面标明了器件下面的晶格构造。此图中显示的器件边缘与晶格构造的方向是确定的。(6)晶圆切面/凹槽(Wafer flats/notche):图中的晶圆有主切面和副切面,表示这是一个 P 型 晶向的晶圆(参见第3章的切面代码)。300毫米晶圆都是用凹槽作为晶格导向的标识。

2020-02-18 13:21:38

晶圆针测制程介绍 晶圆针测(Chip Probing;CP)之目的在于针对芯片作电性功能上的 测试(Test),使 IC 在进入构装前先行过滤出电性功能不良的芯片,以避免对不良品增加制造成

2020-05-11 14:35:33

`159-5090-3918回收6寸晶圆,8寸晶圆,12寸晶圆,回收6寸晶圆,8寸晶圆,12寸晶圆,花籃,Film Fram Cassette,晶元載具Wafer shipper,二手晶元盒

2020-07-10 19:52:04

请问有人用过Jova Solutions的ISL-4800图像测试仪吗,还有它可否作为CIS晶圆测试的tester,谢谢!

2015-03-29 15:49:20

MEMS器件有时也采用晶圆级封装,并用保护帽把MEMS密封起来,实现与外部环境的隔离或在下次封装前对MEMS器件提供移动保护。这项技术常常用于惯性芯片的封装,如陀螺仪和加速度计。这样的封装步骤是在MEMS

2010-12-29 15:44:12

晶圆级芯片级封装; 49 bumps; 3.29×3.29×0.54mm(包括背面涂层)

2022-12-06 06:06:48

SiC SBD 晶圆级测试 求助:需要测试的参数和测试方法谢谢

2020-08-24 13:03:34

的安全。下面给大家重点介绍回扫型ESD的新型封装技术CSP: TVS新型封装CSPCSP封装的概念:Chip Scale Package 芯片级封装 (晶圆级封装)WLP (WLP,Wafer

2020-07-30 14:40:36

`晶圆是如何生长的?又是如何制备的呢?本文的主要内容有:沙子转变为半导体级硅的制备,再将其转变成晶体和晶圆,以及生产抛光晶圆要求的工艺步骤。这其中包括了用于制造操作晶圆的不同类型的描述。生长

2018-07-04 16:46:41

效应和功耗。因此,三维系统集成技术在性能、功能和形状因素等方面都具有较大的优势。用于三维集成的先进晶圆级技术晶圆级封装技术已在许多产品制造中得到广泛应用。目前正在开发晶圆级封装的不同工艺技术,以满足在提高

2011-12-02 11:55:33

纳米到底有多细微?什么晶圆?如何制造单晶的晶圆?

2021-06-08 07:06:42

` 晶圆是指硅半导体集成电路制作所用的硅晶片,由于其形状为圆形,故称为晶圆;在硅晶片上可加工制作成各种电路元件结构,而成为有特定电性功能之IC产品。晶圆的原始材料是硅,而地壳表面有用之不竭的二氧化硅

2011-12-01 11:40:04

`晶圆级封装(WLP)就是在其上已经有某些电路微结构(好比古董)的晶片(好比座垫)与另一块经腐蚀带有空腔的晶片(好比玻璃罩)用化学键结合在一起。在这些电路微结构体的上面就形成了一个带有密闭空腔的保护

2011-12-01 13:58:36

的辅助。 测试是为了以下三个目标。第一,在晶圆送到封装工厂之前,鉴别出合格的芯片。第二,器件/电路的电性参数进行特性评估。工程师们需要监测参数的分布状态来保持工艺的质量水平。第三,芯片的合格品与不良品

2011-12-01 13:54:00

` 晶圆电阻又称圆柱型精密电阻、无感晶圆电阻、贴片金属膜精密电阻、高精密无感电阻、圆柱型电阻、无引线金属膜电阻等叫法;英文名称是:Metal Film Precision Resistor-CSR

2011-12-02 14:57:57

半导体晶圆(晶片)的直径为4到10英寸(10.16到25.4厘米)的圆盘,在制造过程中可承载非本征半导体。它们是正(P)型半导体或负(N)型半导体的临时形式。硅晶片是非常常见的半导体晶片,因为硅

2021-07-23 08:11:27

和测试都在晶片上进行。随着晶片尺寸的增大、管芯的缩小,WLP的成本不断降低。作为最早采用该技术的公司,Dallas Semiconductor在1999年便开始销售晶片级封装产品。2 命名规则 业界在

2018-08-27 15:45:31

请问像AD8233一样的晶圆封装在PCB中如何布线,芯片太小,过孔和线路都无法布入,或者有没有其他封装的AD8233

2023-11-14 07:01:48

1、为什么晶圆要做成圆的?如果做成矩形,不是更加不易产生浪费原料?2、为什么晶圆要多出一道研磨的工艺?为什么不能直接做成需求的厚度?

2014-01-20 15:58:42

越平整,克服弹性变形所做的工就越小,晶圆也就越容易键合。晶圆翘曲度的测量既有高精度要求,同时也有要保留其表面的光洁度要求。所以传统的百分表、塞尺一类的测量工具和测量方法都无法使用。以白光干涉技术为

2022-11-18 17:45:23

单晶的晶圆制造步骤是什么?

2021-06-08 06:58:26

, such as “N-type” and “P-type”.导电类型 - 晶圆片中载流子的类型,N型和P型。Contaminant, Particulate (see light point defect)污染微粒 (参见

2011-12-01 14:20:47

晶圆划片 (Wafer Dicing )将晶圆或组件进行划片或开槽,以利后续制程或功能性测试。提供晶圆划片服务,包括多项目晶圆(Multi Project Wafer, MPW)与不同材质晶圆划片

2018-08-31 14:16:45

`各位大大:手头上有颗晶圆的log如下:能判断它的出处吗?非常感谢!!`

2013-08-26 13:43:15

怎么选择晶圆级CSP装配工艺的锡膏?

2021-04-25 08:48:29

``揭秘切割晶圆过程——晶圆就是这样切割而成芯片就是由这些晶圆切割而成。但是究竟“晶圆”长什么样子,切割晶圆又是怎么一回事,切割之后的芯片有哪些具体应用,这些可能对于大多数非专业人士来说并不是十分

2011-12-01 15:02:42

固态图像传感器要求在环境大气中得到有效防护。第一代图像传感器安装在带玻璃盖的标准半导体封装中。这种技术能使裸片得到很好的密封和异常坚固的保护,但体积比较庞大,制造成本也比较高。引入晶圆级封装后

2018-12-03 10:19:27

`各位大大:手头上有颗晶圆的log如下:能判断它的出处吗?非常感谢!!`

2013-08-26 13:45:30

求晶圆划片或晶圆分捡装盒合作加工厂联系方式:QQ:2691003439

2019-03-13 22:23:17

激光用于晶圆划片的技术与工艺 激光加工为无接触加工,激光能量通过聚焦后获得高能量密度,直接将硅片

2010-01-13 17:01:57

随着集成电路设计师将更复杂的功能嵌入更狭小的空间,异构集成包括器件的3D堆叠已成为混合与连接各种功能技术的一种更为实用且经济的方式。作为异构集成平台之一,高密度扇出型晶圆级封装技术正获得越来越多

2020-07-07 11:04:42

看到了晶圆切割的一个流程,但是用什么工具切割晶圆?求大虾指教啊 ?

2011-12-01 15:47:14

越大,代表著这座晶圆厂有较好的技术。另外还有scaling技术可以将电晶体与导线的尺寸缩小,这两种方式都可以在一片晶圆上,制作出更多的硅晶粒,提高品质与降低成本。所以这代表6寸、8寸、12寸晶圆当中

2011-12-02 14:30:44

; 2010年1月3日,苏州天弘激光股份有限公司推出了新一代激光晶圆划片机,该激光划片机应用于硅晶圆、玻璃披覆(玻钝)二极管等半导体晶圆的划片和切割,技术领先于国内

2010-01-13 17:18:57

`一、照明用LED光源照亮未来 随着市场的持续增长,LED制造业对于产能和成品率的要求变得越来越高。激光加工技术迅速成为LED制造业普遍的工具,甚者成为了高亮度LED晶圆加工的工业标准。 激光

2011-12-01 11:48:46

SRAM中晶圆级芯片级封装的需求

2020-12-31 07:50:40

有没有做晶圆切割厂,封装厂的朋友,请教几个问题,谢谢!

2018-06-28 10:00:27

固态图像传感器要求在环境大气中得到有效防护。第一代图像传感器安装在带玻璃盖的标准半导体封装中。这种技术能使裸片得到很好的密封和异常坚固的保护,但体积比较庞大,制造成本也比较高。引入晶圆级封装后

2018-10-30 17:14:24

` 集成电路按生产过程分类可归纳为前道测试和后到测试;集成电路测试技术员必须了解并熟悉测试对象—硅晶圆。测试技术员应该了解硅片的几何尺寸形状、加工工艺流程、主要质量指标和基本检测方法;集成电路晶圆测试基础教程ppt[hide][/hide]`

2011-12-02 10:20:54

晶圆测温系统,晶圆测温热电偶,晶圆测温装置一、引言随着半导体技术的不断发展,晶圆制造工艺对温度控制的要求越来越高。热电偶作为一种常用的温度测量设备,在晶圆制造中具有重要的应用价值。本文

2023-06-30 14:57:40

WD4000无图晶圆几何形貌测量设备采用高精度光谱共焦传感技术、光干涉双向扫描技术,完成非接触式扫描并建立3D Mapping图,实现晶圆厚度、TTV、LTV、Bow、Warp、TIR、SORI、等

2024-01-10 11:10:39

传苹果在2016年秋天即将推出的新款智能型手机iPhone 7(暂订)上,将搭载采用扇出型晶圆级封装(Fan-out WLP;FOWLP)的芯片,让新iPhone更轻薄,制造成本更低。那什么是FOWLP封装技术呢?

2016-05-06 17:59:35 4579

4579 2017年依然炙手可热的扇出型封装行业 新年伊始,两起先进封装行业的并购已经曝光:维易科(Veeco)签订了8.15亿美元收购优特(Ultratech)的协议,安靠(Amkor Technology

2017-09-25 09:36:00 19

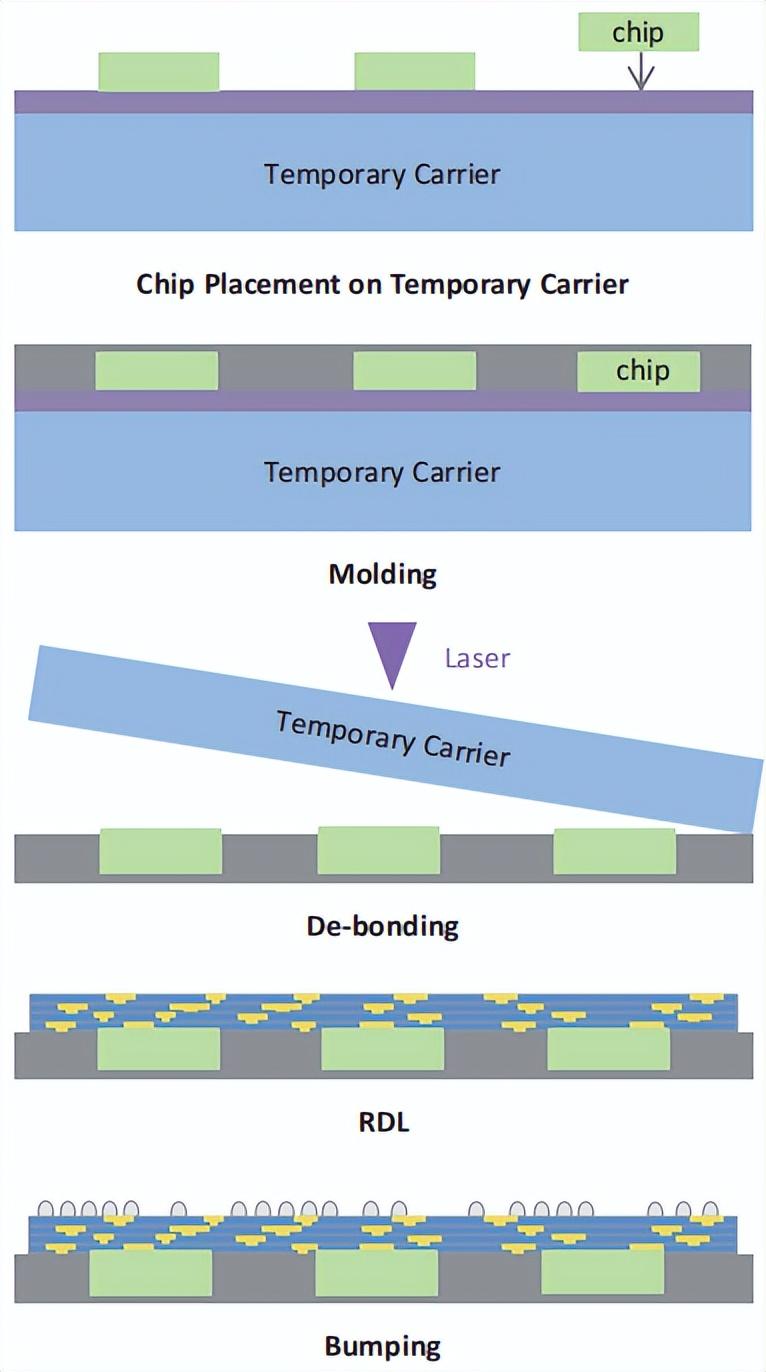

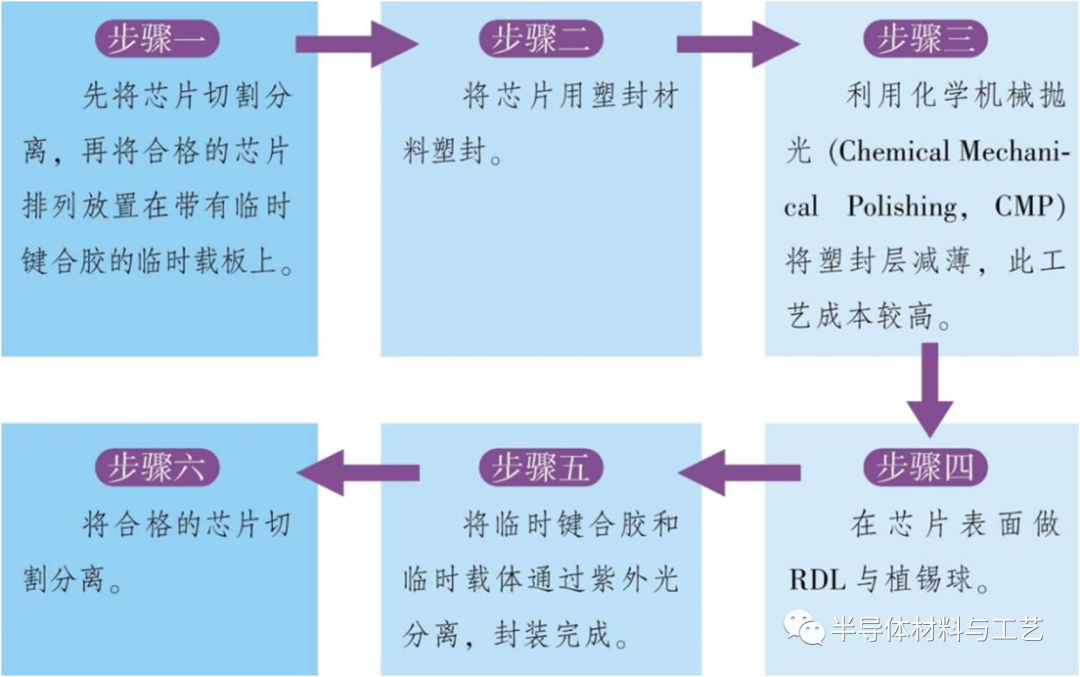

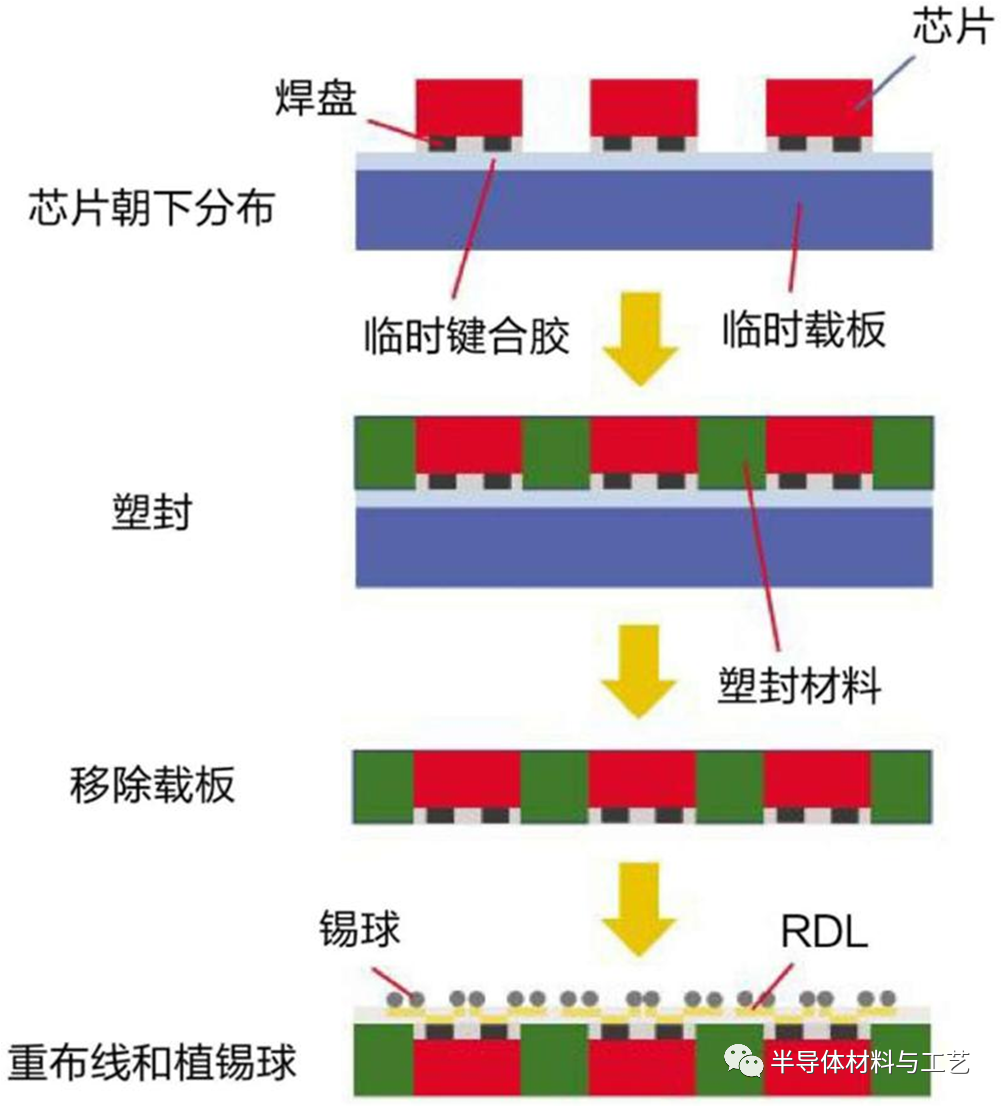

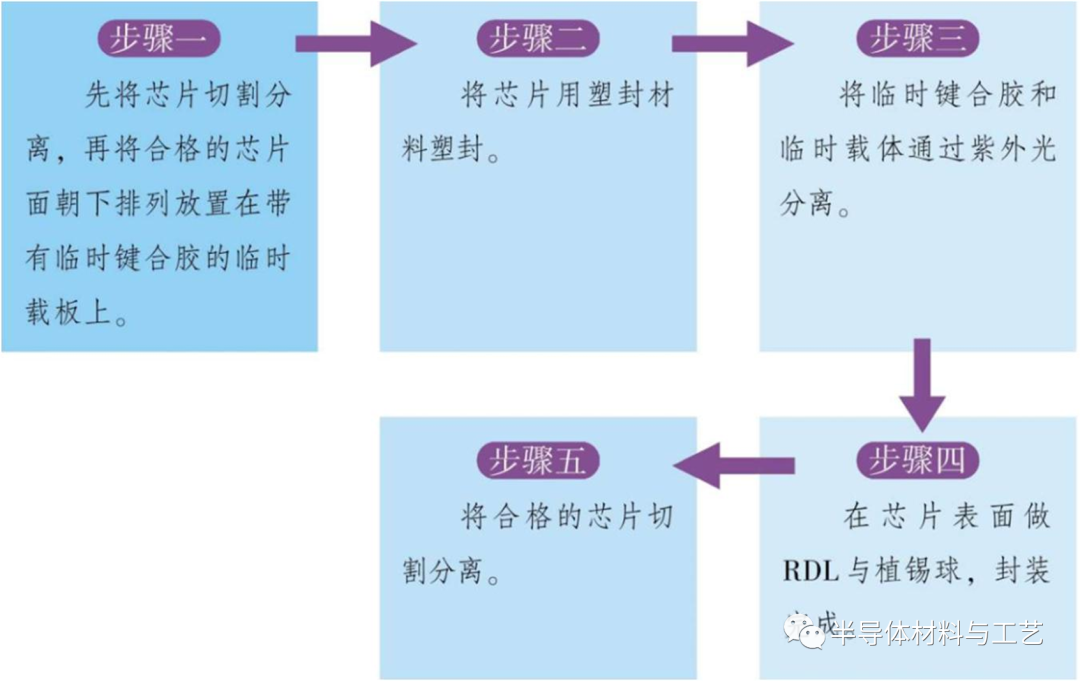

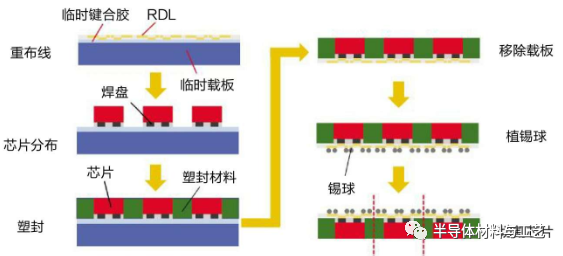

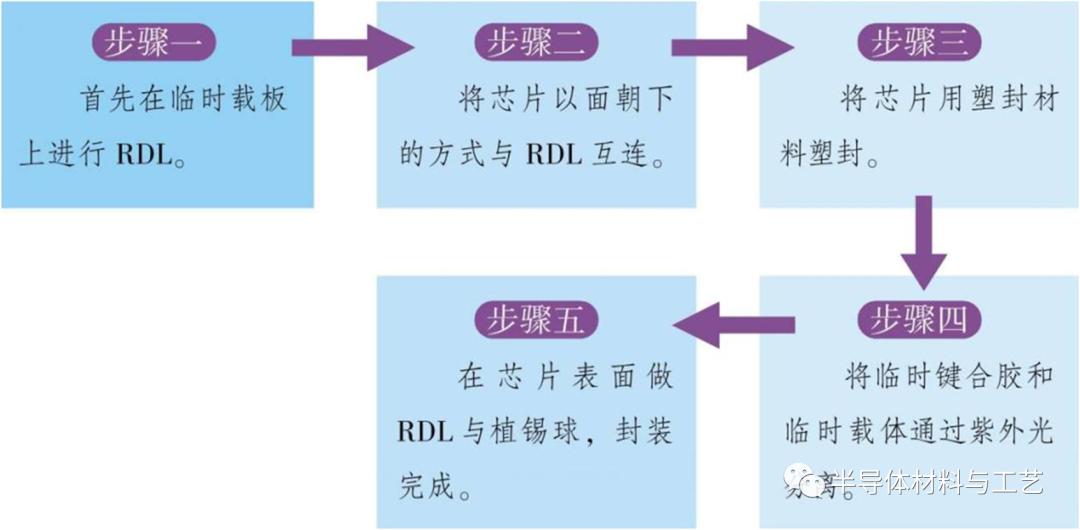

19 当的方式为激光解键合。鸿浩半导体设备所生产的UV激光解键合设备具备低温、不伤晶圆等技术特点,并且提供合理的制程成本,十分适合应用于扇出晶圆级封装。 01 扇出晶圆级封装简介 扇出晶圆级封装(Fan Out Wafer Level Packaging, FOWLP,简称扇出

2023-04-28 17:44:43 972

972

电子发烧友App

电子发烧友App

评论