***是生产芯片最核心的设备,技术难度非常高。目前全球90%以上的***市场都被荷兰、日本占据为什么这个领域这么难做?本篇将从光刻技术和***两大部分来共同探索,一束光的旅程究竟有多复杂?

光刻技术

成就摩尔定律的追光之旅

光刻技术,简单来说就是利用光化学反应原理,在特定波长光线的作用下,把想要的图形刻蚀到到晶圆上的过程,因此也叫光刻蚀工艺。它的思想来源于历史悠久的印刷技术,不同的是,制造芯片所使用的光刻技术使用的是光而不是墨水。

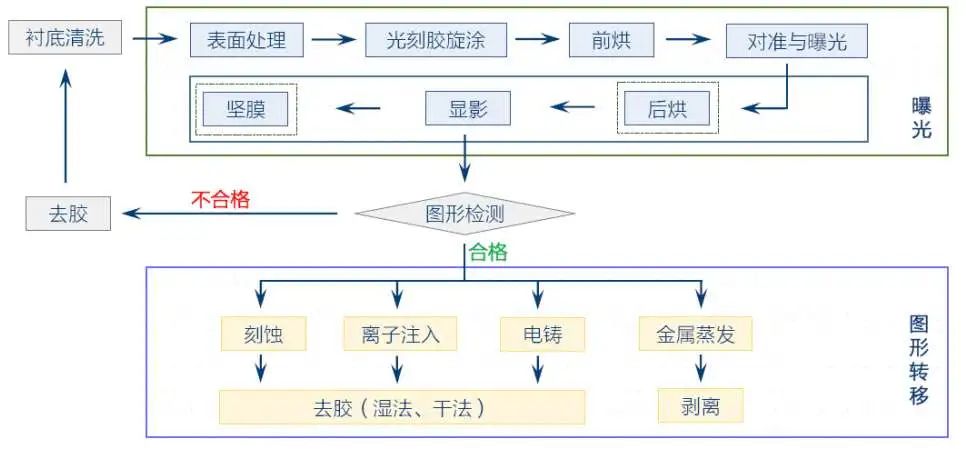

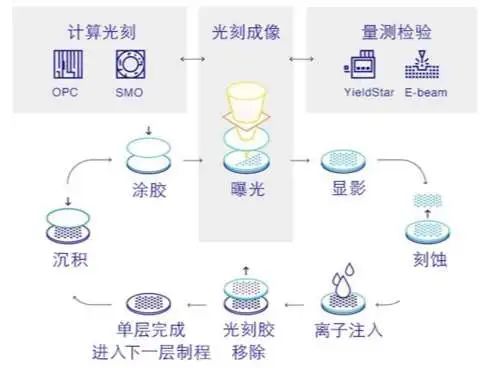

▲光刻工艺的基本步骤

光刻技术的核心其实是围绕两个定律

摩尔定律

由英特尔的创始人之一戈登·摩尔提出。芯片的基本元件是晶体管,晶体管越多,芯片的运算速度越快。摩尔定律是指,每隔两年,同样大小的芯片里面的晶体管的数量就会增加一倍,性能也增加一倍。

这就要求芯片内部制造得越来越精细,如今先进工艺制程的两个起点之间只能有几纳米的距离了。(1nm约为头发丝直径的的五万分之一)

如此精细的产品,便需要用放大的思想来制造。传统的放大方法——杠杆等机械结构无法满足纳米级精度的“雕刻”。因此人们想到了用光来放大,原理类似我们常见的投影机。***的核心就是将光通过一个可以放大的透光的模子,照射到硅片上,从而印出想要的形状,也就是芯片的内部结构。

瑞利判据

Rayleigh Criterion

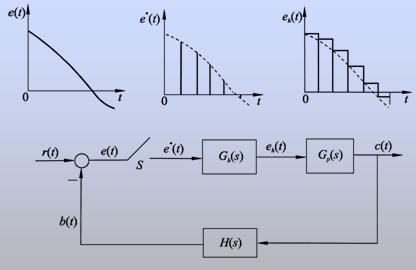

光刻技术对光源有着极为苛刻的要求。这就涉及到第二个原理——瑞利判据

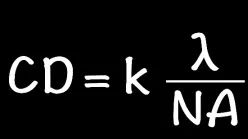

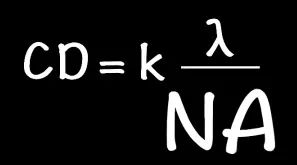

▲瑞利判据第一公式

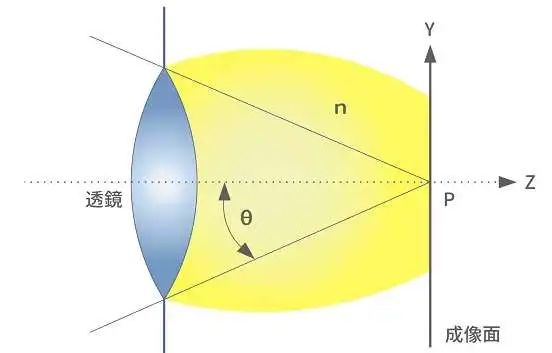

想要制造出更小的尺寸,就需要能分辨更小的尺寸。瑞利判据中,λ为光源波长、ΝΑ为数值孔径、k₁为光刻工艺系数,三者共同决定投影式***分辨率CD。

1

更短光源波长λ

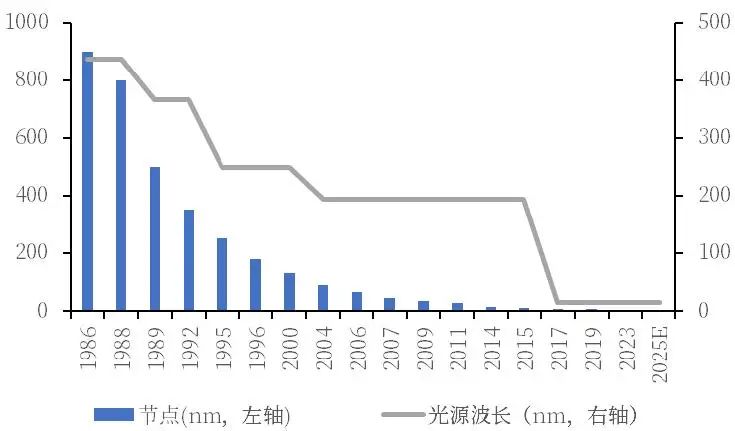

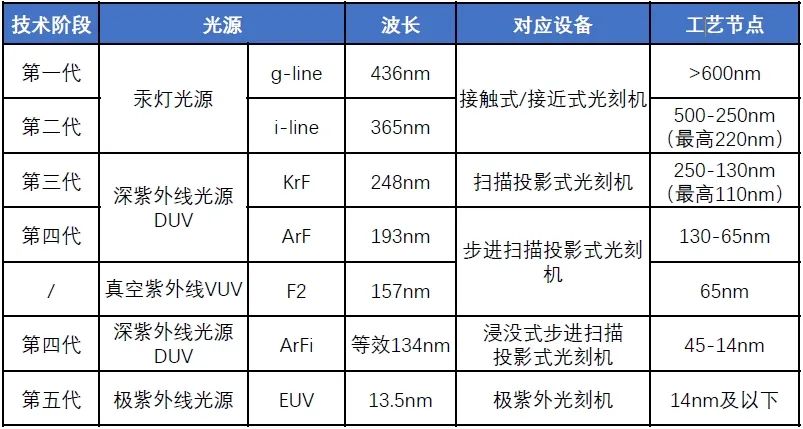

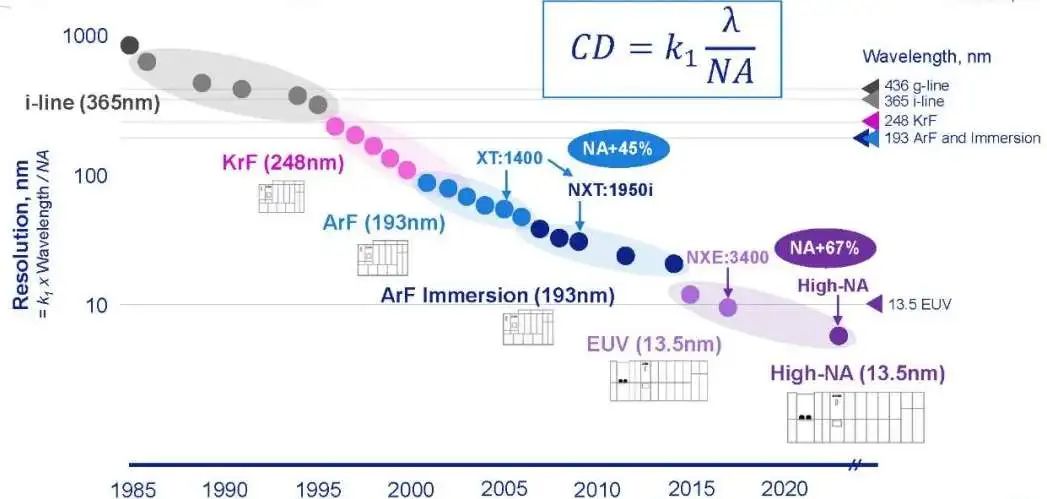

▲缩短光源波长

根据公式可以看出,***的分辨率与光源波长成正比,想要制造出更小的尺寸,就需要缩短光源的波长,这也是***世代演变的核心。***历经五代,波长从436nm缩小约30倍,达到13.5nm,对应节点从μm级升级到最先进的3nm,光源波长的缩短支撑了摩尔定律的发展。

▲芯片工艺节点与光源波长的关系

20世纪六七十年代,集成电路产业制造初期采用接触式光刻技术,以可见光作为光源;80年代广泛应用接近式光刻技术,并改用高压汞灯产生的紫外光(UV),g线和i线是紫外光中能量较高的谱线,365nm的i-line可将最高分辨率推动至220nm;80年代中期,IBM/Cymer等公司开始研发深紫外(DUV)准分子激光,最高分辨率降低至KrF(110nm)和ArF(65nm),采用ArF光源的第四代***是目前应用最广泛的一代。随着工艺节点发展到7nm及以下,20世纪初期产业联合研发第五代EUV***,使用13.5nm的极紫外光,比DUV短14倍以上。

▲光刻光源世代演变

2

增大NA:物镜直径↑+浸没式光刻

▲提高数值孔径NA

光源演进到ArF(193nm)时,下一代光源推进速度放缓,巨头们开始将目光转向提高数值孔径NA,并出现了F2(光源演进)与ArF+immersion(增大NA)的路线之争。

物镜的数值孔径NA= n*sinθ,其中 n 为介质折射率, θ 为镜头聚焦至成像面的角度。

▲光线通过透镜系统聚焦成像

增大NA的两个方法:

1)增加投影物镜的 0.55NA突破。

▲工艺节点与光源波长及NA的关系

3

缩小k₁:突破物理极限

光照条件的设置、掩模版设计以及光刻胶工艺等因素对分辨率的影响都反映在k₁因子中,k₁因子也常被用于评估光刻工艺的难度,ASML认为其物理极限在0.25,k₁体现了各家晶圆厂运用光刻技术的水平。

分辨率增强技术(RET)是指对掩模和光照系统做改进,实现最大共同工艺窗口,从而提高分辨率。常见方法包括离轴照明、光学邻近校正、移相掩模、添加亚分辨率辅助图等,通过改变掩模的振幅(OPC法)或相位(PSM法),调整光源入射角度(OAI法)等提高分辨率、增加焦深、改善图形质量,此外也可以用多重曝光技术实现超越***理论分辨率的精度。

▲部分典型的分辨率增强技术

4

瑞利第二公式DoF = k₂λ/NA²

焦深DoF限制了NA的无限扩大。焦深是指硅片沿光路移动时,能保持曝光成像质量的距离,焦深越大层间误差越小。随着光源波长逼近极限,目前降低分辨率的主要方法为增大数值孔径,但需要和DoF折中考虑。

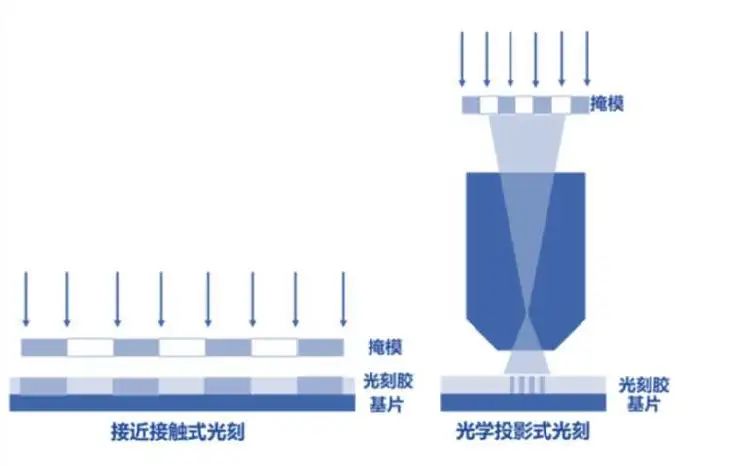

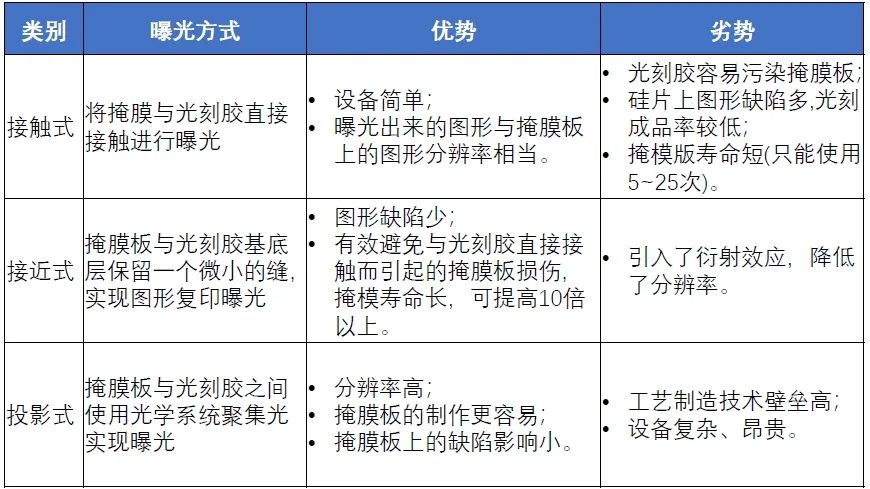

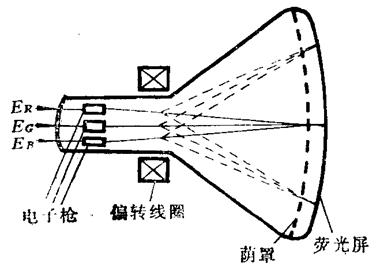

在瑞利公式的指导下,人类在缩短波长λ,增大数值孔径NA,降低工艺因子k₁三个方面不断探索和突破极限。为实现进一步的制程微缩,业界又在曝光工艺方面极尽智慧。初代***采用接触式或接近式,无法兼顾掩模版寿命与分辨率。1973年,美国Perkin Elmer率先推出第一台投影式***,投影式***既能避免污染又能实现倍缩,迅速替代传统接近接触式,成为市场主流。

▲不同曝光技术示意图

▲三类曝光方式的优劣对比

5

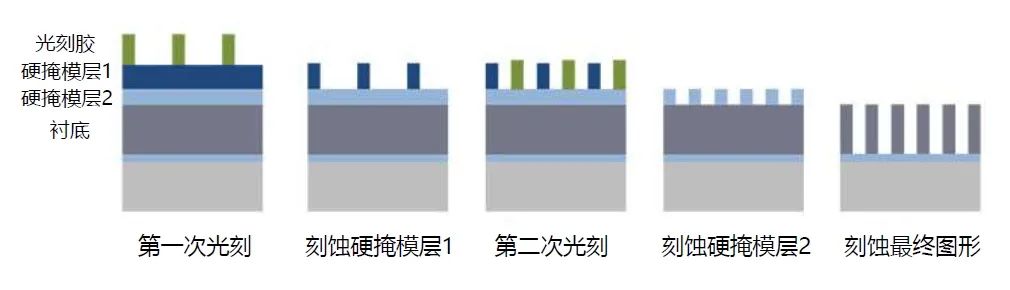

“多重曝光”

实现制程微缩的另一个重要手段是“多重曝光”,即将原本一层光刻的图形拆分到多个掩模上,利用光刻Litho和刻蚀Etch实现更小制程。常见的技术有双重曝光(DE)、固化双重曝光(LFLE)、双重光刻(LELE)、三重光刻(LELELE)、自对准双重成像(SADP)、连续两次SADP(SAQP)等。

▲LELE双重光刻工艺示意图

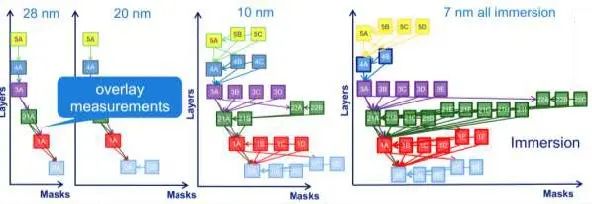

需要注意的是,尽管多重曝光可以做成更先进的制程,当制程微缩至10nm及以下时,浸没式DUV多重曝光的工艺复杂度急剧上升。

比如,多次LE或SADP可以实现7nm制程,但多重曝光技术提高了对刻蚀、沉积等工艺的技术要求并且增加了使用次数,使晶圆光刻成本增加了2-3倍。

此时,相较多重曝光,EUV能降低15%-50%的成本,缩短3-6x的周期时间,使产品更快量产。而对于5nm制程,浸没式DUV难以实现且不具备经济效益。

▲不同节点采用浸没式DUV进行多重曝光的工艺复杂度

***

Mask

Aligner

挑战全人类文明的极限

上一部分我们了解到光刻技术的核心原理和实现手段,想要进行光刻就得上机器了。***的技术水平很大程度上决定了集成电路的发展水平。先进制程芯片(14nm以下)需要进行20-30次光刻,光刻工艺的耗时可以占到整个晶圆制造时间的40%-50%,费用约占芯片生产成本的1/3。

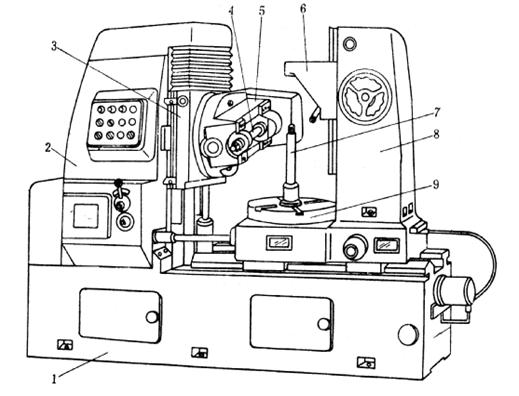

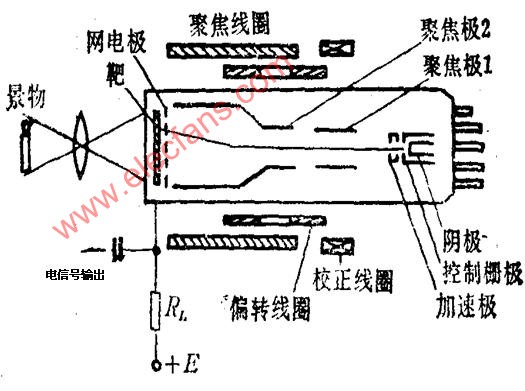

荷兰最新一代EUV***造价1.5亿美元,约合人民币近10亿,整个机器包含10万个部件和2公里长的电缆,有公共汽车大小,重达200吨左右。国内上海微电子90nm的干法DUV***,包括13个分系统,3万个机械件,200多个传感器。

如此庞然大物内部构造是怎样的呢?

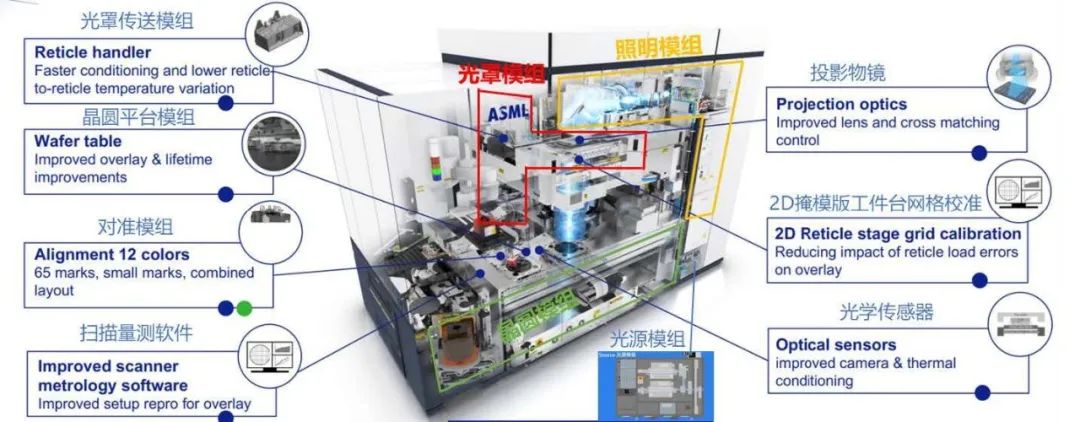

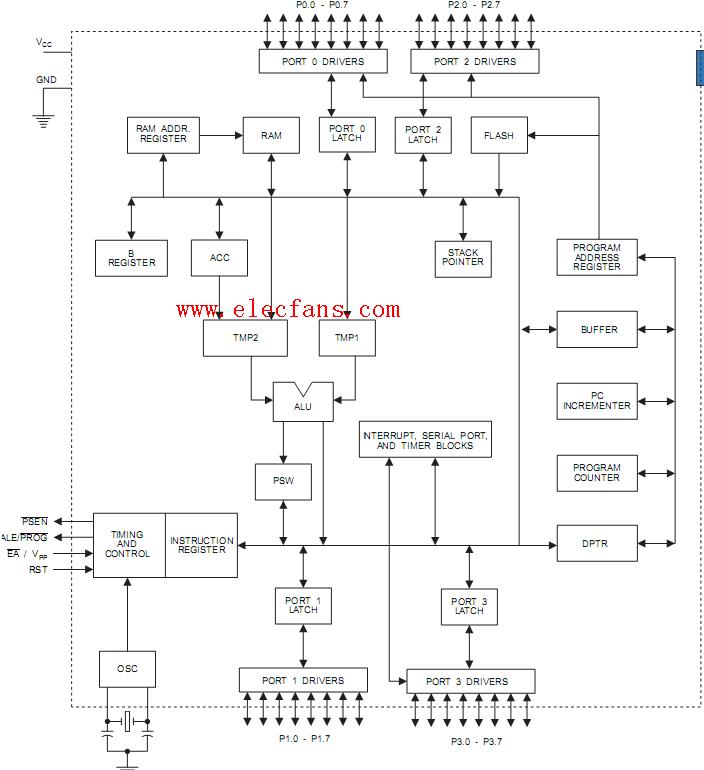

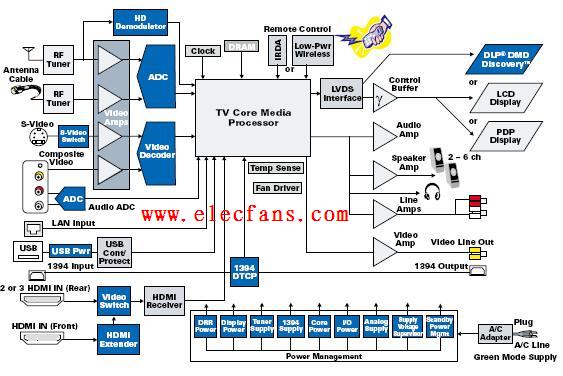

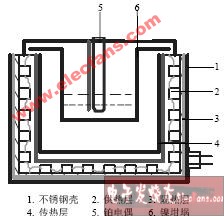

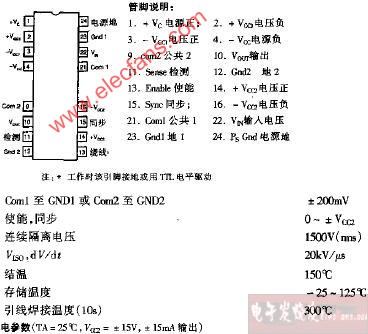

整台***主要包括光源系统、照明系统、投影物镜系统、双工件台系统、以及传输系统(光罩+晶圆)、调平调焦系统、对准系统等;同时需要极严苛的环境控制、整机控制以及整机软件分析系统。***性能的三大评价指标是分辨率(CD)、套刻精度(overlay)、和产率(throughput,wph)。可以说***的每一部分都在挑战人类工程的极限。

▲***的整体结构图

※

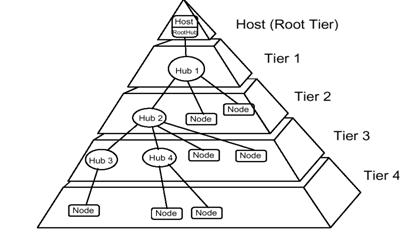

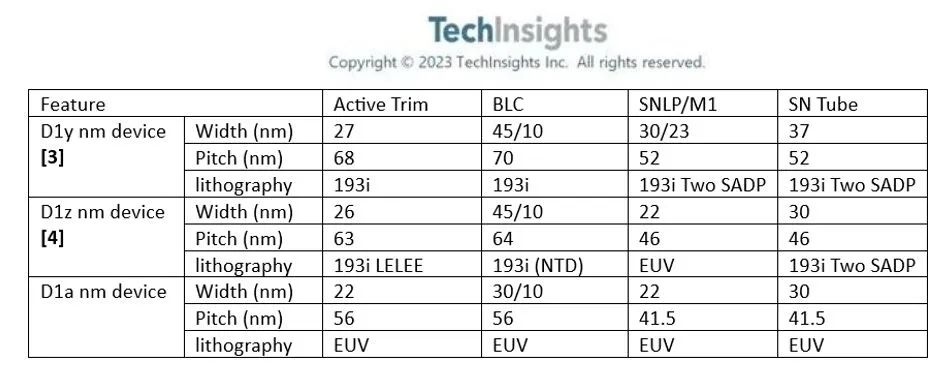

***的演进主要分为以下几个阶段

1)UV***:用于0.25微米及以上制程节点,UV为紫外光,光源类型包括g-line、i-line等。

2)干式DUV***:可用于65nm-0.35μm制程节点,干式DUV是指在光刻过程中使用干式透镜和深紫外线光源,该技术在20世纪90年代初得到了广泛应用。

3)浸入式DUV***:可用于7nm-45nm制程节点,随着芯片制造技术对先进制程的需求持续增加,干式DUV***已无法满足其精度要求。浸入式DUV***通过把物镜与晶圆之间的填充由空气改变为水,进而获得更高的数值孔径(NA),使***具有更高的分辨率与成像能力。

4)Low-NAEUV***:用于3nm-7nm制程节点,EUV为极紫外光,该光源的波长较此前光源明显减小,显著提升***的分辨率。

5)High-NAEUV***:用于3nm以下制程节点,High-NA是指高数值孔径(0.33→0.55),是下一代***技术,将在已有EUV基础上进一步提高分辨率与成像能力,从而实现更先进制程的生产。当前该技术还在研发中。

▲***演进示意图

并且不是有***就“大功告成”,可以开始“印芯片”了,***更像是中间执行的环节,而在执行前后,还需要很多同样重要的工作,比如说计算光刻和量测。

计算光刻指的是利用各种物理,化学和数学模型去计算模拟真实光刻发生的过程和结果。通过修改各种参数,寻找最优的参数组合来修正掩膜板的图形和光源形状,来提升光刻的质量。这种模拟仿真的思路类似造飞机的时候需要经过很多次的风洞实验,都通过之后才能进行真正的试飞,否则既危险又成本高昂。计算光刻已经成为现代光刻技术研发的核心和最重要的环节之一。

▲集成电路制造主要流程

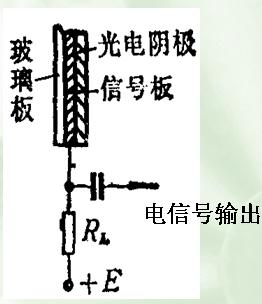

量测就是进行芯片的缺陷检测,判断芯片是否合格。一个晶圆的制作可能包含近百次的曝光,由于每次曝光的间隔都需要对晶圆进行移动调整,为了保证移动的稳定和精准,避免出现小至几纳米的误差导致芯片报废,就需要不断的对晶圆在纳米尺度做量测,并且实现校正和结果的反馈,从而不断的提升良率。

量测主要有两种方法:基于衍射的光学量测和电子束量测。其中基于衍射的光学量测用来评估晶圆电路图案的质量,而电子数量测则是用来定位和分析单个芯片的缺陷。在一个光刻系统中,这两种量测的方法通常是同时使用。

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论