在本文中,我们将重点介绍半导体封装的另一种主要方法——晶圆级封装(WLP)。本文将探讨晶圆级封装的五项基本工艺,包括:光刻(Photolithography)工艺、溅射(Sputtering)工艺、电镀(Electroplating)工艺、光刻胶去胶(PR Stripping)工艺和金属刻蚀(Metal Etching)工艺。

封装完整晶圆

晶圆级封装是指晶圆切割前的工艺。晶圆级封装分为扇入型晶圆级芯片封装(Fan-In WLCSP)和扇出型晶圆级芯片封装(Fan-Out WLCSP),其特点是在整个封装过程中,晶圆始终保持完整。除此之外,重新分配层(RDL)封装、倒片(Flip Chip)封装及硅通孔(TSV)封装通常也被归类为晶圆级封装,尽管这些封装方法在晶圆切割前仅完成了部分工序。不同封装方法所使用的金属及电镀(Electroplating)绘制图案也均不相同。不过,在封装过程中,这几种方法基本都遵循如下顺序。

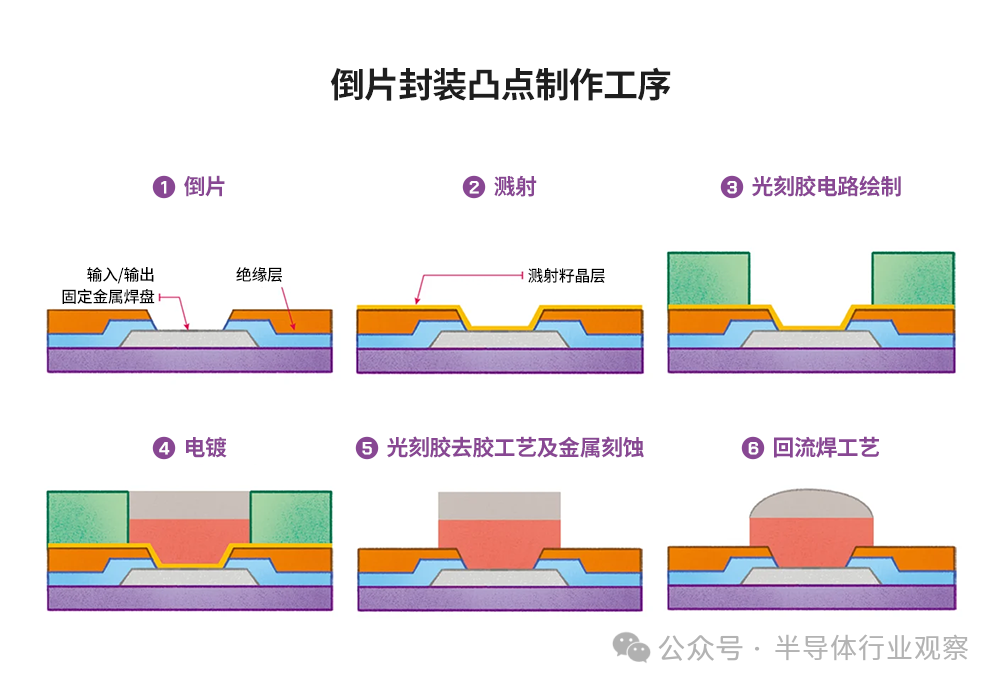

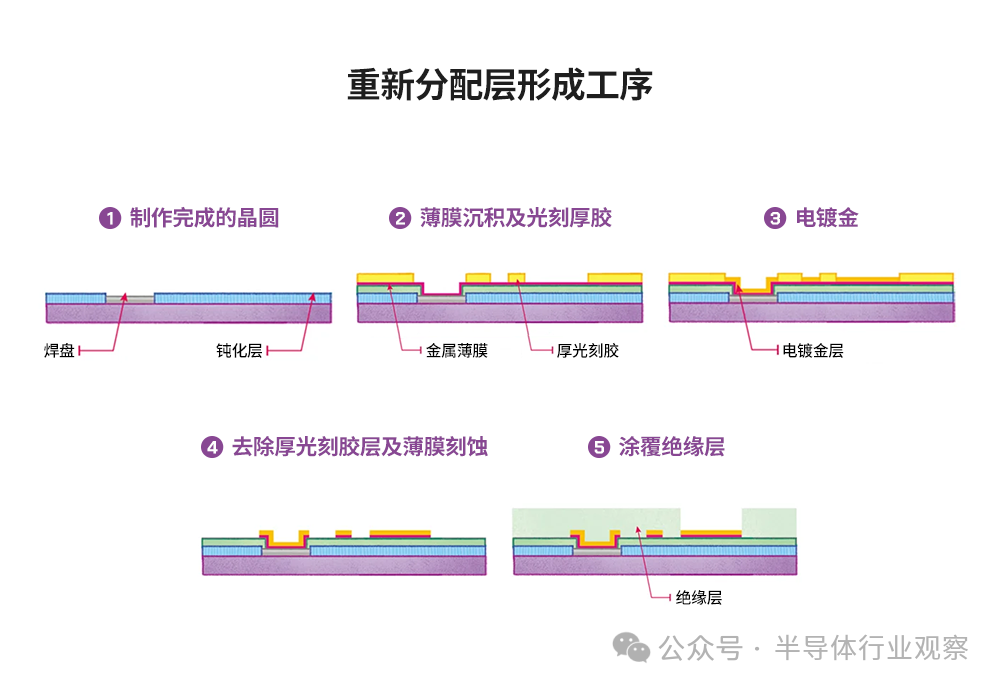

完成晶圆测试后,根据需求在晶圆上制作绝缘层(Dielectric Layer)。初次曝光后,绝缘层通过光刻技术再次对芯片焊盘进行曝光。然后,通过溅射(Sputtering)工艺在晶圆表面涂覆金属层。此金属层可增强在后续步骤中形成的电镀金属层的黏附力,同时还可作为扩散阻挡层以防止金属内部发生化学反应。此外,金属层还可在电镀过程中充当电子通道。之后涂覆光刻胶(Photoresist)以形成电镀层,并通过光刻工艺绘制图案,再利用电镀形成一层厚的金属层。电镀完成后,进行光刻胶去胶工艺,采用刻蚀工艺去除剩余的薄金属层。最后,电镀金属层就在晶圆表面制作完成了所需图案。这些图案可充当扇入型WLCSP的引线、重新分配层封装中的焊盘再分布,以及倒片封装中的凸点。下文将对每道工序进行详细介绍。

光刻工艺:在掩模晶圆上绘制电路图案

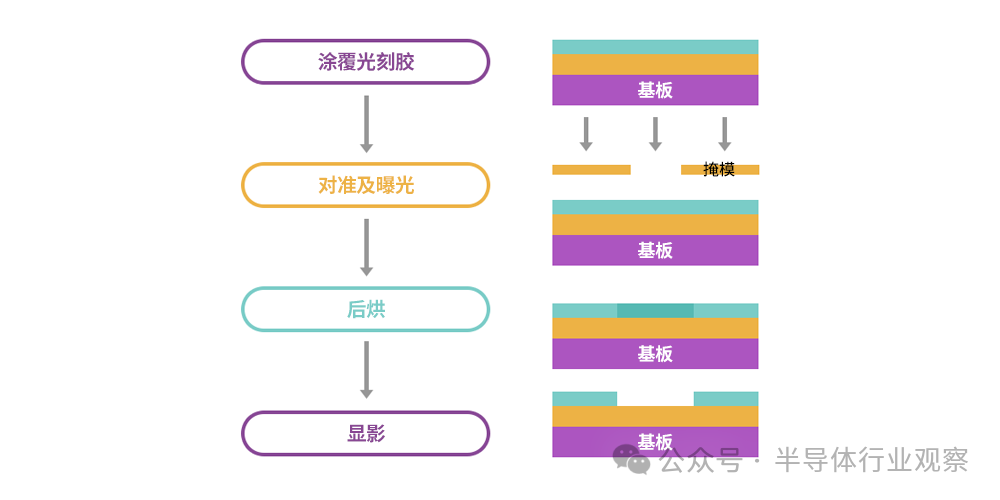

光刻对应的英文是Photolithography,由“-litho(石刻)”和“graphy(绘图)”组成,是一种印刷技术,换句话说,光刻是一种电路图案绘制工艺。首先在晶圆上涂覆一层被称为“光刻胶”的光敏聚合物,然后透过刻有所需图案的掩模,选择性地对晶圆进行曝光,对曝光区域进行显影,以绘制所需的图案或图形。该工艺的步骤如图2所示。

在晶圆级封装中,光刻工艺主要用于在绝缘层上绘制图案,进而使用绘制图案来创建电镀层,并通过刻蚀扩散层来形成金属线路。

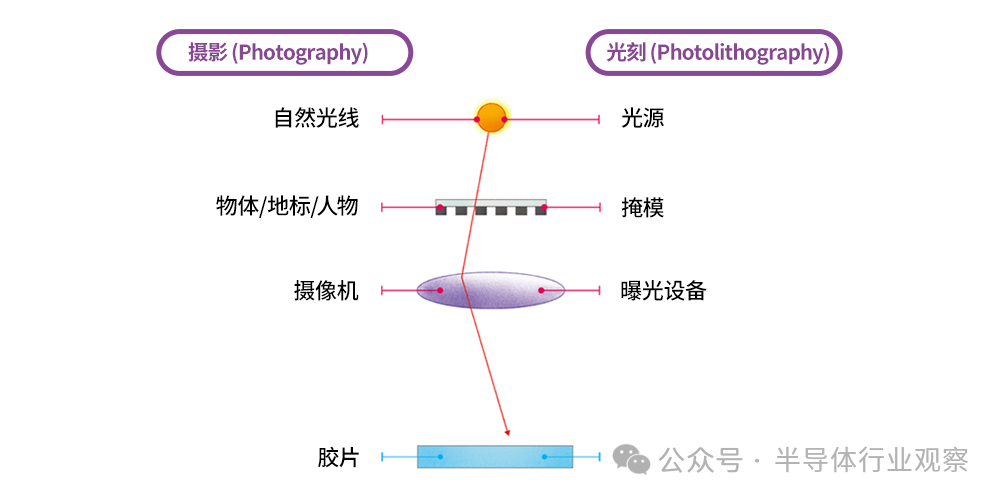

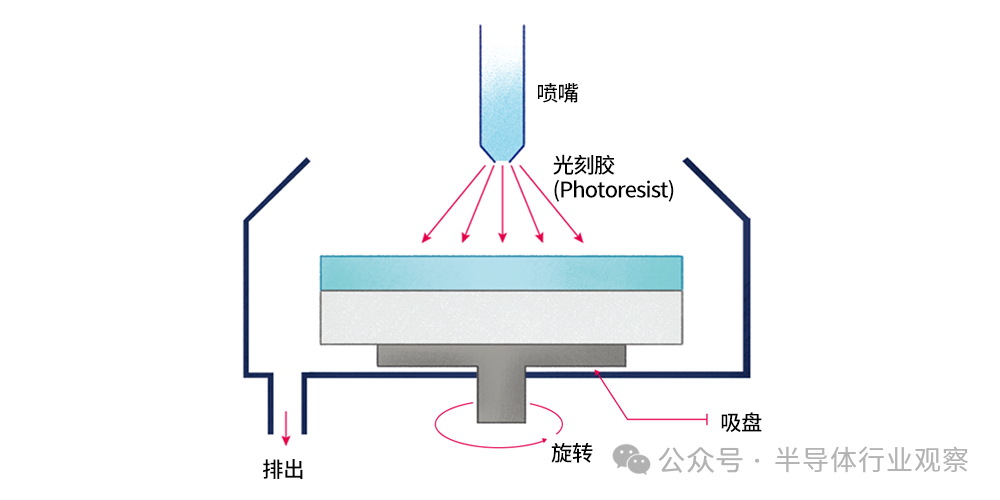

为更加清楚地了解光刻工艺,不妨将其与摄影技术进行比较。如图3所示,摄影以太阳光作为光源来捕捉拍摄对象,对象可以是物体、地标或人物。而光刻则需要特定光源将掩模上的图案转移到曝光设备上。另外,摄像机中的胶片也可类比为光刻工艺中涂覆在晶圆上的光刻胶。如图4所示,我们可以通过三种方法将光刻胶涂覆在晶圆上,包括旋涂(Spin Coating)、薄膜层压(Film Lamination)和喷涂(Spray Coating)。涂覆光刻胶后,需用通过前烘(Soft Baking)来去除溶剂,以确保粘性光刻胶保留在晶圆上且维持其原本厚度。

如图5所示,旋涂将粘性光刻胶涂覆在旋转着的晶圆中心,离心力会使光刻胶向晶圆边缘扩散,从而以均匀的厚度分散在晶圆上。粘度越高转速越低,光刻胶就越厚。反之,粘度越低转速越高,光刻胶就越薄。对于晶圆级封装而言,特别是倒片封装,光刻胶层的厚度须达到30 μm至100 μm,才能形成焊接凸点。然而,通过单次旋涂很难达到所需厚度。在某些情况下,需要反复旋涂光刻胶并多次进行前烘。因此,在所需光刻胶层较厚的情况下,使用层压方法更加有效,因为这种方法从初始阶段就能够使光刻胶薄膜达到所需厚度,同时在处理过程中不会造成晶圆浪费,因此成本效益也更高。但是,如果晶圆结构表面粗糙,则很难将光刻胶膜附着在晶圆表面,此种情况下使用层压方法,会导致产品缺陷。所以,针对表面非常粗糙的晶圆,可通过喷涂方法,使光刻胶厚度保持均匀。

完成光刻胶涂覆和前烘后,接下来就需要进行曝光。通过照射,将掩模上的图案投射到晶圆表面的光刻胶上。由于正性光刻胶(Positive PR)在曝光后会软化,因此使用正性光刻胶时,需在掩模去除区开孔。负性光刻胶(Negative PR)在曝光后则会硬化,所以需在掩模保留区开孔。晶圆级封装通常采用掩模对准曝光机(Mask Aligner)或步进式***(Stepper)作为光刻工艺设备。

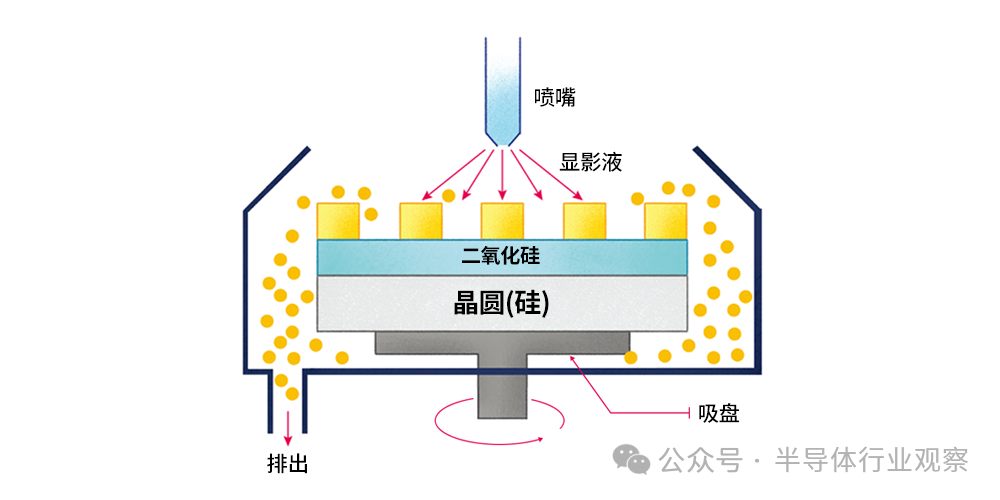

显影(Development)是一种利用显影液来溶解因光刻工艺而软化的光刻胶的工艺。如图6所示,显影方法可分为三种,包括:水坑式 显影(Puddle Development),将显影液倒入晶圆中心,并进行低速旋转;浸没式显影(Tank Development),将多个晶圆同时浸入显影液中;喷淋式显影(Spray Development),将显影液喷洒到晶圆上。图7显示了静态显影方法的工作原理。完成静态显影后,通过光刻技术使光刻胶形成所需的电路图案。

溅射工艺:在晶圆表面形成薄膜

溅射是一种在晶圆表面形成金属薄膜的物理气相沉积(PVD)工艺。如果晶圆上形成的金属薄膜低于倒片封装中的凸点,则被称为凸点下金属层(UBM,Under Bump Metallurgy)。通常凸点下金属层由两层或三层金属薄膜组成,包括:增强晶圆粘合性的黏附层;可在电镀过程中提供电子的载流层;以及具有焊料润湿性(Wettability),并可阻止镀层和金属之间形成化合物的扩散阻挡层。例如薄膜由钛、铜和镍组成,则钛层作为黏附层,铜层作为载流层,镍层作为阻挡层。因此,UBM对确保倒片封装的质量及可靠性十分重要。在RDL和WLCSP等封装工艺中,金属层的作用主要是形成金属引线,因此通常由可提高粘性的黏附层及载流层构成。

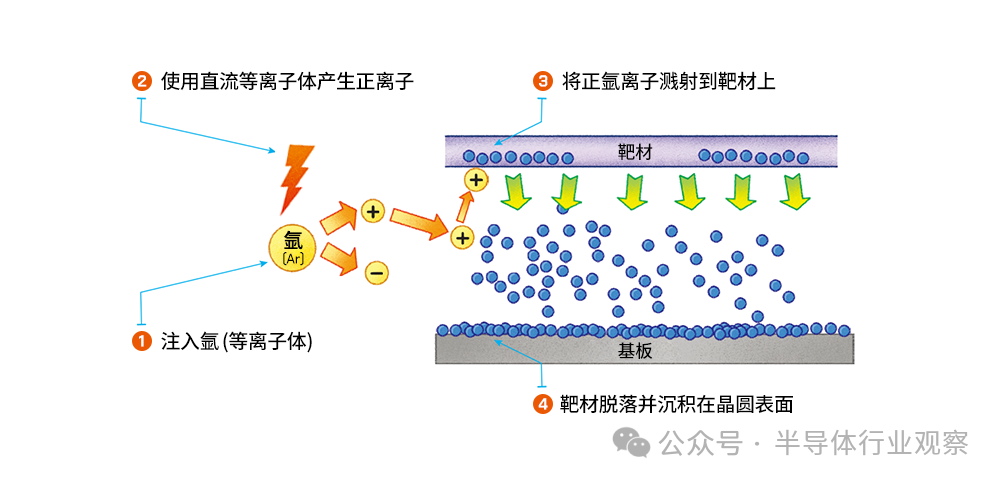

如图8所示,在溅射工艺中,首先将氩气转化为等离子体(Plasma),然后利用离子束碰击靶材(Target),靶材的成分与沉积正氩离子的金属成分相同。碰击后,靶材上的金属颗粒会脱落并沉积在晶圆表面。通过溅射,沉积的金属颗粒具有一致的方向性。尽管晶圆平坦区经过沉积后厚度均匀,但沟槽或垂直互连通路(通孔)的沉积厚度可能存在差异,因此就沉积厚度而言,此类不规则形状会导致平行于金属沉积方向的基板表面的沉积厚度,比垂直于金属沉积方向的基板表面沉积厚度薄。

电镀工艺:形成用于键合的金属层

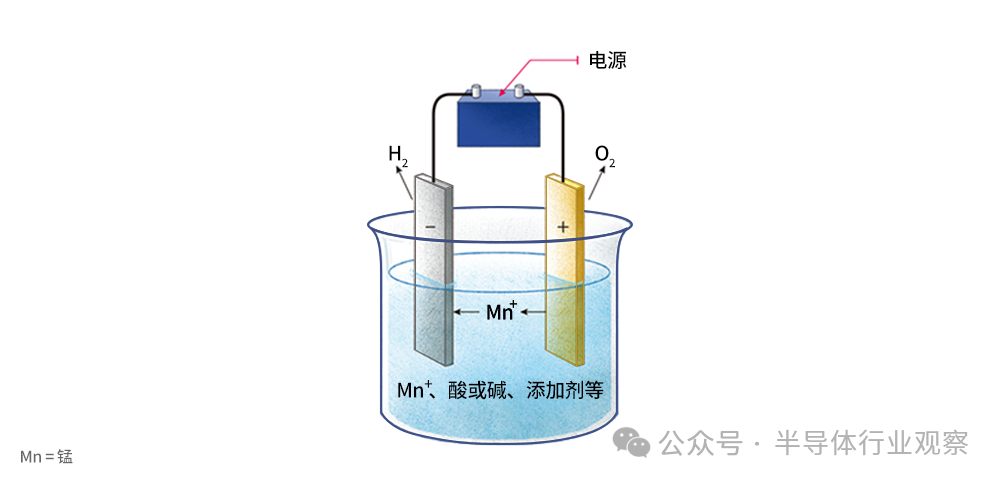

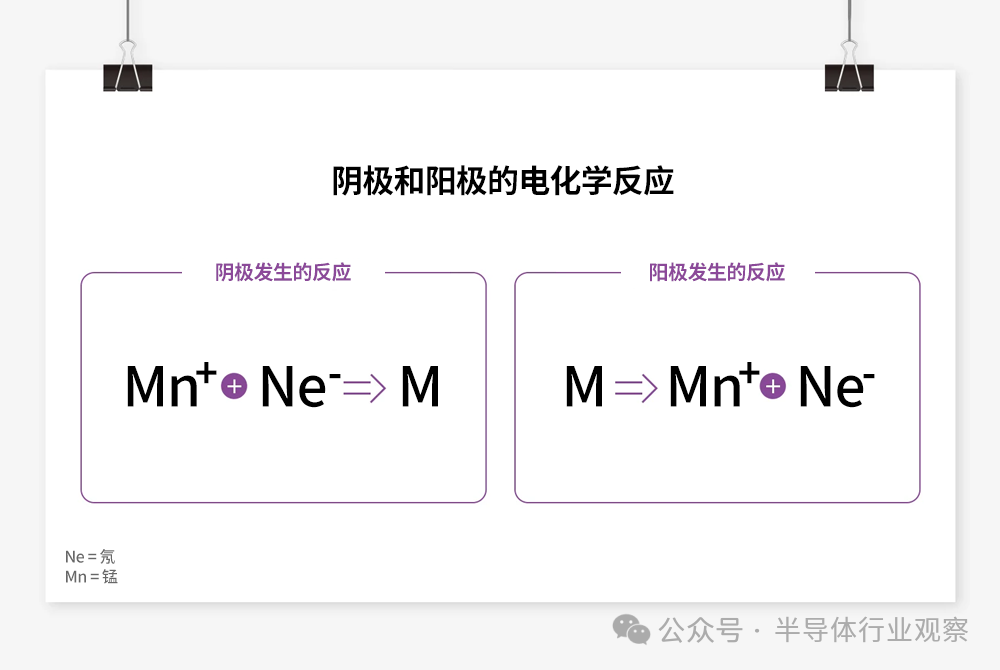

电镀是将电解质溶液中的金属离子还原为金属并沉积在晶圆表面的过程,此过程是需要通过外部提供的电子进行还原反应来实现的。在晶圆级封装中,采用电镀工艺形成厚金属层。厚金属层可充当实现电气连接的金属引线,或是焊接处的凸点。如图9所示,阳极上的金属会被氧化成离子,并向外部电路释放电子。在阳极处被氧化的及存在于溶液中的金属离子可接收电子,在经过还原反应后成为金属。在晶圆级封装的电镀工艺中,阴极为晶圆。阳极由作为电镀层的金属制成,但也可使用如铂金的不溶性电极(Insoluble Electrode)。如果阳极板由作为镀层的金属制成,金属离子就会从阳极板上溶解并持续扩散,以保持溶液中离子浓度的一致性。如果使用不溶性电极,则必须定期补充溶液中因沉积到晶圆表面而消耗的金属离子,以维持金属离子浓度。图10展示了阴极和阳极分别发生的电化学反应。

在放置晶圆电镀设备时,通常需确保晶圆的待镀面朝下,同时将阳极置于电解质溶液中。当电解质溶液流向晶圆并与晶圆表面发生强力碰撞时,就会发生电镀。此时,由光刻胶形成的电路图案会与待镀晶圆上的电解质溶液接触。电子分布在晶圆边缘的电镀设备上,最终电解质溶液中的金属离子与光刻胶在晶圆上绘制的图案相遇。随后,电子与电解质溶液中的金属离子结合,在光刻胶绘制图案的地方进行还原反应,形成金属引线或凸点。

光刻胶去胶工艺和金属刻蚀工艺:去除光刻胶

在所有使用光刻胶图案的工艺步骤完成后,必须通过光刻胶去胶工艺来清除光刻胶。光刻胶去胶工艺是一种湿法工艺,采用一种被称为剥离液(Stripper)的化学溶液,通过水坑式、浸没式,或喷淋式等方法来实现。通过电镀工艺形成金属引线或凸点后,需清除因溅射形成的金属薄膜。这是非常必要的一个步骤,因为如果不去除金属薄膜,整个晶圆都将被电气连接从而导致短路。可采用湿刻蚀(Wet Etching)工艺去除金属薄膜,以酸性刻蚀剂(Etchant)溶解金属。这种工艺类似于光刻胶去胶工艺,随着晶圆上的电路图案变得越来越精细,水坑式方法也得到了更广泛的应用。

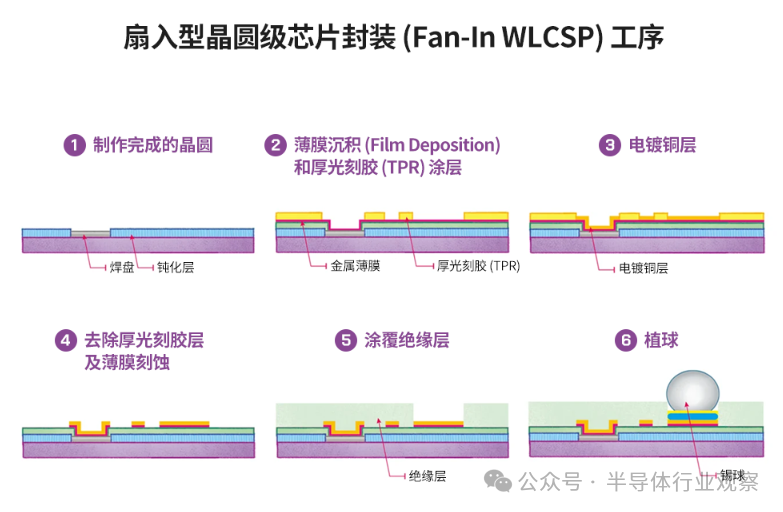

扇入型晶圆级芯片封装工艺

在扇入型晶圆级芯片封装中,合格晶圆首先将进入封装生产线。通过溅射工艺在晶圆表面制备一层金属膜,并在金属膜上涂覆一层较厚的光刻胶,光刻胶厚度需超过用于封装的金属引线。通过光刻工艺在光刻胶上绘制电路图案,再利用铜电镀工艺在曝光区域形成金属引线。随后去除光刻胶,并利用化学刻蚀(Chemical Etching)工艺去除多余的薄金属膜,然后在晶圆表面制备绝缘层(Dielectric Layer),并利用光刻工艺去除锡球(Solder Ball)放置区域的绝缘层。因此,绝缘层也被称为“阻焊层”(Solder Resist),它是晶圆级芯片封装中的钝化层(Passivation Layer),即最后的保护层,用于区分锡球放置区域。如没有钝化层,采用回流焊(Reflow Soldering)等工艺时,附着在金属层上的锡球会持续融化,无法保持球状。

利用光刻工艺在绝缘层上绘制电路图案后,再通过植球工艺使锡球附着于绝缘层。植球安装完成后,封装流程也随之结束。对封装完成的整片晶圆进行切割后,即可获得多个独立的扇入型晶圆级芯片封装体。

在植球过程中,需要将锡球附着到晶圆级芯片封装体上。传统封装工艺与晶圆级封装工艺的关键区别在于,前者将锡球放置在基板上,而后者将锡球放置在晶圆顶部。因此,除了用于涂敷助焊剂和植球的模板需在尺寸上与晶圆保持一致之外,助焊剂涂敷、植球工艺、回流焊工艺都遵循相同步骤。

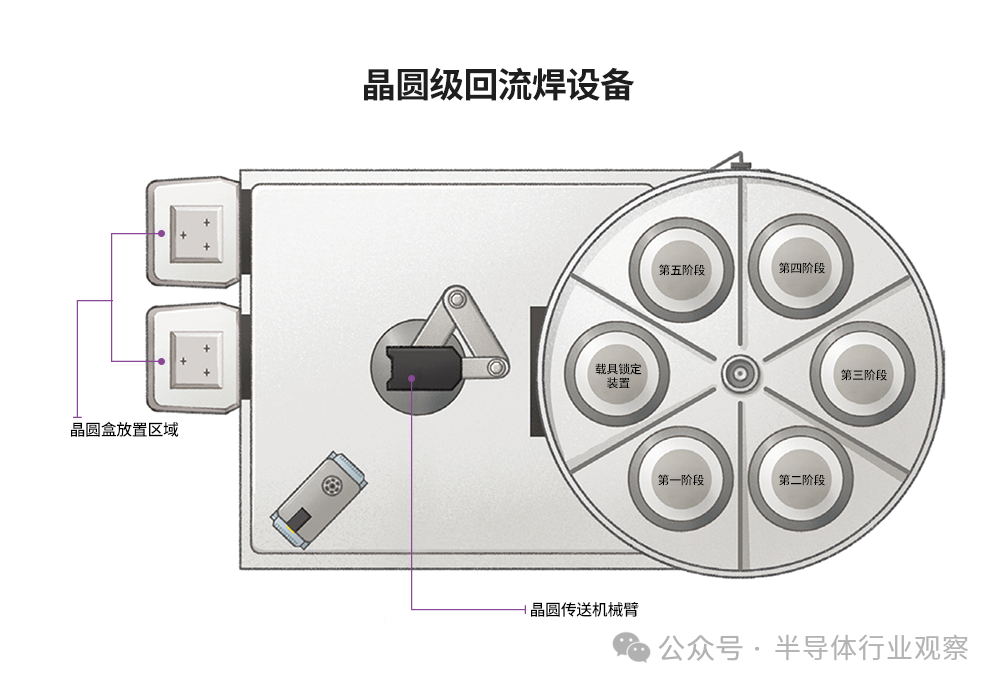

此外,回流焊设备采用基于发热板的回流焊方式,如图所示,而不是涉及运送器的对流热风回流焊方式(Convection Reflow)。晶圆级回流焊设备在不同的加工阶段会对晶圆施加不同温度,以便保持回流焊操作所需温度条件,确保封装工艺流程能够顺利进行。

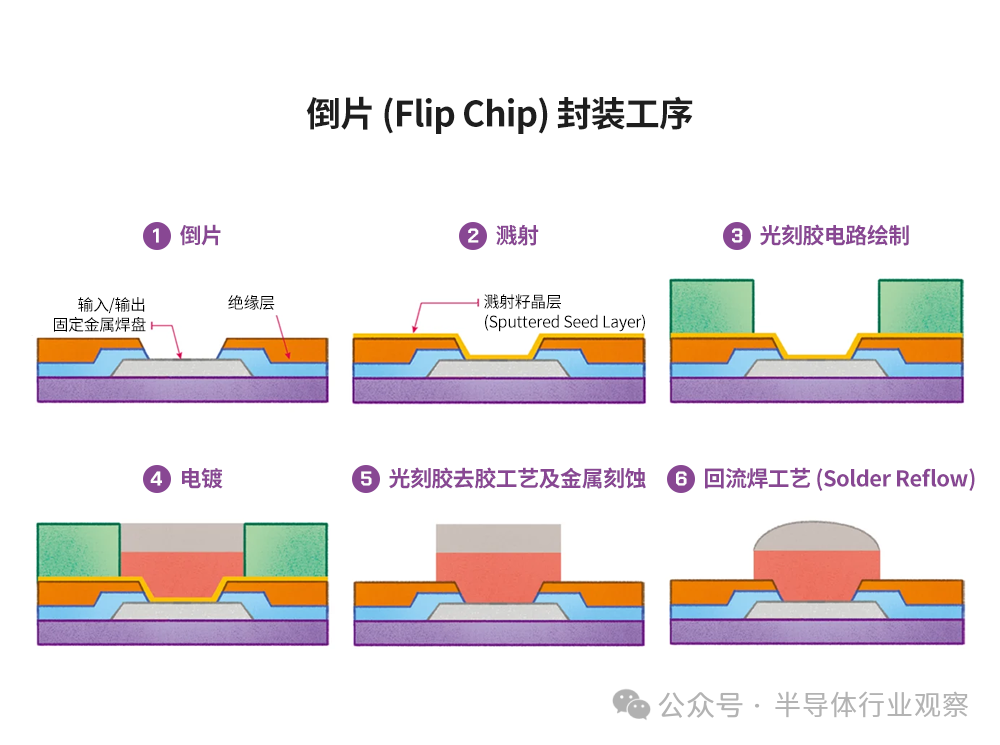

倒片封装凸点工艺

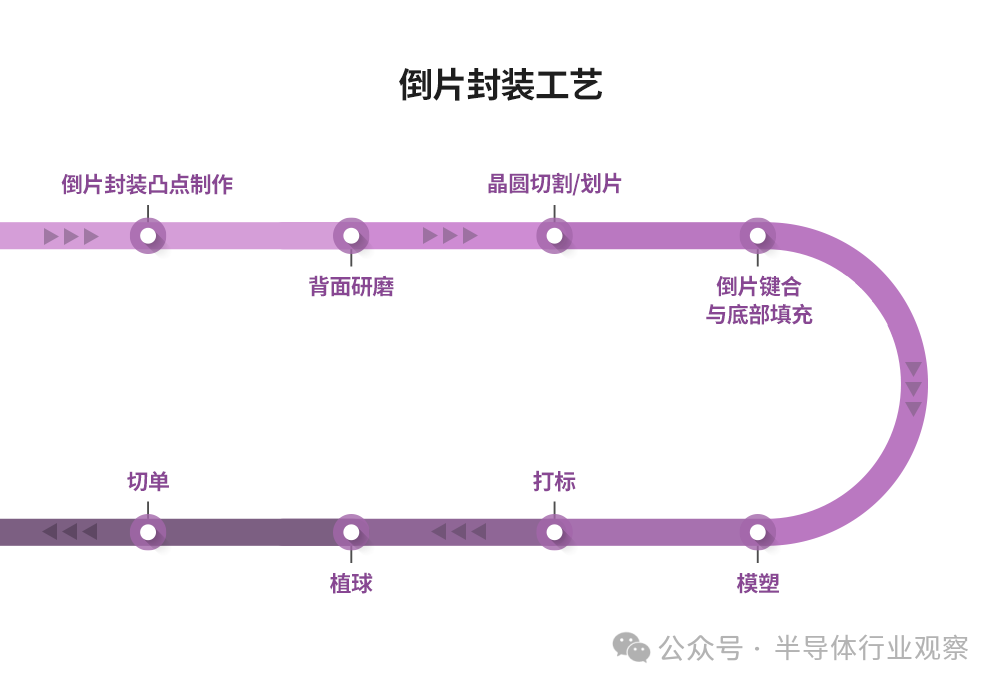

倒片封装体中凸点(Bump)是基于晶圆级工艺而完成的,而后续工序则与传统封装工艺相同。

由于要确保凸点拥有足够的高度,因此需选用能在晶圆上厚涂的光刻胶。铜柱凸块(CPB)需要先后经历铜电镀和焊料电镀两道工序后形成,所使用的焊料通常为不含铅的锡银合金。电镀完成后,光刻胶随即被去除,并采用金属刻蚀工艺去除溅射而成的凸点下金属层(UBM),随后通过晶圆级回流焊设备将这些凸点制成球形。这里采用的焊接凸点回流焊工艺可以最大限度减少各凸点的高度差,降低焊接凸点表面的粗糙度,同时去除焊料中自带的氧化物,进而保障在倒片键合过程中增加键合强度。

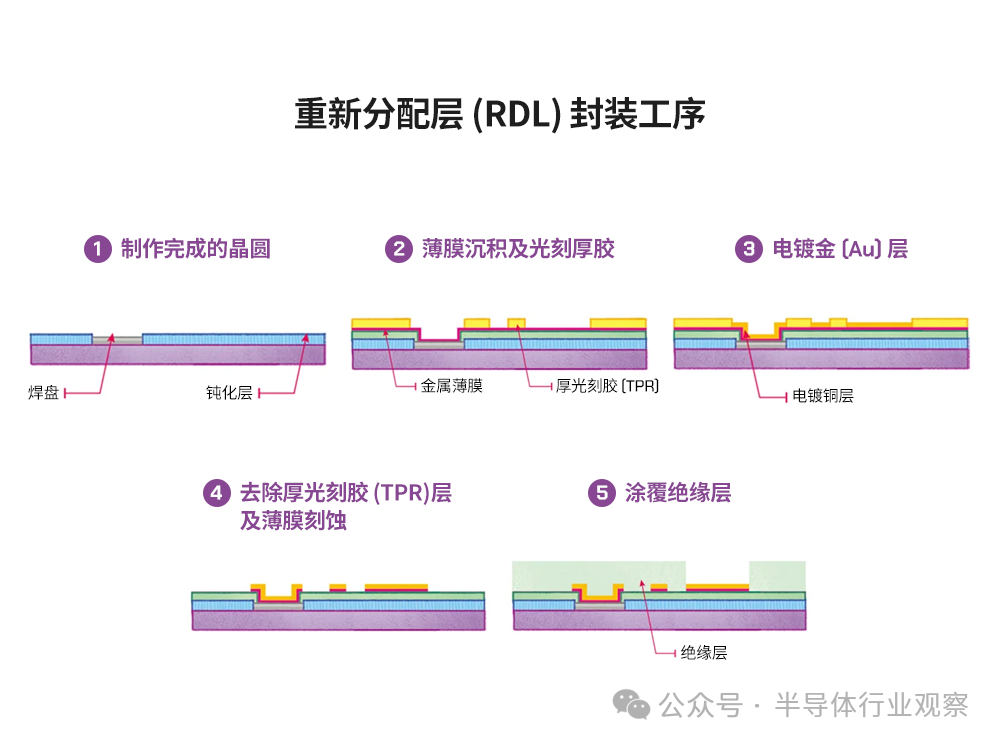

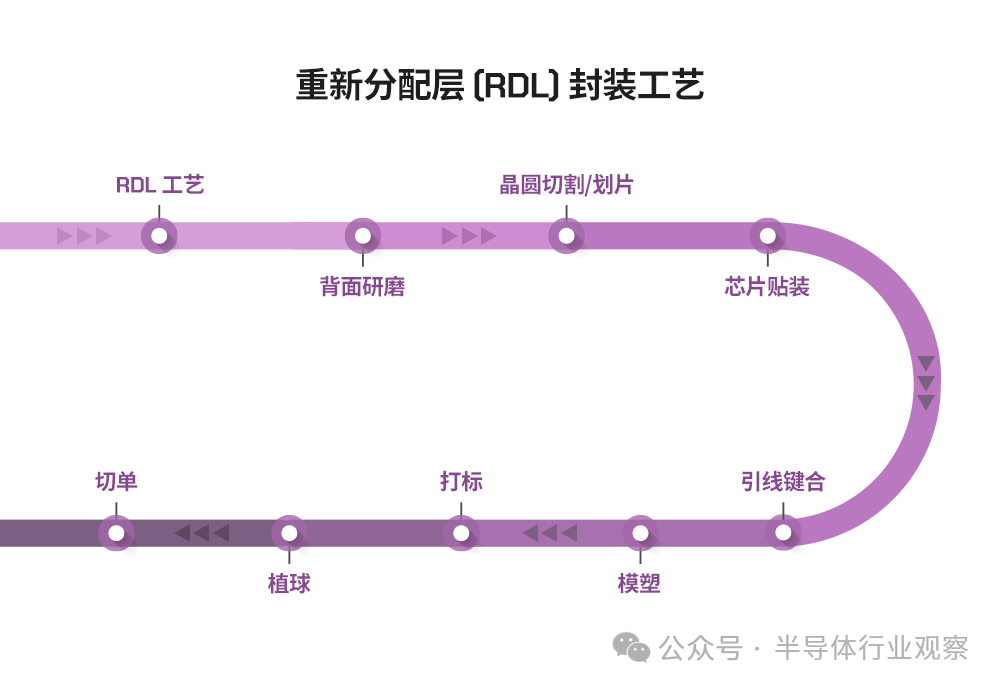

重新分配层封装工艺

利用重新分配层封装工艺,在晶圆原本焊盘上形成新焊盘,以承载额外的金属引线,此种工艺主要用于芯片堆叠。因此,如图所示,重新分配层工序之后的封装工序遵循传统封装工序。在芯片堆叠过程中,每个单独芯片都需重复进行芯片贴装和引线键合这两道工序。

在重新分配层工艺中,首先通过溅射工艺创建一层金属薄膜,之后在金属薄膜上涂覆厚层光刻胶。随后利用光刻工艺绘制电路图案,在电路图案的曝光区域电镀金层,以形成金属引线。由于重新分配工艺本身就是重建焊盘的工艺,因此确保引线键合强度是十分重要的。这也正是被广泛用于引线键合的材料—金,被用于电镀的原因。

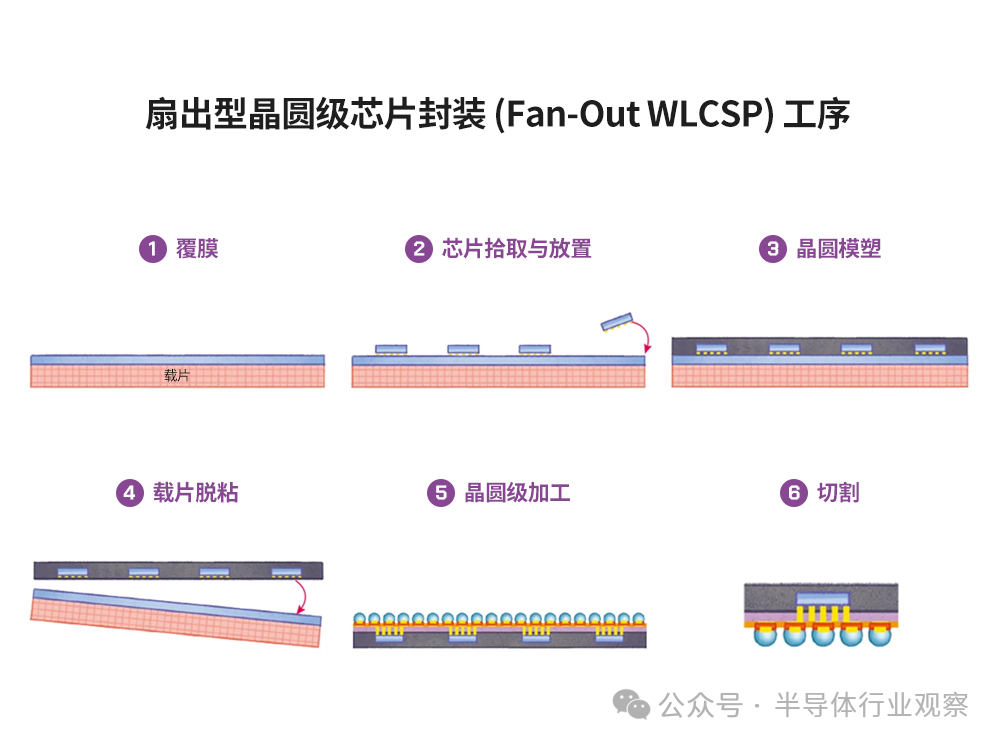

扇出型晶圆级芯片封装工艺

在扇出型晶圆级芯片封装工艺中,首先需要在等同于晶圆形状的载片上贴附一层薄膜。切割晶圆后,再按照一定间距将优质芯片贴在薄膜上,接下来对芯片间隔区域进行模塑,以形成新形状。晶圆模塑完成后,载片和薄膜将被移除。随后在新形成的晶圆上,利用晶圆设备创建金属导线,并附着锡球以便封装。最后,将晶圆切割成多个独立封装体。

一、晶圆模塑

制作扇出型晶圆级芯片封装体时,晶圆模塑是一项重要工序。对于扇出型晶圆级芯片封装件而言,晶圆塑膜需先在芯片上贴附同样形状的晶圆载片,而后将其放置到模塑框架中。将液状、粉状或颗粒状的环氧树脂模塑料(EMC)加入到模塑框架内,对其进行加压和加热处理来塑膜成型。晶圆模塑不仅是扇出型晶圆级芯片封装工艺的重要工序,对于利用硅通孔(TSV)工艺制作已知合格堆叠芯片(KGSD)也是无可或缺的工序。

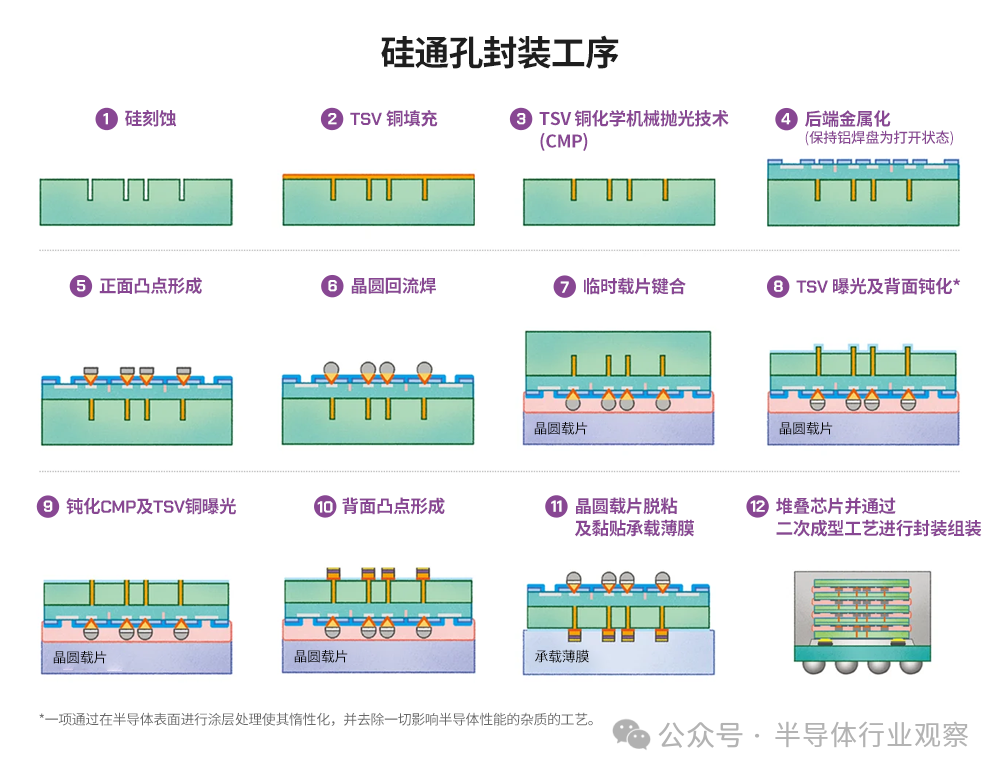

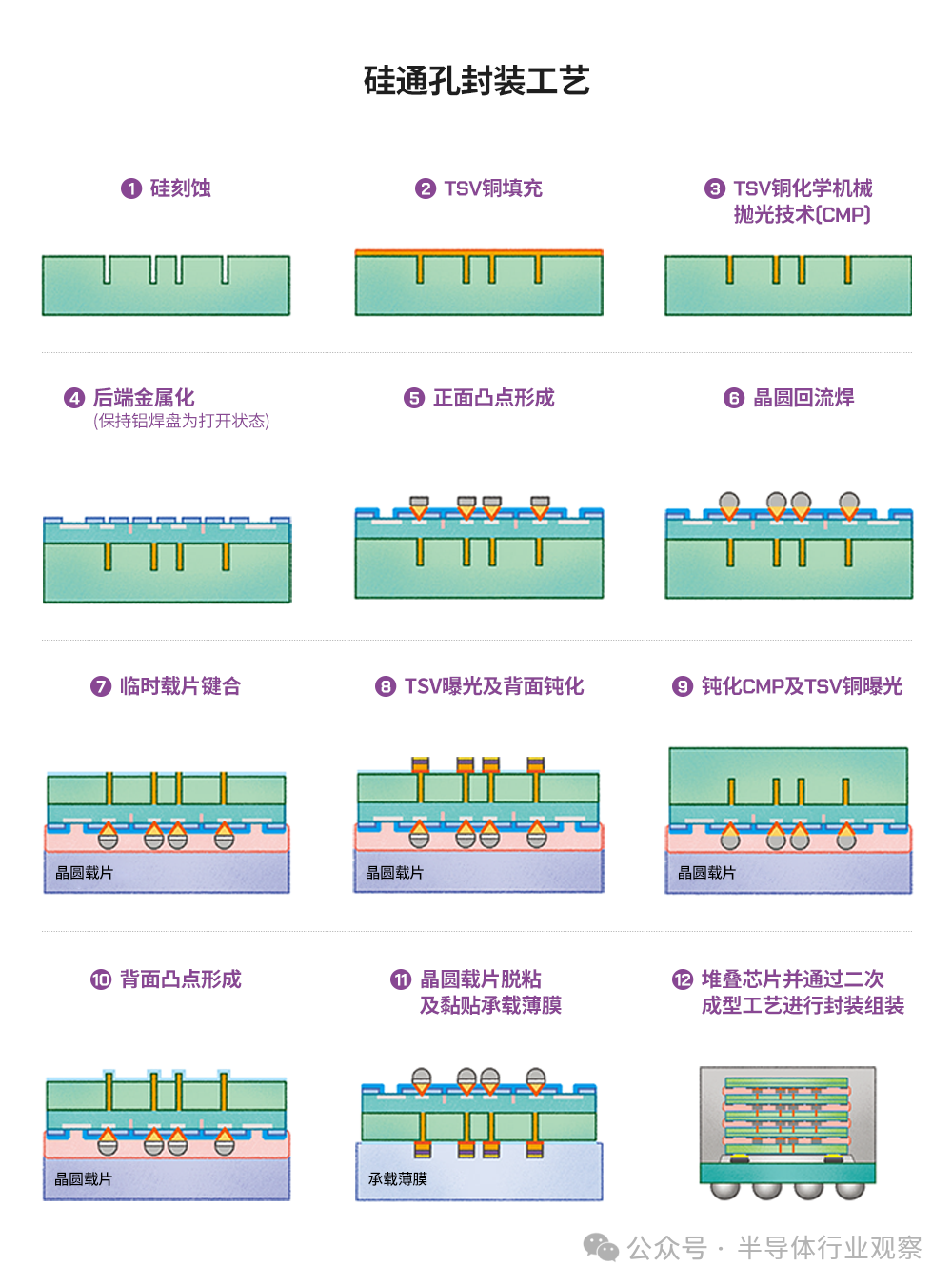

硅通孔封装工艺

下图展示了采用中通孔(Via-middle)方法的硅通孔封装工艺步骤。首先在晶圆制造过程中形成通孔。随后在封装过程中,于晶圆正面形成焊接凸点。之后将晶圆贴附在晶圆载片上并进行背面研磨,在晶圆背面形成凸点后,将晶圆切割成独立芯片单元,并进行堆叠。

接下来,将简单概括中通孔的基本工序。首先在前道工序(Front-end of Line)中,在晶圆上制作晶体管,如互补金属氧化物半导体等。随后使用硬掩模(Hard Mask)6在硅通孔形成区域绘制电路图案。之后利用干刻蚀(Dry Etching)工艺去除未覆盖硬掩膜的区域,形成深槽。再利用化学气相沉积工艺(Chemical Vapor Deposition)制备绝缘膜,如氧化物等。这层绝缘膜将用于隔绝填入槽中的铜等金属物质,防止硅片被金属物质污染。此外绝缘层上还将制备一层金属薄层作为屏障。

此金属薄层将被用于电镀铜层。电镀完成后,采用化学机械抛光(Chemical Mechanical Polishing)技术使晶圆表面保持平滑,同时清除其表面铜基材,确保铜基材只留在沟槽中。然后通过后道工序(Back-end of Line)完成晶圆制造。

使用硅通孔技术制造芯片堆叠封装体时,一般可采用两种类型的封装方法。第一种方法是利用3D芯片堆叠技术的基板封装。第二种方法则需创建KGSD,然后基于KGSD来制作2.5D或3D封装。下文将详细介绍如何创建KGSD,以及如何基于KGSD来制作2.5D封装的过程。

作为利用硅通孔技术制作而成的芯片堆叠封装体,制作KGSD必需经历额外封装工艺,如2.5D封装、3D封装以及扇出型晶圆级芯片封装等,高带宽存储器(HBM)就是KGSD产品的一个典型例子。由于KGSD需经历额外封装工艺,其作为连接引脚的焊接凸点需要比传统锡球更加精细。因此3D封装体中芯片堆叠在基板上,而KGSD中的芯片则堆叠于晶圆上方,晶圆也可以视为KGSD的最底层芯片。就HBM而言,位于最底层的芯片被称为基础芯片或基础晶圆,而位于其上方的芯片则被称为核心芯片。

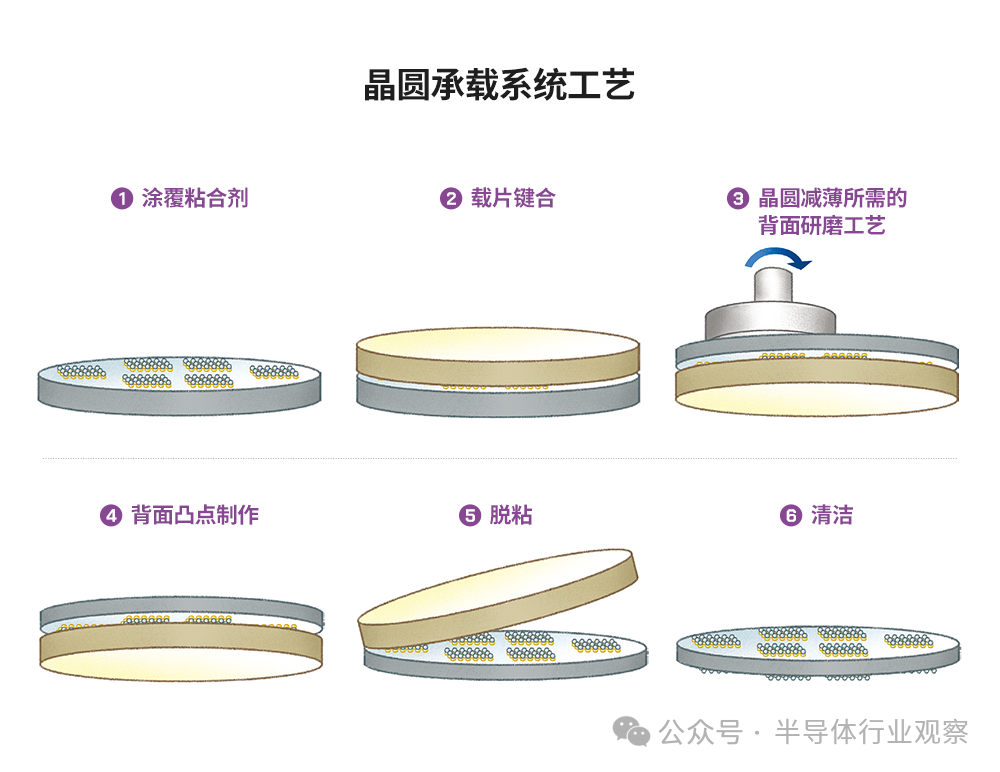

此方法工序如下:首先,通过倒片工艺在基础晶圆和核心晶圆的正面制作凸点。在制作2.5D封装体时,基底晶圆需要排列凸点,使之能够附着到中介层(Interposer);相反,核心晶圆上的凸点布局则是有助于晶圆正面的芯片堆叠。在晶圆正面形成凸点后,应减薄晶圆,同时也需在晶圆背面形成凸点。然而,正如前文在介绍背面研磨工艺时所述,需注意在减薄过程中导致晶圆弯曲。在传统封装工艺中,进行减薄之前,可将晶圆贴附到贴片环架上,以防止晶圆弯曲,但在硅通孔封装工艺中,由于凸点形成于晶圆背面,所以这种保护方法并不适用。为解决此问题,晶圆承载系统(Wafer Support System)应运而生。利用晶圆承载系统,可借助临时粘合剂将带有凸点的晶圆正面贴附于晶圆载片上,同时对晶圆背面进行减薄处理。此时晶圆贴附于晶圆载片上,即使经过减薄也不会发生弯曲。

此外,因晶圆载片与晶圆形式相同,因此也可使用晶圆设备对其进行加工。基于此原理,可在核心晶圆的背面制作凸点,当核心晶圆正面及背面上的凸点均制作完成时,便可对载片进行脱粘。随后将晶圆贴附于贴片环架中,并参照传统封装工艺,对晶圆进行切割。基础晶圆始终贴附于晶圆载片上,从核心晶圆上切割下来的芯片则堆叠于基础晶圆之上。芯片堆叠完成后,再对基础晶圆进行模塑,而后进行晶圆载片脱粘。至此,基础晶圆就变成了堆叠有核心晶圆的模制晶圆。随后对晶圆进行研磨,使其厚度达到制作2.5D封装体所需标准,然后再将其切割成独立的芯片单元,以制作KGSD。HBM成品包装后将运送至制作2.5D封装体的客户手中。

晶圆承载系统工艺

晶圆承载系统是指针对晶圆背面减薄进行进一步加工的系统,该工艺一般在背面研磨前使用。晶圆承载系统工序涉及两个步骤:首先是载片键合,需将被用于硅通孔封装的晶圆贴附于载片上;其次是载片脱粘,即在如晶圆背面凸点制作等流程完工后,将载片分离。

下图展示了晶圆承载系统的工艺步骤。首先在晶圆表面涂覆临时粘合剂,使其贴附于载片上;待晶圆背面的加工工序完成后,即可对载片进行脱粘,并去除残留粘合剂,以确保晶圆表面清洁。

进行载片键合时,需要注意几个因素:首先,载片键合后的晶圆整体厚度应均匀一致;其次,键合面不应存在空隙,两片晶圆对齐应准确无误;此外还应确保晶圆边缘不受到粘合剂污染,且在处理过程中应尽量避免晶圆发生弯曲。在载片脱粘过程中,还应注意:避免晶圆脱离载片后发生损坏,如边缘剥落(Chipping)7或出现裂纹等;避免粘合剂残留;避免凸点变形。

在基于晶圆承载系统的封装工艺中,载片脱粘是一个相对复杂且重要的工序。因此,业界已经提出并研发多种脱粘方法,并针对每一种脱粘方法开发出相应的临时粘合剂。典型的脱粘方法包括热技术、激光烧蚀(Laser Ablation)后剥离、化学溶解、机器剥离后化学清洗等。

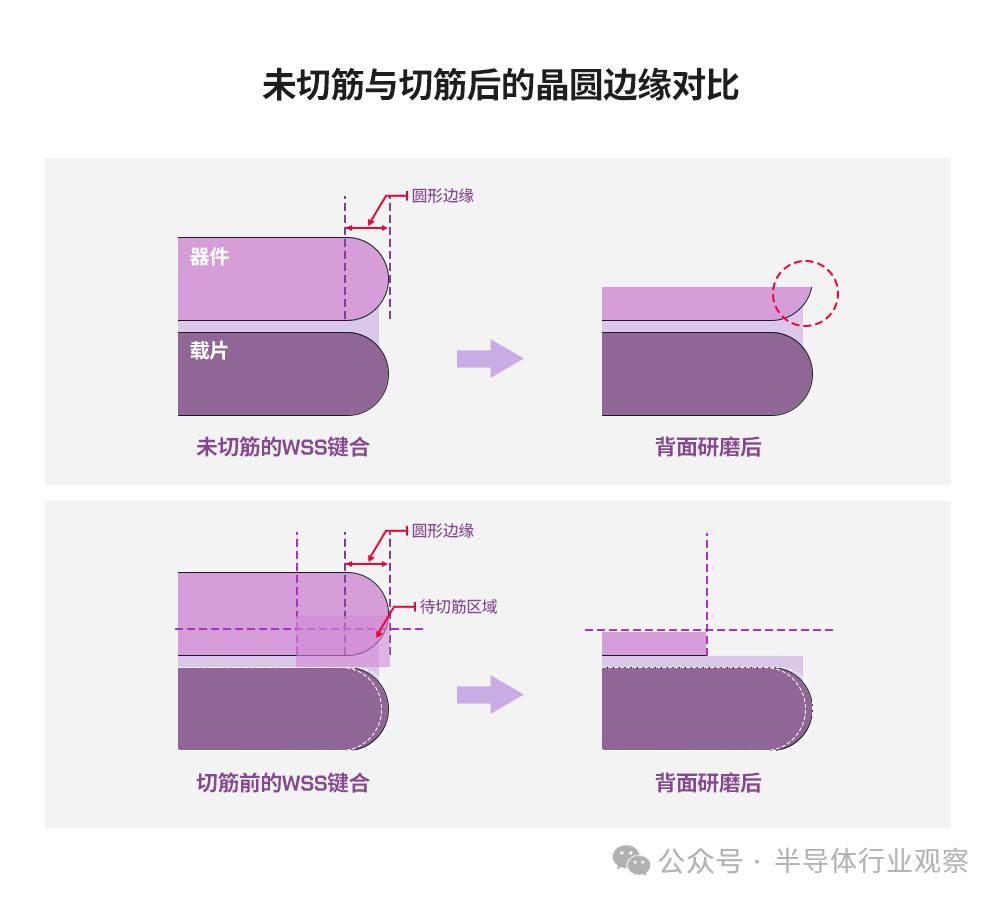

晶圆边缘切筋工艺

如图8上半部分红圈内区域所示,将采用硅通孔工艺封装的晶圆键合到晶圆载片上,经过背面研磨后,其边缘会变得较为尖锐。此种状态下,晶圆后续还将经历光刻、金属薄膜制备、电镀以在背面制作凸点等工序,这些工序会增加晶圆边缘剥落的风险。边缘裂纹可能会延伸至晶圆内部,进而导致后续工序无法进行,最终造成严重的良品损失。为避免此问题,对于采用硅通孔工艺封装的晶圆,在其进行载片键合前,应先对晶圆正面边缘进行切筋并去除修剪部分。如图下半部分区域所示,将切筋后的晶圆贴附于晶圆载片并对其进行背面研磨时,锋利而凸起的边缘已消失。因此,在后续工序中,晶圆边缘剥落的风险也被消除。在切筋过程中,旋转的晶圆切割刀片穿过晶圆边缘,将指定的边缘区域切除。

堆叠工艺

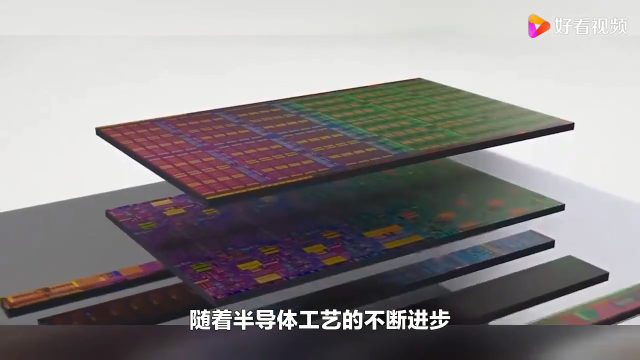

硅通孔封装工艺中,在晶圆正面和背面形成的凸点均用于键合,以便堆叠。同样地,在倒片键合时,批量回流焊(Mass Reflow)工艺8和热压缩(Thermocompression)工艺也用于键合。根据堆叠方式的不同,堆叠工艺可分为芯片与芯片(Chip-to-Chip)堆叠、芯片与晶圆(Chip-to-Wafer)堆叠、晶圆与晶圆(Wafer-to-Wafer)堆叠。

使用硅通孔工艺堆叠芯片时,需使用微型凸点。因此,凸点之间的间距很小,堆叠芯片之间的间距也很小,这就是以可靠性著称的热压缩工艺因被广泛使用的原因。然而,热压缩工艺也存在缺点,那就是耗时长,生产率底,因为在键合过程中必然会耗时去加热加压。因此热压缩工艺逐渐被批量回流焊工艺取代的趋势日益明显。

来源:半导体行业观察

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论