本文将探讨并阐述为企业应用设计电源导轨与处理器导轨监测解决方案的最佳实践。

2025-10-11 11:03:26 4298

4298

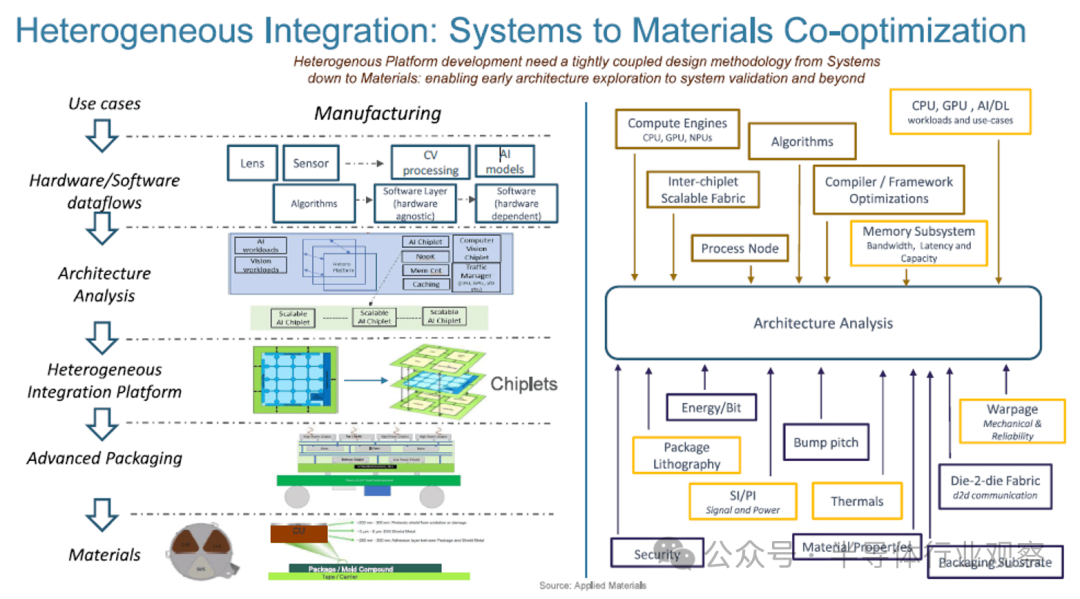

颗是原生支持Transformer全系算子的AI Chiplet“大熊星座”。 Chiplet 集成模式提供低成本、高灵活解决方案 随着摩尔定律逐步放缓以及先进封装等技术的发展,高性能计算芯片的迭代无需再仅仅围绕摩尔定律下的晶体管工艺能力展开,Chiplet架构下的集成模式已经

2024-08-19 00:02:00 4759

4759 最佳的网络打印解决方案发现最佳的网络打印面对hp丰富多样的网络打印解决方案,哪种是最佳的网络打印解决方案呢?如果您愿意,请借给我们几分钟时间,跟随我们来发现最符合您实际需求的方案吧!首先,了解一下您

2009-11-13 21:19:36

三个汽车价格区间。为此,本刊特地采访了几家提供ADAS应用解决方案的半导体厂商,让大家更加了解当前有哪些主流的ADAS应用解决方案。 图1:ZYNQ用于ADAS应用。 图2:4个摄像机的合成技术

2013-01-07 16:58:47

C编程最佳实践.doc

2012-08-17 14:37:18

”微服务一条龙“最佳指南-“最佳实践”篇:Dockerfile

2019-07-11 16:22:33

可编程振荡器解决方案?你要的资料都在这里,一站式免费下载任你学!点击标题即可直达免费下载页面1、用于医疗应用的现场可编程定时解决方案2、最佳设计和布局实践3、MEMS 定时解决方案可提升触屏设备性能4

2017-09-26 14:55:02

摘要: 在刚刚结束的上海云栖大会飞天技术汇分论坛上,阿里云视频云产品架构师罗小飞进行了《阿里云CDN——面向金融政企的CDN最佳实践》主题分享,为上海的嘉宾介绍CDN的解决方案与技术服务体系。在刚刚

2018-06-21 17:29:48

通信技术发展的日新月异,对深度覆盖的要求越来越高.什么是TD-LTE深度覆盖解决方案?这些方案有什么优势?

2019-08-14 07:35:24

本文介绍了一种汽车无线接入技术的解决方案。

2021-05-12 06:40:56

实现快速身份识别,实现智能预警。 动态人脸技术优选解决方案:采用状辨识机理减少复杂背景的干扰可检测左右旋转小于等于30度,上下旋转小于等于15度的人脸人脸检测/捕获率高准确的人脸跟踪,为每人抓拍多张

2018-08-01 15:53:47

分享一个不错的基于RFID技术在物流仓储中的解决方案

2021-09-26 07:52:40

分享一款不错的基于物联网技术的机场安保追踪解决方案

2021-05-26 06:19:09

Socionext公司推出内置Milbeaut系列图像信号处理器的360°全景摄像头设计解决方案,为半专业和普通消费者提供最佳图像质量和卓越的低功耗性能。

2021-05-31 07:12:08

发展,由清华大学交叉信息研究院助理教授马恺声领衔,团队来自于国内外半导体机构,多年来致力于成为基于Chiplet的专用计算领航者,用“小”芯片做“大”芯片,为大算力场景提供定制化高性能计算解决方案。成立

2023-02-21 13:58:08

所以我们开始编写32位和16位代码,并过渡到MPLAB X和XC编译器。我想到的一个主题是声明变量的最佳实践。常规IpType。h或类型。h pr STDIN。或It8或字节char等任何想法,走哪条路?

2019-09-30 12:01:29

Harmony中可用的dsp库时,FFT只有16位版本。换句话说,在PIC32MZ处理器上执行32位FFT的最佳解决方案是什么?许多蒂亚,保罗

2019-08-08 10:49:05

的“incremental evolution(增量式演进)”)。Nokia已于2016年5月末首次演示全双工DOCSIS 3.1技术的概念验证(相关原型解决方案的名称为“XG-CABLE”),实现了在具有100

2019-07-10 06:40:45

安捷伦公司数字测试资深技术/市场工程师 冀卫东为满足日益复杂的数字化系统的设计要求,FPGA的密度及复杂性也在急速增长,越来越多的系统或子系统功能在FPGA内部实现,其先进的功能和高集成度使FPGA成为极具吸引力的解决方案,进而也使得基于内核的FPGA测试方案浮出水面。

2019-07-11 06:15:12

SDON技术的主要优势是什么?多域SDON解决方案的特点有哪些?光网络虚拟化作为SDON的关键技术,面临哪些技术难点?

2021-05-21 06:10:19

应用于工业4.0中的WSN技术及无线通信解决方案

2021-01-08 06:03:23

本帖最后由 dianzijie5 于 2011-9-29 16:42 编辑

假如要为手持终端、便携式设备以及距离插座数英里之遥的固定设备供电,是否还有比电池更好的解决方案呢? 这一

2011-09-29 16:41:36

想找一个基于单片机技术的低成本倒车雷达解决方案,谢谢!

2013-12-18 15:23:43

的数据快速上传到云端。 3. 云服务核心技术全联接ET-iLink核心技术是专门解决方案中软硬云“互联互通”的问题。 四 方案应用拓展设计智慧物业服务的对象主要是物管和住户,主要使用人员是物业管理者

2017-05-25 09:42:05

如果说开源是数字未来的重要一环那么开发者就是开源世界的耕耘者、建设者OpenHarmony 开源开发者成长计划解决方案学生挑战赛为联合国可持续发展的一项或多项目标提供解决方案参赛作品必须

2022-06-08 17:47:57

如果说开源是数字未来的重要一环那么开发者就是开源世界的耕耘者、建设者OpenHarmony 开源开发者成长计划解决方案学生挑战赛为联合国可持续发展的一项或多项目标提供解决方案参赛作品必须

2022-06-08 21:47:31

机器人辅助工程创新实践教育解决方案

2016-04-11 16:49:41

基于LoRa+蓝牙技术的校园学生安全及定位解决方案有哪些功能?基于LoRa+蓝牙技术的校园学生安全及定位解决方案的核心技术优势有哪些?

2021-07-09 07:00:41

我要如何发布我的HarmonyOS组件或解决方案?

2022-06-02 15:55:36

全球电源转换解决方案领导者!优势:设计紧凑、高性能、具成本效益的电源方案!

2017-03-05 20:56:31

` 本帖最后由 zgzzlt 于 2012-8-16 14:01 编辑

简单之美——软件开发实践者的思考`

2012-08-06 12:29:59

综合布线系统凭借尖端的技术与智能化设计,具有无与伦比的优越性。那么谁知道综合布线系统中的屏蔽技术具体有哪些解决方案吗?

2019-08-06 06:28:23

提供各种传感器、微控制器和功率半导体,帮助降低汽车的油耗/排放,提高安全性,并使汽车成为消费者买得起的产品,从而为推动可持续发展的交通发展做出贡献。减少道路交通事故伤亡人数英飞凌提供的各种解决方案

2018-12-13 17:15:46

纹理是游戏不可或缺的一部分。

这是一个艺术家可以直接控制的领域,以提高游戏的性能。

本最佳实践指南介绍了几种纹理优化,这些优化可以帮助您的游戏运行得更流畅、看起来更好。

最佳实践系列指南的总体目标

2023-08-28 06:39:47

软件工程实践者的研究方法

2016-11-07 10:36:17

远程视频监控解决方案中动态IP技术的应用是什么?

2021-05-31 06:52:08

提出了长期性的挑战。为了在不牺牲技术的条件下保持企业的竞争力,商家考虑实现集群化解决方案 — 在集群化环境内,一组应用程序或资源就像单一系统那样运行 - 以便有利于创建经济有效的高可用架构。但是,面对

2009-11-13 21:21:20

科胜讯(Conexant)音讯解决方案赢得EDN年度最佳创新产品奖

单芯片音讯解决方案整合了扬声器技术、处理功能以及可

2009-07-01 08:45:30 3726

3726 安捷伦LTE和WiMAX测试设备获最佳实践奖

安捷伦科技公司荣膺Frost & Sullivan(弗若斯特沙利文公司)颁发的“全球LTE和WiMAX测试设备市场领先份额最佳实践奖”。安捷

2009-12-24 09:17:53 1216

1216 凯悌集团推出Set-Top Box 最佳的主被动解决方案

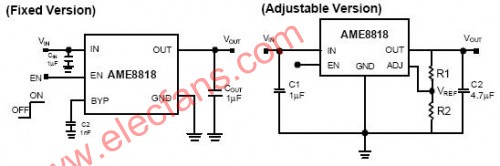

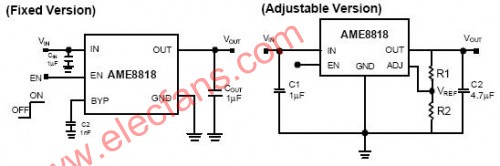

AME(安茂微电子) 提供最佳电源管理解决方案:

随着数字家庭

2010-01-25 00:50:02 1741

1741

凯悌集团推出车电保全应用产品之主被动元件最佳解决方案

APEC的产品是车电保全最佳IGBT、Power MOSFET解决方案:

2010-09-30 10:51:45 1066

1066

MySql5.6性能优化最佳实践

2017-09-08 08:47:44 13

13 MySQL 集群最佳解决方案

2017-09-09 08:40:14 10

10 为了帮助业务领导者在将更多互联产品添加到其投资组合时了解到需要做出改变,PTC开发了互联产品成熟度模型。该成熟度模型基于几十年来与几乎所有行业的产品制造商数百次合作中收集的最佳实践。

2018-05-29 08:06:00 3677

3677 博世集团不仅是德国工业4.0战略的重要发起者,更是全球工业4.0领先的实践者,而作为博世集团至关重要的工业部——博世力士乐以其世界上领先的驱动和传动的液压和电控系统及源自全球各地的成功经验,成为了博世集团工业4.0和工业能效提高的最佳先锋。

2019-07-12 11:56:02 4502

4502 在人工智能成为国家战略的当下,儿童理应成为技术的最佳受益人和最佳实践者。

2019-11-19 15:46:29 725

725 ,5G不论是建设速度还有规模都超出了预期。而这一切都离不开奋战在一线的在5G建设实践过程中作出重要贡献的人。为此,通信世界全媒体特评选出十位2020年5G最佳实践者,以激励更多的人投身到5G实践中。

2020-12-25 10:19:39 1298

1298 从 DARPA 的 CHIPS 项目到 Intel 的 Foveros,都把 chiplet 看成是未来芯片的重要基础技术。简单来说,chiplet 技术就是像搭积木一样,把一些预先生产好的实现特定

2021-01-04 15:58:02 60161

60161 导语:在LED显示屏产业鲜有的六家上市企业中,有些以营收闻名,有些以利润取胜。而有一家企业——奥拓电子,在具备一定规模和体量的基础上,因踩对了多次技术迭代点,笔者认为可算是产业界「新技术的敏锐实践者

2021-04-09 14:44:23 2729

2729

收益,并且也是光伏“大数据”变革中的实践者。 通过资源链接、行业建设、品牌推广、扶贫行动等支持,促进优质光伏产品资源的规模化发展,鼓励和号召每一个人都能参与新能源发展建设。中能融合了区块链、大数据、物联网、人工智能等

2021-07-29 14:33:42 2003

2003

9月4日,曙光总裁历军做客央视高端访谈栏目《对话》,围绕 “数字化服务新逻辑”分享了作为产业实践者的探索与思考。他表示,站在第二个百年的起点,只有持续发展核心技术,建立企业间的紧密协同,牢牢掌握

2021-09-23 09:49:29 1803

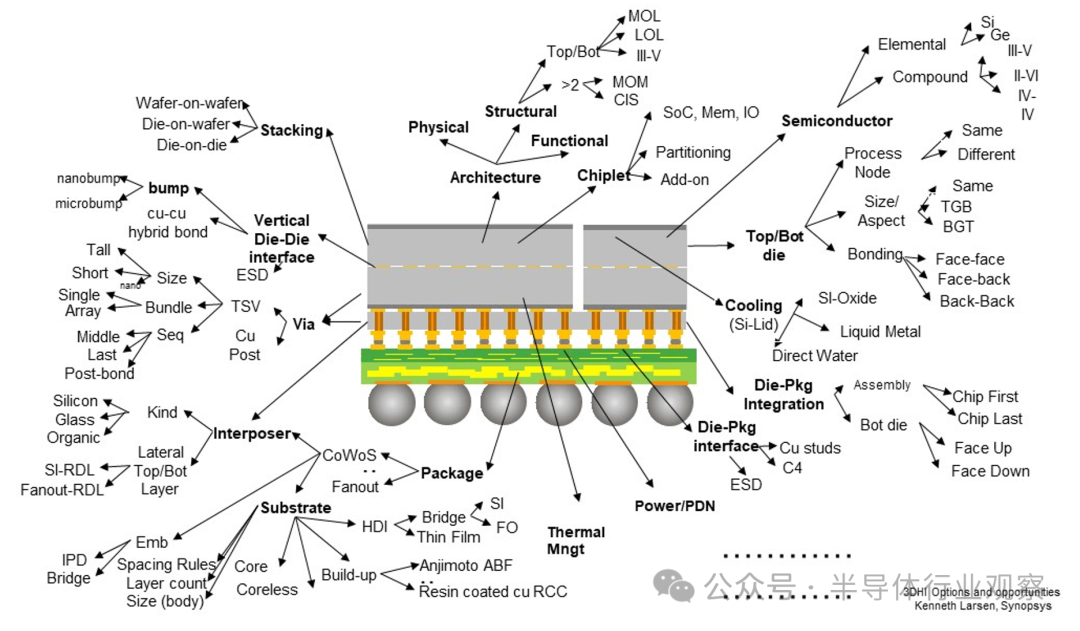

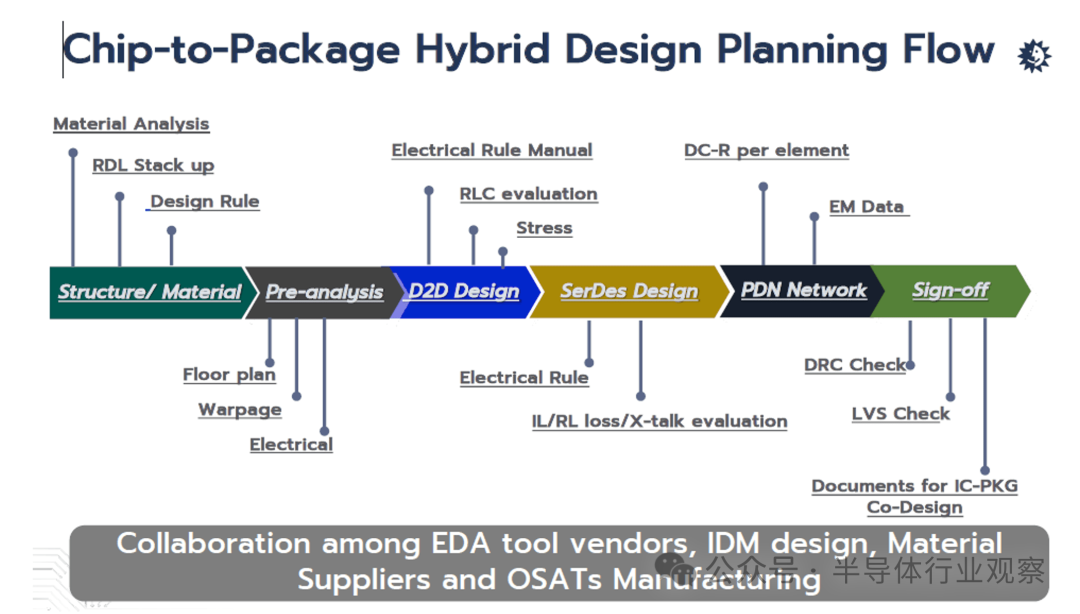

1803 小芯片(Chiplet)已经成为当今大厂角逐的一大方向,对于小芯片来说,需要一种芯片到芯片的互连/接口技术,现在已有多种Die-to-Die接口可以满足这类需求。其中,基于SerDes的或并行

2022-02-15 15:14:48 3963

3963

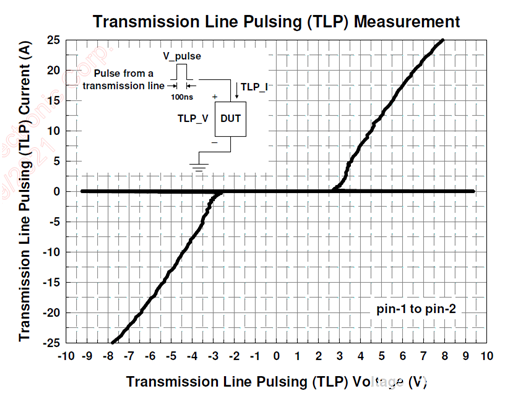

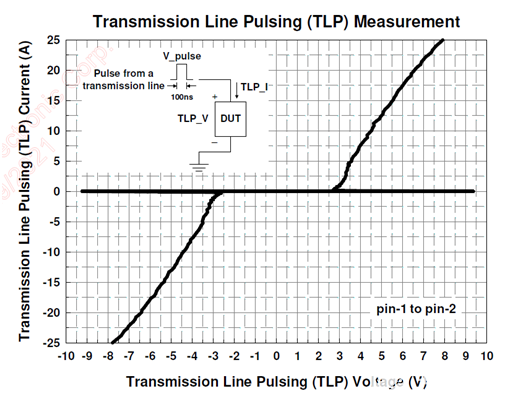

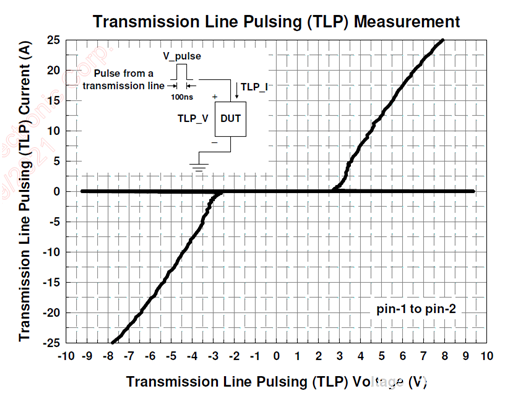

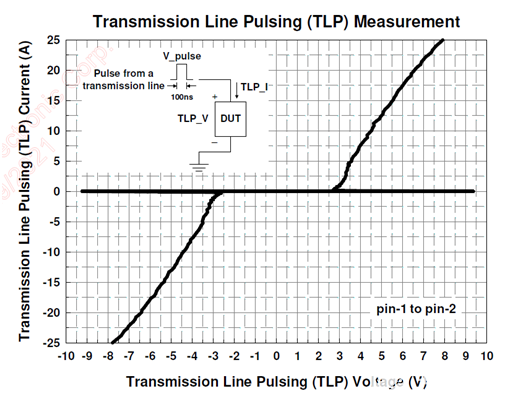

AMAZING晶焱DP2.0应用的ESD/EOS最佳解决方案

2022-08-08 14:37:25 2294

2294

遵循上述最佳实践,组织可以开发和自动化其解决方案的交付过程,以有效地实现其业务目标。

2022-08-15 14:41:09 1531

1531 amazingic晶焱科技DP2.0应用的 ESD/EOS 最佳解决方案

2022-10-10 13:57:31 2266

2266

这篇文章根据我们目前在游戏中使用 NVIDIA RTX 光线跟踪的经验收集了最佳实践。实用技巧被组织成简短的、可操作的项目,供今天从事光线跟踪工作的开发人员使用。他们旨在深入了解什么样的解决方案在大多数情况下会带来良好的性能。为了找到特定案例的最佳解决方案,我总是建议进行分析和实验。

2022-10-10 15:01:15 1773

1773 图像传感器处理和最佳实践

2022-11-15 20:30:07 0

0 功率-性能-面积(PPA)天花板的一个绝佳技术选择。 所谓Chiplet,可将不同功能的裸片(Die)通过2D或2.5D/3D的封装方式组装在一起,其好处是不同功能的Die可以采用不同的工艺制造,然后以异构的方式集成在一起。但是到目前为止,实现Chiplet架构一直非常困难。为了做到

2022-11-23 07:10:09 1576

1576 近日, 芯动科技高速接口IP三件套之明星产品--Innolink Chiplet互连解决方案, 相继亮相第二届中国互连技术与产业大会、智东西Chiplet公开课。芯动科技技术总监高专分享了两场专业

2022-12-23 20:55:03 2907

2907 经纬恒润与北极雄芯签署战略合作协议,双方拟利用各自资源及技术优势,共同探索基于Chiplet架构的智能驾驶整体解决方案。

2023-02-23 10:08:18 1639

1639 的应用程序的解决方案和工具。当使用最流行的 Java 框架(如 Spring Boot 或 Quarkus)时,这些 Kubernetes 建议中的一些是设计强制的。我将向您展示如何有效地利用它们来简化开发人员的生活。

2023-03-14 17:47:18 1162

1162 与SoC相反,Chiplet是将一块原本复杂的SoC芯片,从设计时就先按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的半导体制程工艺进行分别制造,再通过先进封装技术将各个单元彼此互联,最终集成封装为一个系统级芯片组。

2023-03-29 10:59:32 3937

3937 Chiplet技术对芯片设计与制造的各个环节都带来了剧烈的变革,首当其冲的就是chiplet接口电路IP、EDA工具以及先进封装。

2023-04-03 11:33:33 868

868 AMAZINGIC晶焱科技PCIe 4.0的 ESD 最佳解决方案

2022-05-26 15:49:37 1777

1777

如果说开源是数字未来的重要一环那么开发者就是开源世界的耕耘者、建设者OpenHarmony开源开发者成长计划解决方案学生挑战赛为联合国可持续发展的一项或多项目标提供解决方案参赛作品必须

2022-06-13 09:41:42 998

998

安全的软件开发最佳实践是必要的,因为安全风险无处不在。在网络攻击盛行的时代,它们可以影响每个人,包括个人、公司和政府。因此,确保软件开发的安全性至关重要。

在这里,我们将解释了什么是安全软件,如何确保软件的安全性,并提供 安全软件开发的最佳实践 。

2023-05-08 10:51:35 1665

1665

来源:光学半导体与元宇宙Chiplet将满足特定功能的裸芯片通过Die-to-Die内部互联技术,实现多个模块芯片与底层基础芯片的系统封装,实现一种新形势的IP复用。Chiplet将是国内突破技术

2023-05-16 09:20:49 2711

2711

很明显,SQL注入攻击会造成严重的经济和声誉后果。为了避免成为这种攻击的受害者,开发人员必须采取主动措施保护他们的系统免受恶意行为者的攻击。以下是开发人员和组织防止SQL注入攻击的五大最佳实践:

2023-07-16 11:46:26 1336

1336 半导体产业正在进入后摩尔时代,Chiplet应运而生。介绍了Chiplet技术现状与接口标准,阐述了应用于Chiplet的先进封装种类:多芯片模块(MCM)封装、2.5D封装和3D封装,并从技术特征

2023-07-17 16:36:08 2169

2169

及两者之间的关系。 一、Chiplet的概念和优点 Chiplet是指将一个完整的芯片分解为多个功能小芯片的技术。简单来说,就是将一个复杂的芯片分解为多个简单的功能芯片,再通过互联技术将它们组合在一起,形成一个整体的解决方案。 Chiplet技术的优点主要有以下几点: 1. 提高芯片的灵活性。芯片

2023-08-25 14:49:53 4513

4513 电子发烧友网站提供《SAN管理最佳实践指南.pdf》资料免费下载

2023-08-29 09:20:20 0

0 电子发烧友网站提供《SAN设计和最佳实践指南.pdf》资料免费下载

2023-09-01 11:02:55 2

2 电子发烧友网站提供《Windows 10迁移的最佳实践.pdf》资料免费下载

2023-09-07 15:37:04 0

0 电子发烧友网站提供《AI引擎内核编码最佳实践指南.pdf》资料免费下载

2023-09-14 14:58:21 0

0 Chiplet主流封装技术都有哪些? 随着处理器和芯片设计的发展,芯片的封装技术也在不断地更新和改进。Chiplet是一种新型的封装技术,它可以将不同的芯片功能模块制造在不同的芯片中,并通过

2023-09-28 16:41:00 2931

2931 [中国,2023年9月27日]华为星河AI网络解决方案荣获全球著名增长咨询公司 Frost Sullivan 弗若斯特沙利文(以下简称“沙利文”)AI训练场景最佳实践 “2023全球技术领导奖

2023-09-28 21:35:01 1169

1169

电子发烧友网站提供《未来汽车创新的最佳解决方案.pdf》资料免费下载

2023-11-17 10:42:37 0

0 2023开放原子开发者大会 . OPENATOM DEVELOPERS CONFERENCE 云原生技术前沿落地实践分论坛 2023.12.16 随着云原生技术的蓬勃发展,云原生已成为企业数字化转型

2023-12-09 18:45:02 1025

1025 商用实践及产业影响力,位居IDC MarketScape2023年中国智慧园区解决方案市场 领导者 。 IDC Market Sc ape: 华为位居中国智慧园区解决方案领导者 IDC

2023-12-19 15:50:02 874

874

致力于为AIoT市场提供Chiplet芯片级解决方案的勇芯科技(Bravechip)推出了微型模块BCL601S1,用于提供心电图(ECG)读数的医疗设备。

2023-12-22 14:01:30 1565

1565 Chiplet技术是一种将集成电路设计和制造的方法,其中一个芯片被分割成多个较小的独立单元,这些单元通常被称为“chiplets”。每个chiplet可以包含特定的功能块、处理器核心、内存单元或其他

2024-01-08 09:22:08 6862

6862 什么是Chiplet技术?Chiplet技术是一种在半导体设计和制造中将大型芯片的不同功能分解并分散实现在多个较小和专用的芯片(Chiplets)上的方法。这些较小的芯片随后通过高速互连方式集成到一个封装中,共同实现全功能的芯片系统。

2024-01-25 10:43:32 4059

4059

日前,中国上市公司协会发布首届“上市公司投资者关系管理最佳实践”榜单,海格通信(SZ 002465)成功入选该项荣誉榜单,充分体现了中国上市公司协会对公司长期以来在投资者关系管理方面所作出努力的高度认可和肯定。

2024-04-18 10:09:30 974

974

这些要求,因此,多芯片集成(如Chiplet设计)成为了一种新的趋势。 Chiplet设计 带来的挑战及行业解决方案 Chiplet设计带来了许多优势,同时也带来了众多新的挑战。这些挑战主要集中在以下几个方面: ◎ 热管理问题:芯片之间的热传导和散热是一

2024-07-24 17:13:36 1292

1292 基于RTOS编写应用程序时,有一些要注意事项。在本节中,您将学习RTOS开发最佳实践,例如POSIX合规性、安全性和功能安全认证。

2024-08-20 11:24:55 1200

1200 电子发烧友网站提供《MSP430 FRAM技术–使用方法和最佳实践.pdf》资料免费下载

2024-08-23 09:23:28 0

0 了近3倍,算力提升了6倍,这背后离不开Chiplet(小芯片)设计方案的引入。Chiplet技术,作为“后摩尔定律时代”提升芯片性能的关键解决方案之一,正逐渐受到业界的广泛关注。

2024-10-16 14:08:34 1441

1441 爱芯元智车载事业部(品牌“爱芯元速”)凭借在车载芯片领域的创新技术研发实力以及在推动量产上车方面的卓越成绩收获本届“金辑奖”的“2024最佳技术实践应用奖”。

2024-10-25 11:39:36 1008

1008 效率、降低成本、保证产品质量。 MES系统的最佳实践案例 引言 在当今竞争激烈的制造业环境中,企业必须不断寻求创新和改进的方法来保持竞争力。MES系统作为一种关键的信息技术工具,已经被广泛应用于各种制造行业,以实现生产过程的优化和管理。本文将探讨MES系统的最佳实践案

2024-10-27 09:33:28 3705

3705 随着半导体技术的飞速发展,芯片设计和制造面临着越来越大的挑战。传统的单芯片系统(SoC)设计模式在追求高度集成化的同时,也面临着设计复杂性、制造成本、良率等方面的瓶颈。而Chiplet技术的出现,为这些问题提供了新的解决方案。本文将详细解析Chiplet技术的原理、优势以及其在半导体领域的应用前景。

2024-12-26 13:58:51 2054

2054

在全球瞩目的Network X年度颁奖典礼上,华为5GC解决方案凭借其卓越的技术创新和市场影响力,成功摘得“最佳核心网产品解决方案奖”。该奖项是对华为5G-A核心网标准制定、技术创新、商业实践和行业推广方面成就的高度认可,为移动AI时代体验经营、创新业务、自智网络等新场景树立了新的标杆。

2025-01-10 10:36:09 889

889 《兆芯最佳实践应用场景解决方案》现已正式发布,扫描下方二维码或点击阅读原文即可获取下载。

2025-01-13 14:45:22 906

906 随着半导体行业的技术进步,尤其是摩尔定律的放缓,芯片设计和制造商们逐渐转向了更为灵活的解决方案,其中“Chiplet”和“先进封装”成为了热门的概念。

2025-04-14 11:35:18 1170

1170

,共论未来网络转型之路。随着自智网络近年来在通信产业热度的持续上升,本次大会首次设立“自智网络最佳实践奖”,华为以自动驾驶网络(ADN)L4解决方案突出的技术创新和前沿实践成果,成为首个斩获该奖项的通信厂商。 华为ADN L4解决方案荣获自智网络最佳

2025-05-09 19:47:45 1454

1454

2025年5月,中国上市公司协会正式公布“中国上市公司2024年度投资者关系管理最佳实践”评选结果。洲明科技凭借专业表现与持续的沟通成效,从沪、深、北交所超5000家上市公司中脱颖而出,成功斩获该项

2025-05-23 16:37:10 973

973 近日,鲲鹏昇腾开发者大会2025(KADC 2025)在北京正式启幕。软通动力作为鲲鹏路线坚定的拥护者与实践者,受邀出席大会,正式发布软通动力智慧园区RAG(Retrieval Augmented Generation 检索增强生成)解决方案。

2025-05-29 10:00:46 780

780

在大型互联网企业中,Linux网络管理是运维工程师的核心技能之一。面对海量服务器、复杂网络拓扑、高并发流量,运维人员需要掌握从基础网络配置到高级网络优化的全套技术栈。本文将结合大厂实际场景,深入解析Linux网络管理的关键技术和最佳实践。

2025-07-09 09:53:04 792

792 FutureNet Asia 2025峰会期间,华为携手泰国领先电信运营商AIS凭借在网络智能化领域的创新实践,荣获“最佳网络AI解决方案奖”。继2023年荣获“亚太区域最佳运营商”、2024年摘得“最佳用户体验奖”之后,AIS与华为再次在AN L4领域获高度认可。

2025-10-14 15:02:03 699

699

电子发烧友App

电子发烧友App

评论