莱迪思半导体公司日前宣布MachXO2 PLD系列的2.5mmx2.5mm 25球型晶圆级芯片尺寸封装(WLCSP)的样片现已发运。目前MachXO2器件结合了超小封装尺寸——至今在PLD市场还未被超越

2011-09-09 15:44:49 2135

2135 摘要:据彭博社报道,Facebook聘请曾在谷歌负责设备芯片开发的主管沙赫里亚尔·拉比(Shahriar Rabii)担任其副总裁,显示出Facebook打造自主研发芯片的决心。彭博社认为,Facebook与其他科技巨头一样,正试图降低对英特尔、高通、英伟达等芯片厂商的依赖。

2018-07-16 10:57:18 3608

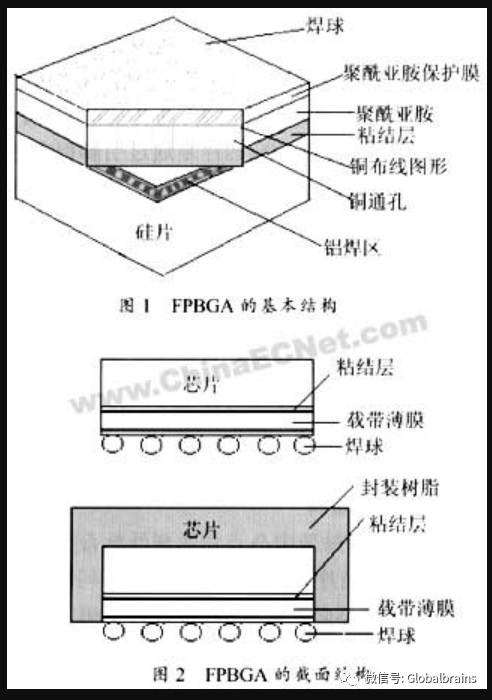

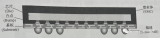

3608 所谓芯片尺寸封装就是CSP (Chip Size Package或Chip Scale Package)。JEDEC(美国EIA协会联合电子器件工程委员会)的JSTK一012标准规定,LSI芯片封装

2023-09-06 11:14:55 702

702

,成立于1987年,是当时全球的第一家专业积体电路(集成电路/芯片)制造与服务兼硅晶圆片代工的大型跨国企业。

台积电占据了全球芯片代工市场过半的份额。2022年,台积电全年营业收入2.264万亿元新台币

2023-04-27 10:09:27

台积电0.18工艺电源电压分别是多少?是1.8v跟3.3v吗?

2021-06-25 06:32:37

台积电宣布5nm基本完工开始试产:面积缩小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

有机会“独吞”A7代工订单。 台积电作为全球规模最大的专业集成电路制造公司,其技术优势的领先,在业界可谓屈指可数。台积电积极开发20纳米制程,花旗环球证券指出,在技术领先MAX3232EUE+T优势下,未来1

2012-09-27 16:48:11

制造技术为今年的10.5寸和12.9英寸iPad Pro制造A10X芯片。事实上,A10X是第一款采用该技术生产的芯片,尽管台积电还有其他客户。 相比之下,iPhone 7和7 Plus中使用的A10

2017-08-17 11:05:18

,如示波器,电源等,同时探针台提供样品细节可视化功能,协助芯片设计人员对失效芯片进行分析在显微镜的辅助下,使用探针接触芯片管脚,给芯片加电,观察芯片加电后的功耗表现。芯片失效分析探针台测试probe

2020-10-16 16:05:57

相当于TSOP内存芯片面积的1/6。与BGA封装相比,同等空间下CSP封装可以将存储容量提高三倍。

芯片尺寸封装(CSP)和BGA是同一时代的产物,是整机小型化、便携化的结果。美国JEDEC给

2023-12-11 01:02:56

是由石英沙所精练出来的,晶圆便是硅元素加以纯化(99.999%),接着是将些纯硅制成硅晶棒,成为制造集成电路的石英半导体的材料,将其切片就是芯片制作具体需要的晶圆。晶圆越薄,成产的成本越低,但对工艺就要

2016-06-29 11:25:04

的基础。CPU和GPU的整合会推动百亿级别的超算的发展,而这或许也会将英特尔与AMD之间的竞争带到另外一个阶段。据外媒报道称,AMD和Intel都赢得了美国DOE百亿级超级计算机的合同。除此以外,台积电也在积极

2020-03-19 14:04:57

意味着该行业的低迷会持续更久。 但也有分析师补充称,台积电的业绩可能最早会在第三季度反弹,与苹果、英伟达和AMD预测的季度前景改善相对应。

在芯片方面,据财报披露,5纳米制程芯片出货占公司2023年第一季

2023-05-06 18:31:29

发挥着重要作用。谷歌与芯片设计公司博通合作,开发用于“巨型数据中心”服务器的张量处理单元(TPU),希望加速定制人工智能算法的计算,以帮助识别和分析云端图像、语言、文本和视频。全球最大的代工芯片制造商台

2018-08-31 09:24:57

处理器号称是“全球第一个AI汽车超级芯片”,将采用台积电16nm FinFET+工艺制造,集成多达70亿个晶体管,性能方面,Xavier预计可以达到30 DL TOPS,比现在的Drive PX 2平台

2018-07-31 09:56:50

一共就72亿美元左右,台积电一家就拿走了其中3/4的份额。如果消息属实,台积电面临客户的砍单情况将会比预期的还要严重。

【博世拟15亿收购芯片制造商TSI】

4月26日,博世宣布将收购美国芯片制造

2023-05-10 10:54:09

又全数到台寻求产能帮助,导致早已供不应求的8吋晶圆产能缺货持续扩大。不止在台寻求产能帮助,远到日、韩、新加坡及马来西亚,甚至俄罗斯都有台系IC设计公司前往投石问路,毕竟,以目前台积电、联电及世界先进

2020-10-15 16:30:57

内建封装(PoP)技术。 台积电明年靠着16纳米FinFET Plus及InFO WLP等两大武器,不仅可以有效对抗三星及GlobalFoundries的14纳米FinFET制程联军,还可回防全球最大

2014-05-07 15:30:16

产业发展,新区设立了集成电路天使投资基金、创投基金等产业发展基金,成立了集成电路产业技术创新中心和产业服务中心,引进了台积电、ARM、展讯、鸿海(富士康)等一批行业龙头企业,集成电路芯片设计、晶圆制造

2017-09-25 10:56:40

需求量高达百万片,2017年将从PMIC 4规格转到PMIC 5,预计PMIC 5在2017年底开始小量生产,真正大量出货会落在2018年,未来PMIC 5将逐渐成为高通电源管理芯片主流,而台积电将以

2017-09-22 11:11:12

据外媒报道,预计台积电将获得高通新一代电源管理芯片(PWM IC)70%至80%的订单。高通前一代电源管理芯片是由中芯国际(SMIC)生产的,后者在其8英寸晶圆厂使用0.18至0.153微米工艺来生

2017-09-27 09:13:24

。先进的刻蚀技术使芯片制造商能够使用双倍、四倍和基于间隔的图案来创造出现代芯片设计的微小尺寸。和光刻胶一样,刻蚀也分为“干式”和“湿式”两种。干式刻蚀使用气体来确定晶圆上的暴露图案。湿式刻蚀通过化学

2022-04-08 15:12:41

寸指的是什么部分?要产出大尺寸的晶圆制造又有什么难度呢?以下将逐步介绍半导体最重要的基础——「晶圆」到底是什么。晶圆(wafer),是制造各式电脑芯片的基础。我们可以将芯片制造比拟成用乐高积木盖房子

2017-09-04 14:01:51

。相比之下,中国芯片厂商则少了许多麻烦。研究机构ICInsights的数据称,今年中国芯片厂商出货量增长高达40%。 在谈及芯片设计厂商将封装合同外包给台积电等封装公司时,市场调研机构Bernstein

2016-06-29 11:17:40

通和AMD也需要台积电生产芯片。 苹果的芯片项目已经进行了好几年,被认为是该公司最秘密的项目之一。2018年,苹果成功开发了一款基于iPad Pro处理器的Mac芯片,用于内部测试,这让该公司有信心在今年宣布这样的转型。

2013-12-21 09:05:01

全球进入5nm时代目前的5nm制造玩家,只有台积电和三星这两家了。而三星要到明年才能实现量产,就今年来看,台积电将统治全球的5nm产业链。在过去的一年里,台积电的5nm研发节奏很快,该公司在2019

2020-03-09 10:13:54

求教,怎么才能找出这种芯片的尺寸?????

2016-03-24 14:39:58

,尼康在ASML面前被打的毫无还手之力,高端光刻机市场基本被ASML占据。光刻机工作原理在加工芯片的过程中,光刻机通过一系列的光源能量、形状控制手段,将光束透射过画着线路图的掩模,经物镜补偿各种光学误差

2018-09-03 09:31:49

,ASML还预计2020年,公司将交付35台EUV光刻机,2021年则会达到45台到50台的交付量,是2019年的两倍左右。 除了光刻机外,其他如刻蚀机等设备购买、工艺研发也都需要大量的资金,这就驱使

2020-02-27 10:42:16

大量的协调和沟通。需要一种将各个部分更紧密地结合在一起以促进更好协作的方法。因此,台积电开发了开放式创新平台,或称OIP。他们很早就开始了这项工作,刚开始这项工作时, 65 nm 还是前沿工艺。今天

2024-03-13 16:52:37

的协调和沟通。需要一种将各个部分更紧密地结合在一起以促进更好协作的方法。因此,台积电开发了开放式创新平台,或称OIP。他们很早就开始了这项工作,刚开始这项工作时, 65 nm 还是前沿工艺。今天,OIP

2024-03-27 16:17:34

各类常用工艺库台积电,中芯国际,华润上华

2015-12-17 19:52:34

回收EUTECH芯片 回收EUPEC芯片181-2470 同上-1558 同步中芯发布公告称,公司就购买用于生产晶圆的阿斯麦产品与阿斯麦集团签订购买单,根据阿斯麦购买单购买的阿斯麦产品定价,阿斯麦

2021-07-19 15:09:42

北京时间11月8日晚间MAX3232EUE+T消息,展讯通信(Nasdaq:SPRD)今日宣布,基于展讯通信40纳米2.5G基带芯片SC6530的两款三星手机E1282(GT-E1282T

2012-11-09 15:43:30

43.3亿美元,季增5.5%。结语:台媒表示,台积电涨价现已生效,但台积电的价格合同是一年一次的,因此新价格应该到2022年1月才会生效。台积电作为全球最大的芯片制造商,此翻大幅涨价将标志公司走上

2021-09-02 09:44:44

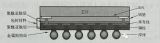

晶圆级芯片封装技术是对整片晶圆进行封装测试后再切割得到单个成品芯片的技术,封装后的芯片尺寸与裸片一致。

2019-09-18 09:02:14

最新芯片银行芯片卡采集器【电/薇:159,***,***满丨意丨给丨钱】20180404【V信已开通】以实力求生存,以信誉求发展】参考消息网2月27日报道美国战略之页网站2月10日发表题为《特种作战

2018-04-04 20:28:33

想要找一款芯片尺寸比较小的能搭载安卓系统的芯片,大神们有推荐么~

2017-10-18 21:07:10

IC尺寸微缩仍面临挑战。为了使芯片微缩,总是利用光刻技术来推动。然而近期Sematech在一次演讲中列举了可维持摩尔定律的其他一些技术。1. 零低k界面:在目前Intel的45nm设计中,采用硅衬底

2014-01-04 09:52:44

物联网被业内认为是继计算机、互联网之后世界产业技术第三次革命,其市场规模达到万亿级,前景可谓无限光明。根据 IDC 测算,到2021年将会有250 亿台设备联网,而物联网芯片作为万物互联的关键,目前

2019-11-21 16:48:03

,所以只能以旧工艺(16nm制程)制造A10处理器。除此之外,台积电还将独家代工重大变化的2017年版iPhone采用的A11处理器。据称A11芯片将采用10纳米FinFET工艺,最早有望于明年二季度

2016-07-21 17:07:54

坛上,其总经理兼联合CEO刘德音表示,他们早已制造出7nm的SRAM,并确认10nm将在2016年初试产,7nm则预期在2017年Q1开试。报道称,台积电非常高兴,因为终于超过英特尔了。他们还趁热预告

2016-01-25 09:38:11

只要将完成的方形 IC芯片剪下,便可送到封装厂做封装,至于封装厂是什么东西?就要待之后再做说明啰。 ▲ 各种尺寸晶圆的比较。纳米制程是什么? 三星以及台积电在先进半导体制程打得相当火热,彼此

2018-08-22 09:32:10

比如华为的麒麟芯片晶体管数量、功耗控制,芯片内总线连接?澎湃芯片的失败是不是它的研发团队在这些方面的不足?

2020-03-15 17:31:09

最近想用opa37做一个高频增益运放,该芯片增益带宽积可以达到63M,但实际应用时,输入为正负5V的方波,在放大两倍的情况下仅能允许1KHz带宽的正负10V方波,想问下各位大神前辈,我看芯片资料增益

2018-10-26 19:43:55

淀积厚度大于500A的NiAu层,用于欧姆接触和背反射;第二步,采用掩模选择刻蚀掉P型层和多量子阱有源层,露出N型层;第三步,淀积、刻蚀形成N型欧姆接触层,芯片尺寸为1×1mm2,P型欧姆接触为正方形

2018-08-31 20:15:12

高通最新中端芯片,台媒报道指高通的新款高端芯片骁龙875已在台积电投产,预计将在9月份发布,中国手机企业小米将首发这款芯片,小米似乎有意借这款芯片之势趁机从华为手里抢夺高端手机市场份额。骁龙875将是高通...

2021-07-28 06:39:35

据羊城晚报报道,近日中芯国际从荷兰进口的一台大型光刻机,顺利通过深圳出口加工区场站两道闸口进入厂区,中芯国际发表公告称该光刻机并非此前盛传的EUV光刻机,主要用于企业复工复产后的生产线扩容。我们知道

2021-07-29 09:36:46

高功率55流明光通量红色LED芯片

日立电线株式会社宣布开发高功率红色LED芯片 ,该芯片可提供最大55流明的光通量。此光通量是通过增加LED芯片尺寸和使用细线电极结

2010-01-11 09:26:12 857

857 近年来,芯片的发展进程始终严格遵守着“摩尔定律”,并有条不紊地进行着,直到14nm制造工艺的芯片在英特尔的实验室中被研制成功,业界开始有了担忧。

2012-03-13 14:36:51 27657

27657 出来的成品的品质也会有天壤之别。 下面就说一下具体有哪些区别: 1、芯片辐射功率等级的区别: 以厦门三安的芯片为例,S-23BBMUP-C*******,芯片尺寸为23X10mil,这个芯有4个辐射功率等级(@20mA),辐射功率越高,做出的灯珠越亮。 D2

2017-09-22 16:17:51 14

14 中兴不允许从美国企业购买芯片了,中兴董事长说这会让中兴进入休克状态,为何会如此,因为缺“芯”少魂,科技公司是没有活路的,据悉我国每年芯片进口花费是原油的两倍,去年进口了1万亿芯片,中国自己的“芯”去哪了?

2018-04-24 10:19:49 1105

1105 在GPU上训练卷积网络。谷歌团队实现了一个all-conv CIFAR-10网络,只涉及卷积和ReLU激活。谷歌编写了一个单独的随机梯度下降(SGD)更新步骤,并从一个纯Python循环中调用它,结果如表2所示。

2018-11-24 10:13:39 3153

3153 北京时间12月4日消息,英特尔在一项被称作自旋电子学的技术方面取得了进展,未来芯片尺寸可缩小5倍,能耗可降低至多30倍。

2018-12-04 14:10:54 2014

2014 适用于DA4580蓝牙芯片的QFN40芯片尺寸及推荐PCB封装资料免费下载

2021-02-02 08:00:00 0

0 近日,瑞士洛桑联邦理工学院(EPFL)教授Tobias Kippenberg团队开发出一种采用氮化硅衬底制造集成光子电路(光子芯片)技术,得到了创纪录的低光学损耗,且芯片尺寸小。相关研究在《自然—通讯》上发表。

2021-05-24 10:43:38 4570

4570 为基础半导体材料、制造设备和晶圆制造流程;中游一般指汽车芯片制造环节,包括智能驾驶芯片制造,辅助驾驶系统芯片制造、车身控制芯片制造等;下游包含了汽车车载系统制造、车用仪表制造以及整车制造环节。随着科技的不断发展和

2021-12-27 10:25:58 10412

10412 在计算焊盘坐标时,经常有 数据中指定的模具尺寸之间的混淆 板材和从中切割后的物理模具尺寸 晶片。虽然不需要物理芯片尺寸 对于引线键合目的,重要的是 了解两者之间的区别 影响 整体物理芯片尺寸。物理

2023-02-20 11:06:10 657

657 晶圆级芯片尺寸封装-AN10439

2023-03-03 19:57:27 5

5 合封芯片是一种芯片封装技术,它将多个芯片通过引线相互连接在一起,形成一个更大的芯片结构,以便更好地实现集成和减小芯片尺寸。合封芯片的优点是可以提高芯片的集成度和性能,同时可以减小芯片尺寸,从而提高芯片的功能密度和速度。

2023-04-11 14:09:04 1072

1072 FC-CSP 是芯片级尺寸封装(CSP)形式中的一种。根据J-STD-012 标准的定义口,CSP 是指封装体尺寸不超过裸芯片 1.2倍的一种封装形式,它通过凸块与基板倒装焊方式实现芯片与基板的电气

2023-05-04 16:19:13 2868

2868

圆片级芯片尺寸封装(WLCSP)是指在圆片状态下完成再布线,凸点下金属和焊锡球的制备,以及圆片级的探针测试,然后再将圆片进行背面研磨减薄

2023-05-06 09:06:41 2068

2068

在计算焊盘坐标时,数据手册中指定的芯片尺寸与从晶圆上切割后的物理芯片尺寸之间经常存在混淆。芯片的物理边缘不是引线键合的良好参考,因为整体芯片尺寸略有不一致。本应用笔记将简要讨论芯片尺寸、芯片方向、键合坐标以及如何计算物理芯片尺寸。MAX3970将作为示例。

2023-06-16 17:23:19 388

388 随着终端电子产品往多功用化、智能化和小型化方向开展,芯片尺寸越做越小,留给晶圆划片机的空间越来越小,既要保证足够的良品率,又要确保加工效率,这对晶圆划切刀片以及划片工艺是不小的应战。从划片刀自身

2022-10-19 16:56:49 5303

5303

电子发烧友网站提供《32位单片机晶圆级芯片尺寸封装(WLCSP).pdf》资料免费下载

2023-09-19 16:12:26 1

1 电子发烧友网站提供《32位单片机晶圆级芯片尺寸封装(WLCSP).pdf》资料免费下载

2023-09-19 14:23:37 0

0 麒麟a2芯片尺寸是多少 麒麟a2芯片尺寸是多少这个问题目前没有相关官方的报道,因此无法给出准确的回答。麒麟A2是华为旗下的音频芯片,麒麟A2芯片功耗相比上一代直接降低了50%,真正实现了高性能

2023-10-17 16:20:31 1086

1086 为了实现集成电路芯片的电通路,一般需要将芯片装配到在塑料或陶瓷载体上,这一过程可以称为CSP。CSP的尺寸只是略大于芯片,通常封装尺寸不大于芯片面积的1.5倍或不大于芯片宽度或长度的 1.2

2023-12-22 09:08:31 691

691

新版CoWoS技术使得台积电能制造出比传统光掩模(858平方毫米)大3.3倍的硅中介层。因此,逻辑电路、8个HBM3/HBM3E内存堆栈、I/O及其他小型芯片(Chiplet)最多可占据2831平方毫米的面积。

2024-04-29 09:18:53 47

47

电子发烧友App

电子发烧友App

评论