在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。

2015-04-07 15:30:53 2009

2009

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。通过调整PCB布局布线,能够很好地防范ESD.尽可能使用多层PCB,相对于双面PCB而言,地平面和电源平面,以及排列

2016-01-20 09:59:14 3293

3293 2016 年EDA IC设计技术都有哪些最新热点,PCB设计布线策略、走线技巧有哪些,PCB Layout及电路设计规范是怎样的,PCB设计抗静电方法设计如何,地线设计注意事项有哪些,机壳地与数字

2017-01-26 08:08:00 2003

2003 PCB设计时DDR线宽和阻抗是怎样确定下来的呢?让我们通一个具体的项目来学习一下。

2018-07-06 09:04:47 16923

16923

这期我带大家继续进行静电放电问题典型案例分析,前篇文章分别介绍了复位信号、DC-DC芯片设计问题引发的静电放电问题;这篇文章将介绍软件设计、PCB环路设计引发的静电放电问题;话不多说,还是通过两个案例展现给大家。

2023-12-11 10:03:46 489

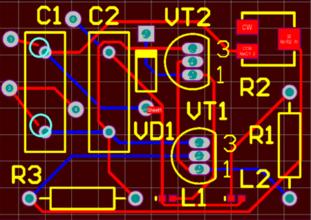

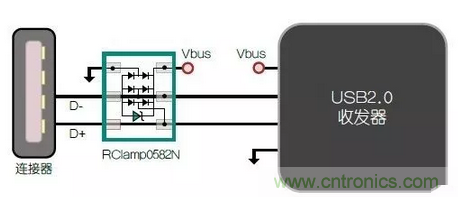

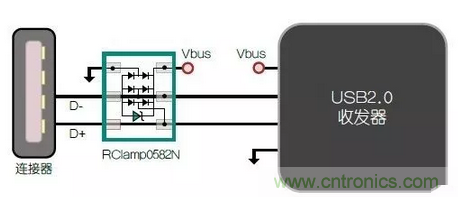

489 保护器件靠近输入端或者连接器,静电保护器件与被保护线之间的线路距离,应该设计得尽量短一些。

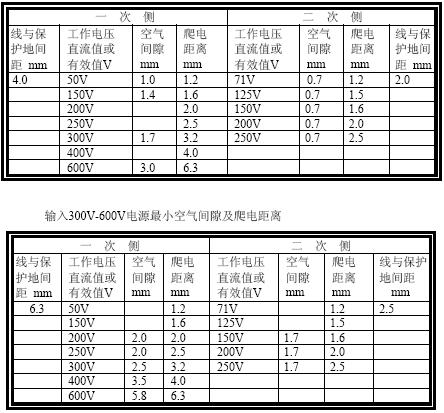

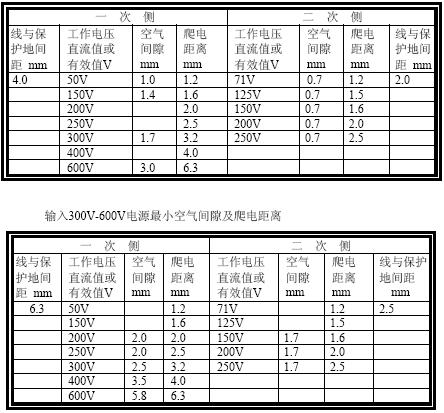

对于PCB设计来说,在容易发生静电放电的边缘,设置一定的隔离距离非常重要,对于机架类产品,每千伏的静电电压的击穿距离在

2023-05-12 12:02:17

保护器件靠近输入端或者连接器,静电保护器件与被保护线之间的线路距离,应该设计得尽量短一些。

对于PCB设计来说,在容易发生静电放电的边缘,设置一定的隔离距离非常重要,对于机架类产品,每千伏的静电电压的击穿距离在

2023-05-12 11:52:56

将静电保护器件靠近输入端或者连接器,静电保护器件与被保护线之间的线路距离,应该设计得尽量短一些。对于PCB设计来说,在容易发生静电放电的边缘,设置一定的隔离距离非常重要,对于机架类产品,每千伏的静电

2023-05-08 18:28:47

请问在PCB设计时用手动布线时为啥显示黄线且白色小线未消失,哪里错了,哪位大神回复一下。

2017-04-03 16:59:54

PCB设计中如何防止静电放电我们的手都曾有过静电放电(ESD)的体验,即使只是从地毯上走过然后触摸某些金属部件也会在瞬间释放积累起来的静电。我们许多人都曾抱怨在实验室中使用导电毯、ESD静电腕带

2013-01-29 10:38:41

紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100.对于顶层和底层表面都有元器件、具有很短连接线。来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成

2016-07-21 11:00:16

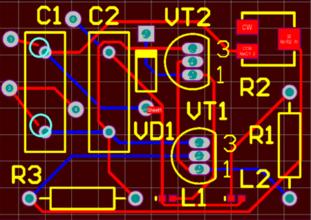

的PCB设计之电容量和耐压。2.RC充放电回路电路是以一个RC充放电回路示意图。假设PCB设计之电容器两端的初始电压为零,开关K与1端接通的瞬间,电源通过电阻R对PCB设计之电容器充电,此时PCB设计之

2019-08-13 10:49:30

PCB设计技术会对下面三种效应都产生影响: 1. 静电放电之前静电场的效应 2. 放电产生的电荷注入效应 3. 静电放电电流产生的场效应 但是,主要是对第三种效应产生影响。下面的讨论

2018-08-29 10:28:15

PCB电流与线宽有何关系?PCB设计铜铂厚度、线宽和电流有何关系?PCB设计时铜箔厚度,走线宽度和电流有何关系?

2021-09-30 08:28:23

正向偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进行防范。 在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB

2018-11-26 11:09:39

让我们面对现实吧。人都会犯错,PCB设计工程师自然也不例外。与一般大众的认知相反,只要我们能从这些错误中学到教训,犯错也不是一件坏事。下面将简单地归纳出在进行PCB设计时的一些常见错误。 缺乏

2018-09-17 17:43:59

PCB设计的可制造性分为哪几类?PCB设计时考虑的内容有哪些?

2021-04-21 06:16:30

PCB设计时铜箔厚度,走线宽 度和电流的关系

2014-09-08 08:37:10

PCB设计时铜箔厚度、走线宽度和电流有何关系?PCB设计要考虑哪些因素?

2021-10-09 06:44:11

静电放电是普遍存在的自然现象(当充有电荷的物体靠近或接触一个导体时,电荷就要发生转移,这就是静电放电)。无处不在的影响着电子产品,是一种危害程度极高的电磁能量。只有提高电子产品抗静电能力水平,才能

2018-01-03 10:22:07

LED死灯有很多种原因,但由于LED本身抗静电能力弱,因此,大部分死灯都是由于静电击穿造成的。LED内部的PN结在应用到电子产品的制造、组装筛选、测试、包装、储运及安装使用等环节,难免不受静电

2013-06-03 12:57:51

,然后又重新烧写程序就好了。 如果又遇到静电又会丢失 Flash内容…………结论是 CC2540抗静电能力太差了, 不知道有没有什么方法可以改善? 或者 CC2541会不会好一点?

2016-04-27 10:46:56

防静电咨讯网上了解了很可能是静电放电的原因,对于手机,在正常使用下,手机不接地,加之夏季天气会很干燥,人体静电自然多一些,上述静电现象很可能是这个原因,合成纤维衣服与皮肤相互摩擦而产生静电,静电的电压

2013-03-15 11:25:19

pciex2进行PCB设计时,收发数据线需要做等长么?

2016-02-15 15:12:40

抗静电为什么是三极管优于MOS?那么三极管和MOS管抗静电?接下来就跟着深圳比创达EMC小编一起来看下吧!

首先要了解电子元件的特性,三极管是电流驱动元件,MOS管是电压驱动元件,为什么说MOS管用

2023-09-25 10:56:07

什么是静电放电?什么是电迁移?

2021-06-17 07:34:44

—05 单电源运放电路实例从零学运放—06 运放中器件介绍&音频功放电路从零学运放—07 理想晶体管-运放从零学运放—08 积分电路_开关电源等一些电路讲解从零学运放—09 电容电感PCB设计

2017-04-08 16:44:35

,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100。对于顶层和底层表面都有元器件、具有很短连接线。 来自人体、环境甚至电子设备内部的静电对于精密

2018-08-27 15:54:33

微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的 IC。单次静电放电事件就可以将 PCB 摧毁。抗静电放电设计只要错失一步就可能意味着

2020-01-03 09:15:31

一、术语及定义 1、静电:物体表面过剩或不足的静止的电荷. 2、静电场:静电在其周围形成的电场. 3、静电放电:两个具有不同静电电位的物体,由于直接接触或静电场感应引起两物体间的静电电荷的转移.静电

2019-07-02 06:42:48

请问各位大神,在静电放电抗扰度试验中,静电放电发生器的直流高压电源、充电电阻、放电电阻、储能电容器、放电开关、等等的各项具体要求是什么?比如功率,电流,耐压值什么的。希望大家可以帮助我这个小菜鸟,我是刚刚开始学习EMC。谢谢!!!

2013-12-22 15:47:30

在进行PCB设计时,需要遵守哪些原则?在设计RF布局时,需要满足哪些原则?

2021-04-21 06:50:45

多层板PCB设计时的EMI解决之道

2012-08-06 11:51:51

。本文介绍了手机静电放电测试的要求和方法,总结分析了手机静电放电抗扰度试验的主要失效现象和模式, 可供手机静电放电抗扰度试验及提高手机抗静电能力设计时参考。

2019-07-25 06:51:33

本帖最后由 jinyi7016 于 2019-9-5 14:13 编辑

电阻屏如何抗静电:接触6kV,空间8kV

2019-09-05 09:32:41

随着半导体制程技术的不断演进,以及集成电路大量的运用在电子产品中,静电放电已经成为影响电子产品良率的主要因素。美国最近公布因为静电放电而造成的国家损失,一年就高达两百多亿美金,而光是电子产品部份

2019-07-25 06:45:53

排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100。对于顶层和底层表面都有元器件、具有很短连接线。 来自人体、环境甚至电子设备内部的静电对于精密的半导体

2018-09-17 17:34:36

μModule电源稳压器LTM4644的抗静电等级多少?能耐多少kV的静电电压呢?

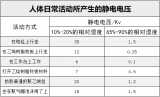

人体接触静电电压值(HBM)多少?

2024-01-05 07:10:08

运放电路PCB设计技巧

2020-12-29 07:50:05

尽管印刷线路板(PWB,通常也称之为PCB)的设计会对下述三种效应都产生影响,但是主要是对第三种效应产生影响。

1. 静电放电之前静电场的效应2. 放电产生的电荷注入

2010-06-12 15:43:49 58

58 介绍采用Protel99 SE进行射频电路PCB设计的流程。为保证电路性能,在进行射频电路PCB设计时应考虑电磁兼

2006-04-16 22:17:22 1352

1352 PCB设计时铜箔厚度,走线宽度和电流的关系不同厚度,不同宽度的铜箔的载流量见下表:

2007-12-12 14:30:28 14675

14675

PCB设计时应该遵循的规则

1) 地线回路规则:

环路最小

2007-12-12 14:48:15 1096

1096

PCB设计时防范ESD的方法

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例

2009-11-18 14:10:29 371

371 本文介绍了手机静电放电测试的要求和方法, 总结分析了手机静电放电抗扰度试验的主要失效现象和模式, 可供手机静电放电抗扰度试验及提高手机抗静电能力设计时参考。

2011-10-20 10:02:18 3375

3375 PCB设计时阻抗计算的板材常识学习,介电常数是个重要的参数,在阻抗计算公式里,它对阻抗是有较大影响的

2011-11-09 16:22:57 3737

3737

ESD 是代表英文ElectroStatic Discharge 即静电放电的意思。ESD 是本世纪中期以来形成的以研究静电的产生与衰减、静电放电模型、静电放电效应如电流热(火花)效应(如静电引起的着火与

2011-11-25 14:05:43 125

125 在深次微米半导体製程中,由于元件尺寸微缩,元件的静电放电(ElectrostaticDischarge,ESD) 耐受度相对变差,因此静电放电防护设计在IC 设计时即必需被加入考量 [1]。通常商用IC 的静电放

2011-11-30 09:55:40 51

51 由于CMOS器件静电损伤90%是延迟失效,对整机应用的可靠性影响太大,因而有必要对CMOS器件进行抗静电措施。本文描述了CMOS器件受静电损伤的机理,从而对设计人员提出了几种在线路设

2012-02-02 10:53:26 54

54 PCB设计时会碰到的各种问题集合 及其解答

2016-09-02 16:54:40 0

0 PCB设计时铜箔厚度走线宽度和电流的关系,有参考价值

2016-12-16 22:04:12 0

0 静电放电原理

2016-12-30 15:22:44 0

0 PCB设计时铜箔厚度,走线宽度和电流的关系

2017-01-28 21:32:49 0

0 详细介绍PCB设计时需要遵守的规则

2017-09-18 14:08:17 0

0 ,光衰加重,甚至出现死ce灯现象,静电对LED品质有非常重要的影响。LED的抗静电指标绝不仅仅是简单地体现它的抗静电强度,LED的抗静电能力与其漏电值、整体可靠性有很大关系,更是一个整体质素和可靠性的综合体现。因为往往抗静电高的LED,它的光特性、电特性

2017-10-12 18:00:32 10

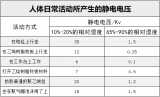

10 一种普通的物理过程。静电产生不仅取决于材质,而且在相当程度上还与外界因素有关。运动摩擦可引起静电放电效应。以下是我们日常生产活动中所产生的静电电压; 3、LED抗静电与衬底材质 摩擦产生静电的强弱与材质的电阻率有关,电

2017-11-14 10:19:35 7

7 一、术语及定义 1、静电:物体表面过剩或不足的静止的电荷. 2、静电场:静电在其周围形成的电场. 3、静电放电:两个具有不同静电电位的物体,由于直接接触或静电场感应引起两物体间的静电电荷的转移.静电

2017-11-23 05:45:51 1087

1087 微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。这些祸害是隐秘的杀手,特别容易攻击敏感的IC。单次静电放电事件就可以将PCB送入地狱。抗静电放电设计只要错失一步就可能意味着延误上市时间、影响开发进度,以及激怒客户。在某些高压力情况下,甚至意味着你的饭碗不保。

2018-06-05 15:40:00 3778

3778

本文主要介绍的是pcb开窗,首先介绍了PCB设计中的开窗和亮铜,其次介绍了如何实现PCB走线开窗上锡,最后阐述了PCB设计怎样设置走线开窗的步骤,具体的跟随小编一起来了解一下。

2018-05-04 15:37:30 34498

34498

汽车电子车联网的普及,敏感器件的大量使用,要求汽车级的抗静电ESD元件,抗静电能力高达30KV,抗浪涌能力也是越高越好。现在市面上的ESD,很多还是按消费级标准8KV接触 15KV空气静电生产,没法满足汽车电子要求标准。

2018-06-01 08:07:00 5

5 PCB设计时的6个常见错误 让我们面临现实吧。人都会出错,PCB设计工程师天然也不例外。和一般大众的认识相反的是,只要我们在这些错误中能够学习到教训,出错不见得是一件坏事。下面将简朴地归纳出在进行

2018-06-05 11:42:22 2733

2733 尽可能使用多层PCB,相对于双面PCB而言,地平面和电源平面,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的 1/10到1/100.尽量地将每一个信号层都紧靠一个电源层或地线层。对于顶层和底层表面都有元器件、具有很短连接线以及许多填充地的高密度PCB,可以考虑使用内层线。

2019-08-17 17:35:00 1817

1817 PCB设计中怎样消除反射噪声

2019-08-17 20:31:00 2446

2446

PCB设计技术会对下面三种效应都产生影响:

1. 静电放电之前静电场的效应。

2. 放电产生的电荷注入效应。

3. 静电放电电流产生的场效应。

2019-08-01 15:36:51 1007

1007

PCB设计中,对于静电的防护,一般采用隔离、增强单板静电免疫力和采用保护电路三项措施来进行设计。

2019-05-24 15:49:57 16325

16325 在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时怎样来考虑这个问题?

2019-06-21 17:03:47 6432

6432 PCB设计时对于双面都有的元件的PCB,较大较密的IC,插件元件放在板的顶层,底层只能放较小的元件和管脚数少且排列松散的贴片元件。

2019-08-16 15:20:00 3063

3063 在pcb板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。

2020-04-01 17:40:18 1760

1760 在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。

2019-11-11 17:34:38 2974

2974 PCB设计时记住148个检查项目,提升你的效率!

2019-08-20 08:42:08 3177

3177 在pcb板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。

2019-08-22 11:02:49 449

449 在PCB设计时,芯片电源处旁路滤波等电容应尽可能的接近器件,典型距离是小于3MM。

2019-08-27 11:38:31 444

444 为了保证线路板设计时的质量问题,在PCB设计的时候,要注意PCB图布线的部分是否符合要求。

2019-09-02 10:12:36 2190

2190 EAGLE CAD怎样做更简单的PCB设计

2019-09-10 17:51:32 8049

8049

微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的IC。单次静电放电事件就可以将PCB摧毁。

2019-12-13 16:36:32 4102

4102

PCB设计技术会对下面三种效应都产生影响:

1.静电放电之前静电场的效应

2.放电产生的电荷注入效应

3.静电放电电流产生的场效应

2019-12-31 15:48:50 951

951 了手机静电放电测试的要求和方法,总结分析了手机静电放电抗扰度试验的主要失效现象和模式,可供手机静电放电抗扰度试验及提高手机抗静电能力设计时参考。

2020-07-10 10:29:00 6

6 来源:罗姆半导体社区 微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的 IC。单次静电放电事件就可以将 PCB 摧毁。抗静电放电

2022-11-15 16:23:37 964

964 在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时怎样来考虑这个问题?

2020-11-12 17:09:06 4684

4684 ,光衰加重,甚至出现死灯现象,静电对LED品质有非常重要的影响。LED的抗静电指标绝不仅仅是简单地体现它的抗静电强度,LED的抗静电能力与其漏电值、整体可靠性有很大关系,更是一个整体质素和可靠性的综合体

2021-07-15 15:40:27 854

854 微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。这些祸害是隐秘的杀手,特别容易攻击敏感的IC。单次静电放电事件就可以将PCB送入地狱。抗静电放电设计只要错失一步就可能意味着延误

2022-02-10 11:48:27 2

2 一站式PCBA智造厂家今天为大家讲讲pcb板设计时应注意的问题?PCB设计时应满足的要求。 PCB设计如何考虑焊接工艺性? 在PCB设计中,电源线、地线及导通孔的图形设计中,需要从以下这些方面考虑

2022-11-25 09:13:05 480

480 在干燥的环境下,人体静电(ESD)的电压很容易超过6~35Kv,当用手触摸电子设备、PCB或PCB上的元器件时,会因为瞬间的静电放电,而使元器件或设备受到干扰,甚至损坏设备或PCB上的元器件。

2023-07-04 09:07:44 1004

1004

在pcb板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。

2023-07-20 14:52:15 411

411 静电放电的产生有两个基本条件,一. 是电荷的积累,电荷的积累是前提,然后是“跨接”,电荷的剧烈流动就是放电。所以从这两个方面就行控制就能有效地防护静电放电的产生。

2023-09-05 11:08:19 479

479

三极管和MOS管抗静电?|深圳比创达EMC

2023-09-25 10:54:53 343

343

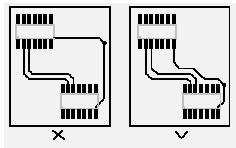

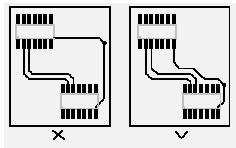

PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查和返工所带来不必要的成本。在PCB设计中,不但需要在静电薄弱电路增加静电抑制器件,还要克服放电电流产生的电磁干扰(EMI)电磁场效应。

2023-09-26 10:57:16 650

650

为什么PCB设计时要考虑热设计? PCB(Printed Circuit Board)设计是指通过软件将电路图转化为PCB布局图,以导出一个能够输出到电路板的文件。在进行电路设计时,我们需要考虑到

2023-10-24 09:58:27 331

331 PCB设计时铜箔厚度,走线宽度和电流的关系

2022-12-30 09:20:39 15

15 PCB设计时铜箔厚度,走线宽度和电流的关系

2023-03-01 15:37:46 13

13 在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。

2023-11-20 15:28:27 158

158 静电放电发生器原理 静电放电发生器的主要用途 静电发生器怎么使用 静电放电发生器(Electrostatic Discharge Generator)是一种用于模拟和测试电子器件和系统在静电放电

2023-11-23 10:07:22 666

666 在具体PCB设计中,如电场或磁场占主导地位,应用方法7和8就可以解决。然而,静电放电一般同时产生电场和磁场,这说明方法7将改善电场的抗扰度,但同时会使磁场的抗扰度降低。

2023-12-14 16:20:29 61

61 最容易在导电材料上产生,因此选择具有良好防静电性能的材料是防止静电放电损伤的基础。常见的防静电材料包括抗静电塑料、抗静电硅胶等,这些材料能够有效吸收和分散静电,减小静电放电的能量。 2. 使用静电消除器:静电消除器是

2024-01-03 11:43:27 229

229

电子发烧友App

电子发烧友App

评论