Cadence宣布业内首个DDR4 Design IP解决方案在28纳米级芯片上得到验证

2012-09-10 09:53:24 1403

1403 赛灵思的20纳米产品以备受市场肯定的28纳米制程突破性技术为基础,提供超越一个技术世代的系统效能、功耗和可编程系统整合度,继续超越下一代!

2012-12-03 09:48:01 876

876 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,该版本将复杂SoC的低功耗验证效率提高了30

2013-05-14 10:31:40 1832

1832 Cadence系统芯片开发工具已经通过台积电(TSMC) 16纳米 FinFET制程的设计参考手册第0.1版与 SPICE 模型工具认证,客户现在可以享用Cadence益华电脑流程为先进制程所提供的速度、功耗与面积优势。

2013-06-06 09:26:45 1236

1236 艾迈斯欧司朗与创迈思联合发布演示方案,实现OLED屏下超高安全级别人脸认证 • 发布完整的智能手机集成解决方案联合演示,包括OLED屏下方案; • 解决方案包括结合了隐蔽

2022-06-28 11:46:04 797

797

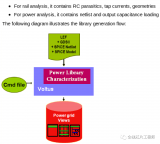

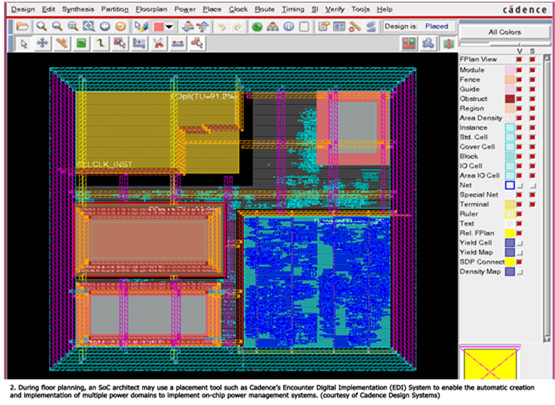

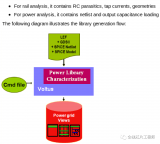

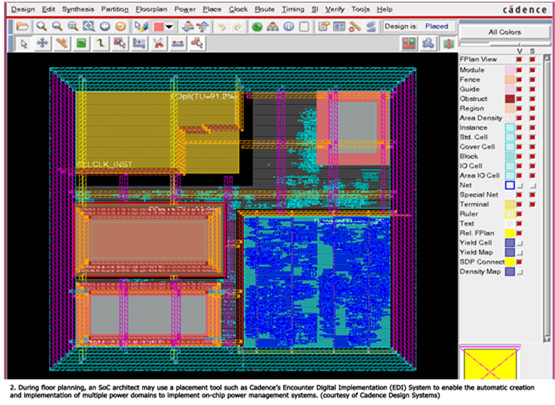

Cadence功耗分析首先需生成power grid library

2023-09-06 09:47:50 859

859

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,全球领先的晶圆厂之一中国中芯国际[0.40 2.56%]集成电路制造有限公司(SMIC)推出一款采用Cadence Encounter数字技术和SMIC

2012-04-11 09:44:30 825

825 Cadence设计系统公司发布了Cadence Allegro系统互连设计平台针对印刷电路板(PCB)设计进行的全新产品和技术增强。改进后的平台为约束驱动设计提供了重要的新功能,向IC、封装和板

2018-11-23 17:02:55

。” Cadence推出的RFSiP套件为无线通信应用的RFSiPs设计提供了自动化和加速设计流程的最新产品和技术。它同时提供了基于802.11b/g无线局域网设计的成熟的SiP实施方法,能够低风险地实现

2008-06-27 10:24:12

Cadence仿真流程Cadence仿真流程[/hide][此贴子已经被作者于2009-8-16 13:47:51编辑过]

2009-08-16 13:47:03

授权使用正确的低功耗分析和最优化引擎,这些功能要求集成在整个设计流程中。此外,在65纳米芯片设计中,约有50%的设计工作是混合信号设计。传统的模拟设计流程与数字工作处于完全隔离的状态,如何把模拟和数字

2019-05-20 05:00:10

数据透传是选择低功耗WiFi模块还是低功耗蓝牙模块好?

2021-01-04 06:55:35

物联网的兴起带动越来越多的公司选用无线互联产品,在无线互联中低功耗蓝牙(BLE)是不可缺少的用来支持相互连接的产品之一,因为低功耗蓝牙无需网关就可以直接与智能终端通信,有比较好的人机交互体验,特别是蓝牙MESH发布,可以让更多结点在同一个网络互通。 许多工程师不清楚如何选型;有什么技巧吗?

2021-03-06 08:22:49

本帖最后由 eehome 于 2013-1-5 10:02 编辑

数字语音解码器的低功耗设计方案

2012-08-20 12:50:40

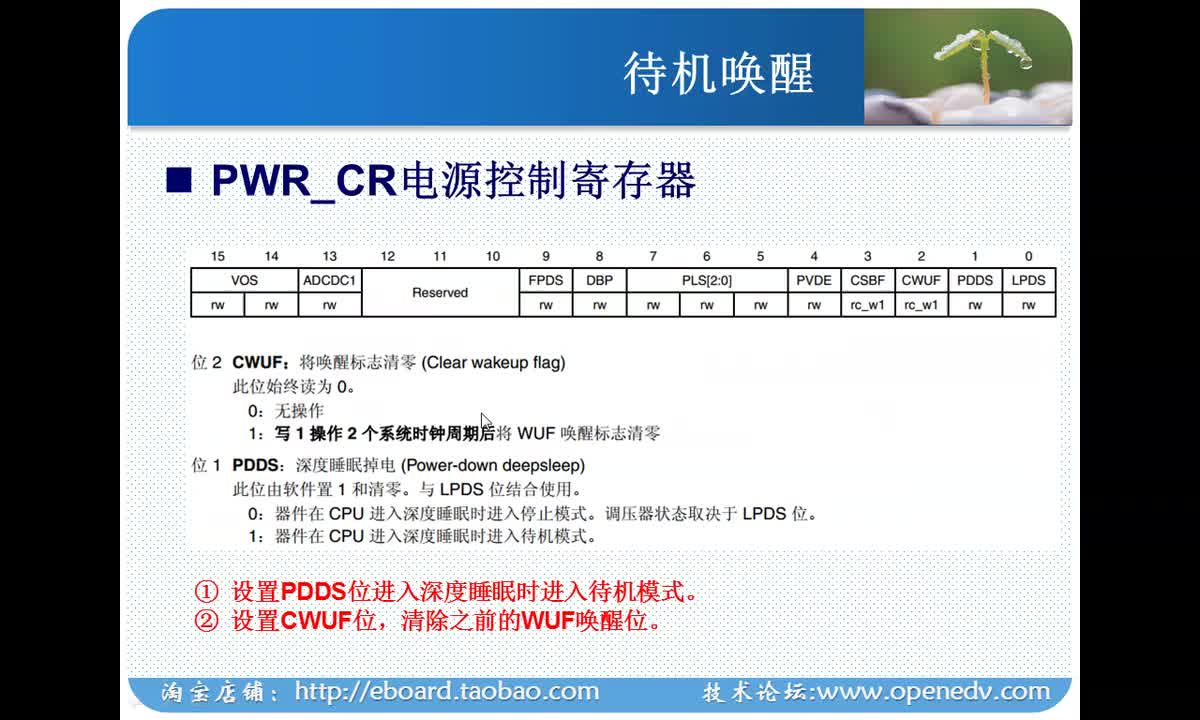

程序使用定时唤醒采样方式,每隔一段时间唤醒,进行AD采样。问题在于,如果不使用内部2.5V基准电压,进入低功耗时候,电流在20uA左右;使用内部2.5V基准电压,进入低功耗前关闭(ADC12CTL0

2018-06-21 14:54:10

` Nordic发布了nRF8002低功耗蓝牙单芯片解决方案,成本更低,功耗更低,更简单应用于无线蓝牙智能标签和配件(如手链,坠子,钥匙扣,小玩具和臂章等)。 要配置µBlue™ nRF8002

2012-03-26 14:20:38

Port Pins,它说“有时在数字输入时将数字输入配置为模拟输入是适当的和可能的必须进入低功耗状态。“我不太理解这一点,关于数字输入必须如何进入低功耗状态。”请你阐述一下这一点好吗?如果有一些例子的话会很有帮助的。谢谢!

2020-04-30 09:25:33

,通过发行所谓的“虚拟资产”、“数字资产”、“虚拟货币”等方式吸收资金,已经侵害到公众的合法权益了。五部委联合发布风险提示,让无数人拍手叫好!有网友甚至吐出心声:确实该整顿了,这些打着“给大众迅速赚大钱

2018-08-29 13:36:47

今天更新一篇数字IC低功耗设计方法总结,内容参考的是郭炜老师的书:《SoC设计方法与实现(第3版)》,希望能给大家带来帮助~

2021-07-29 06:38:58

芯片设计解决方案供应公司微捷码(Magma)设计自动化有限公司近日宣布,已和专为消费性应用提供超低功耗65纳米FPGA(现场可编程门阵列)技术的先驱者SiliconBlue科技公司正式签定技术合作

2019-07-26 07:29:40

现在电子产品一般都有要求低功耗,不同的MCU,进入低功耗的处理流程可能不一样,但是大致的流程还是一样。现对MCU进入低功耗的处理流程大致如下:(1)关闭MCU之外的外设电源,例如:RS485、CAN

2021-11-01 08:10:03

一半,而性能提高两倍。通过选择一个高性能低功耗的工艺技术,一个覆盖所有产品系列的、统一的、可扩展的架构,以及创新的工具,赛灵思将最大限度地发挥 28 纳米技术的价值, 为客户提供具备 ASIC 级功能

2019-08-09 07:27:00

为什么需要低功耗设计?如何实现数字IC低功耗的设计?

2021-11-01 06:37:46

单位。中科院计算技术研究所:负责设计验证及测试综合 SIG,与中科鉴芯(北京)科技有限责任公司联合发布故障仿真器 v1.0;中科院微电子研究所:负责器件模型与参数提取 SIG、工艺模型及 PDK SIG

2022-06-24 15:17:14

2月19日,在新华社新媒体中心与搜狗公司战略合作签约仪式上,搜狗公司与新华社新媒体中心联合发布了全球首个站立式AI合成主播,新的AI合成主播将从过去的“坐着播新闻”升级成结合肢体动作的“站立

2019-02-25 09:28:26

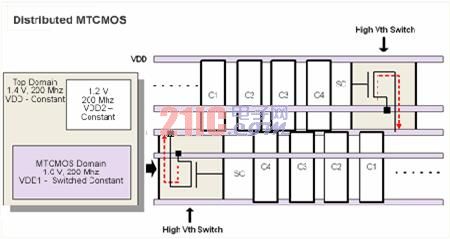

本资料是关于如何采用低功耗28nm降低系统总成本

2012-07-31 21:25:06

Cadence 仿真流程:第一章 在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方

2008-07-12 08:56:05 0

0

低功耗数字VLSI设计:概览:

2009-07-25 16:44:42 0

0 cadence 视频教程 (第28课):adence SPB 15.7 视频教程,手把手教你学习cadence软件使用方法。本套视频教程是于博士信号完整性研究网于争博士主讲。从一个工程师的角度出发讲解软件的操

2009-09-16 19:02:12 0

0 Tensilica 日前宣布与Cadence 合作,根据Tensilica 的330HiFi 音频处理器和388VDO 视频引擎,为其多媒体子系统建立一个通用功耗格式(CPF)的低功耗参考设计流程。Cadence 和Tensilica公司的工

2009-12-04 13:54:39 32

32 安富利与赛普拉斯联合发布Spartan-3A FPGA评估套件升级版

安富利公司旗下之安富利电子元件部 (Avnet Electronics Marketing) 美洲业务区与赛普拉斯半导体公

2008-09-25 07:55:47 687

687 2009年3月4日,Cadence设计系统公司今天宣布生物指纹安全解决方案领先厂商UPEK®, Inc.已经整合其设计流程,并选择Cadence®作为其全芯片数字、模拟与混合信号设计的

2009-03-05 12:14:18 519

519

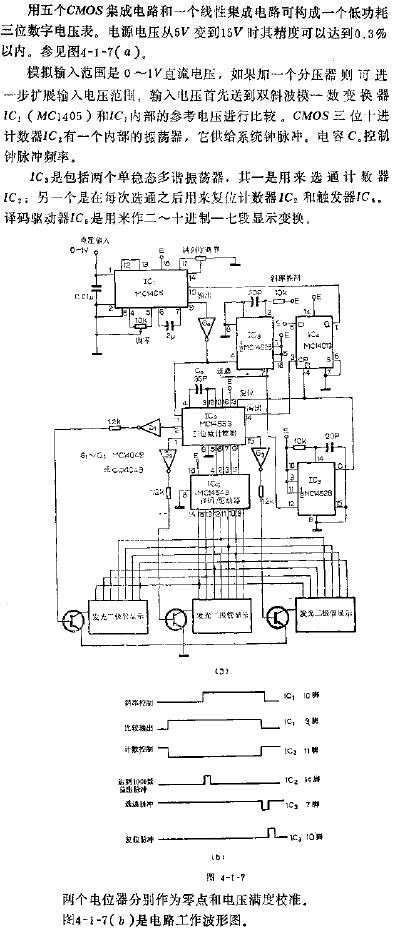

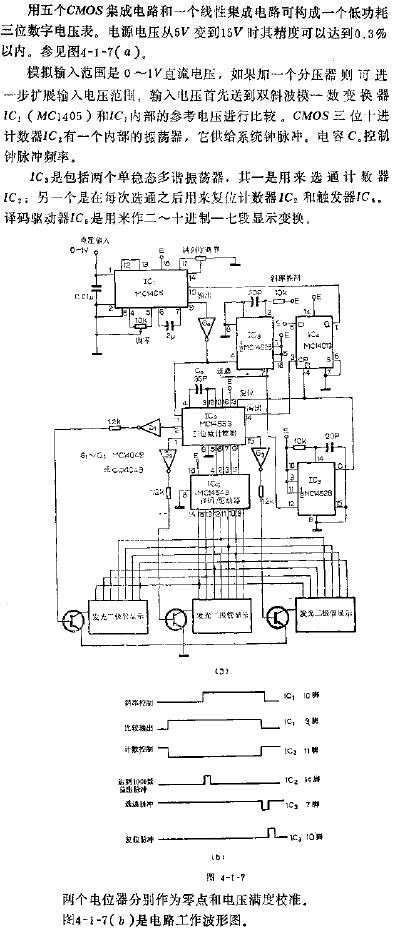

低功耗数字电压表

2009-04-10 10:15:58 585

585

中芯国际采用Cadence DFM解决方案用于65和45纳米 IP/库开发和全芯片生产

Cadence 模型化的 Litho Physical 和 Litho Electrical

2009-10-19 17:48:11 461

461 中芯国际(SMIC)和Cadence 共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

完全集成的能效型流程令快速、轻松地设计低功耗尖端器件成为可能

2009-10-31 07:48:01 1228

1228 中芯国际(SMIC)和Cadence共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

全球电子设计创新领先企业Cadence设计系统公司今天宣布推出一款全面的低功耗设计流程,面向

2009-11-04 17:05:17 589

589 SIG发布新版低功耗蓝牙规范

蓝牙技术联盟(Bluetooth Special Interest Group,SIG)日前推出采用低功耗版本蓝牙核心规范4.0版本的升级版蓝牙低功耗无线技术,将为具备低成本、

2009-12-30 08:52:37 1153

1153 台积电与联电大客户赛灵思合作28纳米产品

外电引用分析师资讯指出,联电大客户赛灵思(Xilinx)3月可能宣布与台积电展开28纳米制程合作;台积电28纳米已确定取得富

2010-01-19 15:59:55 1058

1058 统一工艺和架构,赛灵思28纳米FPGA成就高性能和低功耗的完美融合

赛灵思公司(Xilinx)近日宣布,为推进可编程势在必行之必然趋势,正对系统工程师在全球发布赛灵思

2010-03-02 08:48:51 576

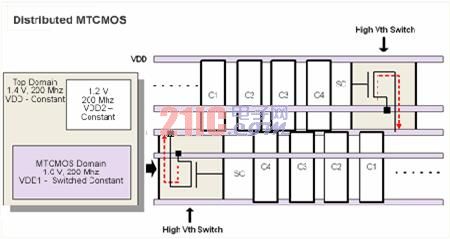

576 根据贯穿整个IC实现流程的集成化低功耗设计技术策略

降低功耗是现代芯片设计最具挑战性需求之一。采用单点工具流程时,往往只有到了设计流程后期阶段才会去考虑降

2010-04-21 10:54:28 651

651

微捷码(Magma®)设计自动化有限公司日前宣布,一款经过验证的支持Common Platform™联盟32/28纳米低功耗工艺技术的层次化RTL-to-GDSII参考流程正式面市。

2011-01-26 09:44:09 894

894 本文基于IEEEl801标准Uni-fied Power Format(UPF),采用Synopsys和Mentor Graphics的EDA工具实现了包括可测性设计在内的“从RTL到GDSII”的完整低功耗流程设计。本论文第1部分描述了低功耗技术和术语

2011-03-11 11:33:55 1621

1621

即将上市的这种新流程支持Cadence的硅实现方法,专注于独一无二且普遍深入的设计意图、提取与从RTL到GDSII,然后到封装。硅实现是EDA360构想的一个关键组成部分。

2011-06-28 09:44:23 455

455 三星电子有限公司使用Cadence统一数字流程,从RTL到GDSII,成功实现了20纳米测试芯片的流片

2011-07-27 08:47:49 967

967 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence® Virtuoso®统一定制/模拟(IC6.1)以及Encounter®统一数字流程生产其混合信号芯片。

2011-09-27 11:06:26 1483

1483 本白皮书介绍了有关赛灵思 28 nm 7 系列 FPGA 功耗的几个方面,其中包括台积电 28nm高介电层金属闸 (HKMG) 高性能低功耗(28nm HPL 或 28 HPL)工艺的选择。 本白皮书还介绍了 28 HPL 工艺提供

2012-03-07 14:43:44 41

41 Cadence 设计系统公司日前宣布,汽车零部件生产商Denso公司在改用了Cadence定制/模拟与数字流程之后,在低功耗混合信号IC设计方面实现了质量与效率的大幅提升。将Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 该14纳米产品体系与芯片是ARM、Cadence与IBM之间在14纳米及以上高级工艺节点上开发系统级芯片(SoC)多年努力的重要里程碑。使用FinFET技术以14纳米标准设计的SoC能够大幅降低功耗。 这

2012-11-16 14:35:55 1270

1270 Cadence设计系统公司日前宣布Avago Technologies在大型28纳米网络芯片设计中使用其EDI系统,大幅度加快设计进度,提高了工程效率。Avago实现1GHz的性能,比之前所用软件设计的芯片提高57%。

2013-02-04 09:17:00 1150

1150

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)今天宣布,历经广泛的基准测试后,半导体制造商联华电子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence® “设计内”和“签收”可制造性设计(DFM)流程对28纳米设计进行物理签收和电学变量优化。

2013-07-18 12:02:09 905

905 日前,联华电子与SuVolta公司宣布联合开发28纳米工艺技术,该工艺将SuVolta的SuVolta的Deeply Depleted Channel晶体管技术集成到联华电子的28纳米High-K/Metal Gate高效能移动工艺。

2013-07-25 10:10:52 1049

1049 全球电子创新设计Cadence公司与上海华力微电子,15日共同宣布了华力微电子基于Cadence Encounter数字技术交付55纳米平台的参考设计流程。华力微电子首次在其已建立55纳米工艺上实现了从RTL到GDSII的完整流程。

2013-08-16 11:08:11 1383

1383 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)与上海华力微电子有限公司,今天共同宣布华力微电子基于Cadence ® Encounter® 数字技术交付出55纳米平台的参考设计流程。

2013-08-16 12:02:40 1445

1445 中芯国际新款40纳米 Reference Flow5.1结合了最先进的Cadence CCOpt和GigaOpt工艺以及Tempus 时序签收解决方案, 新款RTL-to-GDSII数字流程支持Cadence的分层低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839 ® 数字工具流程,应用于其新款SMIC Reference Flow 5.1,一款为低功耗设计的完整的RTL-GDSII 数字流程。Cadence流程结合了先进功能,以帮助客户为40纳米芯片设计提高功率、性能和面积。

2013-09-05 16:50:41 748

748 9月24日——全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,Silicon Labs采用完整的Cadence® 混合信号低功耗设计流程,使其最新款节能型

2013-09-25 09:59:51 913

913 美国加州圣何塞,2014年9月30日 ─ 全球知名的电子设计创新领导者Cadence设计系统公司(NASDAQ: CDNS)今日宣布其丰富的IP组合与数字和定制/模拟设计工具可支持台积电全新的超低功耗(ULP)技术平台。

2014-10-08 19:24:35 906

906 详细介绍Cadence的仿真流程

有需要的朋友下来看看

2015-12-08 14:49:11 0

0 2016年3月22日,中国上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10纳米 FinFET工艺的数字、定制/模拟和签核工具通过台积电(TSMC)V1.0设计参考手册(DRM)及SPICE认证。

2016-03-22 13:54:54 1026

1026 继广州车展正式宣布YunOS for Car品牌升级为YunOS Auto后,此次泰国发布会上,YunOS TV也正式升级亮相。12月8日,YunOS携手Cybo在泰国曼谷召开联合发布会。此次与Cybo的合作,意味着YunOS正式进军海外。

2016-12-09 09:37:11 845

845 基于CCopt引擎的SMIC40nm低功耗工艺CortexA9的时钟树实现,该文基于 SMIC 40nm 低功耗工艺的 ARM Cortex A9 物理设计的实际情况,详细阐述了如何使用 cadence 最新的时钟同步优化技术,又称为 CCopt 技术来实现统一的时钟树综合和物理优化。

2017-09-28 09:08:51 7

7 台积电业务开发副总经理金平中指出,台积电的超低功耗平台包括55纳米超低功耗技术、40纳米超低功耗技术、22纳米超低功耗/超低漏电技术等,都已经被各种穿戴式产品和物联网应用采用,同时,台积电也把超低功耗

2017-12-11 15:03:29 1409

1409 浪潮与科大讯飞IPF2018联合发布超强AI系统AI Booster 4月26日,在2018浪潮云数据中心合作伙伴大会(IPF2018)上,浪潮与科大讯飞联合发布了面向于语音识别、翻译等AI

2018-05-06 05:03:00 4967

4967 双方联合推出基于华润上华110纳米嵌入式闪存技术平台的低功耗物联网完整解决方案。

2018-08-15 08:52:50 3822

3822 Cadence Low-Power Solution是用于低功耗芯片的逻辑设计、验证和实现的完全集成的、标准化的流程,将领先的设计、验证和实现技术与Si2Common Power Format

2018-11-13 11:30:03 1357

1357 近日,华虹集团旗下中国领先的12英寸晶圆代工企业上海华力与全球IC设计领导厂商---联发科技股份有限公司(以下简称“联发科技”)共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一---基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2018-12-12 15:15:01 2029

2029 12月11日,华虹集团旗下中国领先的12英寸晶圆代工企业上海华力与全球IC设计领导厂商---联发科技股份有限公司(以下简称“联发科技”)共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一---基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2018-12-14 15:47:30 3159

3159 华虹集团旗下中国领先的12英寸晶圆代工企业上海华力与全球IC设计领导厂商---联发科技股份有限公司(以下简称“联发科技”)共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一---基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2019-01-01 15:13:00 3780

3780 华虹集团旗下上海华力与联发科技股份有限公司共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一——基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2019-01-07 14:15:45 3224

3224 中国移动、中国电信、中国联通三家运营商联合发布了《开放参考设计理念、进展及未来演进策略》白皮书

2019-06-27 17:14:11 3991

3991 采用极紫外(EUV)光刻技术的Cadence 数字全流程解决方案已通过Samsung Foundry 5nm早期低功耗版(5LPE)工艺认证。

2019-07-11 16:36:47 3436

3436 在HUAWEI CONNECT2019期间,华为与北京中安星云软件技术有限公司(以下简称“中安星云”)联合发布了融慧智简大数据安全解决方案,依托协议解析和大数据技术为用户提供动态可视的安全防护能力。

2019-10-12 17:09:47 567

567 和知名服务商、企业代表共聚一堂,共同探讨“未来智造发展的新模式、新平台、新生态”和企业数字化转型实践。 在现场和直播平台数万观众的见证下,会长单位杭州优海信息系统有限公司与浙江蓝卓工业互联网信息技术有限公司联合发布了基于supOS的

2021-01-14 13:49:01 1533

1533 世界移动通信大会(MWC展)在上海盛大开幕。大会同期,广和通联合宏电在内的众多生态合作伙伴,隆重启动“5G智造营·生态原力发布会”,发布会上, 宏电携手广和通联合发布搭载广和通5G模组FM650

2021-03-10 14:11:10 1052

1052 就在普京与拜登举行会晤之际中俄联合发布国际月球科研站路线图;而且今天是神舟载人飞船发射成功的大好日子,我国空间站的建设加速推进正大迈步的走向世界前列。 中俄联合发布国际月球科研站路线图的时间是在全球

2021-06-17 12:04:40 11394

11394 安富利旗下全球电子元器件产品与解决方案分销商e络盟通过其在线互动社区与英飞凌联合发起低功耗物联网设计挑战赛。

2021-07-19 14:54:53 1582

1582

现在电子产品一般都有要求低功耗,不同的MCU,进入低功耗的处理流程可能不一样,但是大致的流程还是一样。现对MCU进入低功耗的处理流程大致如下:(1)关闭MCU之外的外设电源,例如:RS485、CAN

2021-10-25 11:36:02 18

18 展锐赋能蚂蚁链和广和通联合发布蚂蚁链首批无线通信可信上链模组。

2021-11-19 20:29:52 1278

1278 近日,全球能源管理和自动化领域的数字化转型专家施耐德电气携手CNBC Catalyst,联合发布了名为《开启可持续未来:数字解决方案成为可持续转型关键》的报告(以下简称报告)。

2022-03-21 17:09:08 1394

1394 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其数字和定制 / 模拟设计流程已获得 TSMC N3E 和 N4P 工艺认证,支持最新的设计规则手册(DRM)。

2022-06-17 17:33:05 4800

4800 8月28日,由华为云、软通动力信息技术(集团)股份有限公司(下称“软通动力”)等多家合作伙伴联合发起的首届828 B2B企业节正式启动。作为此次盛事的联合发起方,软通动力出席启动仪式并将全程参与

2022-08-30 11:25:47 747

747 会上,云天励飞与华为联合发布基于昇腾AI的“AICE赋能行业解决方案”,以AI赋能城市千行百业,共筑产业生态,共创数智未来。

2022-09-05 11:03:41 647

647 电子发烧友网站提供《低功耗数字温度计参考设计.zip》资料免费下载

2022-09-06 10:44:37 2

2 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发布

2023-05-09 10:09:23 708

708 研究院党委书记、副院长宋灵恩,罗兰贝格全球合伙人兼大中华区副总裁李冰联合发布《工业数字化/智能化2030白皮书》。 白皮书憧憬了“IMAGINE”的未来工业,分析了十六大工业行业的数字化进展和二十个共性的高价值工业数字化场景,洞悉了工业装

2023-06-01 03:10:02 363

363

中芯国际是中国大陆最大的半导体制造企业之一,主要业务是为其他半导体公司生产晶片。暂时中断28纳米芯片的生产扩大,将致力于提高12纳米节点的生产能力。smic的决定是出于经济上的原因。

2023-06-01 10:50:21 1485

1485 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ● Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对

2023-07-05 10:12:14 381

381 的 Cadence 流程,以十足把握交付各类 HPC 及消费电子应用 中国上海,2023 年 7 月 14 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布其数字和定制/模拟

2023-07-14 12:50:02 381

381

9月20日-22日,以“加速行业智能化”为主题的华为全联接大会2023在上海召开。作为本届大会唯一最高级别(钻石级)的合作伙伴,软通动力受邀参会,并出席行业辅助运营联合发布仪式, 与华为及伙伴联合发布

2023-09-24 21:55:01 650

650

内容提要 Cadence 数字全流程涵盖关键的新技术,包括一款高精度且支持大规模扩展的寄生参数 3D 场求解器 Cadence Cerebrus 由 AI 驱动,支持 N2 制程,可大幅提高客户

2023-10-10 16:05:04 270

270 内容提要 1 通过利用 Cadence AI 驱动云端数字全流程,Imagination 成功将其最新 5nm 节点的漏电功耗降低 20%,将总功耗降低 6%,同时改善了面积和性能

2023-10-18 15:50:01 160

160 “基于人工智能的cadence cerebrus和更广泛的cadence数字进程是为复杂的下一代设计而设计的,例如5纳米低功耗gpu的imagination。”

2023-10-20 10:04:07 261

261 清华、阿里安全、Real_AI联合发布最新AI安全评估平台

2023-01-13 09:07:31 1

1 Cadence近日宣布,其数字和定制/模拟流程在Intel的18A工艺技术上成功通过认证。这一里程碑式的成就意味着Cadence的设计IP将全面支持Intel的代工厂在这一关键节点上的工作,并提

2024-02-27 14:02:18 160

160

电子发烧友App

电子发烧友App

评论