思维再缜密的程序员也不可能编写完全无缺陷的C语言程序,测试的目的正是尽可能多的发现这些缺陷并改正。这里说的测试,是指程序员的自测试。前期的自测试能够更早的发现错误,相应的修复成本也会很低,如果你不彻底测试自己的代码,恐怕你开发的就不只是代码,可能还会声名狼藉。

2023-09-19 16:24:41 313

313

的测试设计显得尤为重要。对于单片或者数量很小的几片嵌入式SRAM,常用的测试方法是通过存储器内建自测试MBIST来完成,实现时只需要通过EDA软件选取相应的算法,并给每片SRAM生成MBIST控制逻辑

2019-10-25 06:28:55

和应用可靠性所要求的测试水平之间存在著一个非常大的差距。这通常意味着板级ESD元件(如多层压敏电阻、聚合物ESD抑制器和硅保护阵列)必须填补这一差距。要注意的一点是,这些技术的ESD保护性

2019-05-22 05:01:12

设计技术,按照该准则设计即可保证模块的测试性要求 :(1)在模块连接器上可以存取所有BIT的控制和状态信号,从而可使 ATE直接与BIT电路相连;(2)在模块内装入完整的 BIT 功能和机内检测设备

2018-01-11 11:16:01

电路在线测试技术的原理是什么?测试仪由那几部分构成?

2021-04-25 06:50:44

从根本上讲,市场是电路板级仿真的强劲动力。在激烈竞争的电子行业,快速地将产品投入市场至关重要,传统的PCB设计方法要先设计原理图,然后放置元器件和走线,最后采用一系列原型机反复验证/测试。修改

2018-08-24 16:48:08

电路板级的EMC设计(3) PCB布线技术文章目录电路板级的EMC设计(3) PCB布线技术文档简介第三部分:印制电路板的布线技术1.PCB基本特性2.分割3.局部电源和IC间的去耦4.基准面的射频

2021-11-12 08:43:48

电路板改板设计中的可测试性技术电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单的方法来测试,以确定该元件能是否到达预期的功能需求。进一步含义即:麦|斯

2013-10-09 10:57:40

电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单的方法来测试,以确定该元件能是否到达预期的功能需求。进一步含义即: 1 检测产品是否符合技术

2018-09-14 16:25:59

本帖最后由 gk320830 于 2015-3-4 13:43 编辑

电路板设计可测试性技术电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单

2013-10-08 11:26:12

本帖最后由 gk320830 于 2015-3-7 13:19 编辑

电路板设计可测试性技术电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单

2013-10-16 11:41:06

电路板制板可测试性的定义可简要解释为:电路板测试工程师在检测某种元件的特性时应该尽可能使用最简单的方法来测试,以确定该元件能是否到达预期的功能需求。进一步含义即: 1 检测产品是否符合技术

2018-11-27 10:01:40

如题目,电路板信号经过一级三极管,两级运放放大,电路板不动的时候,电路正常工作;电路板震动的时候,电路自动产生干扰信号,干扰信号波形与振铃波形类似,震动停止则干扰波形消失。第一次遇到这种问题,上论坛来请教下大家。

2019-05-13 03:25:58

AMBA测试接口控制器(TIC)是一个ASB总线主设备,它接受来自外部测试总线(32位外部数据总线,如果可用)的测试向量,并启动总线传输。

TIC锁存来自测试总线的地址向量并驱动ASB地址总线

2023-08-22 08:10:20

系统外部的一个模块,它驱动测试接口线以访问ASB总线,然后施加来自测试输入文件的测试矢量(参见图1-1)。

此测试输入文件是运行用TICTalk命令语言编写的C程序的输出。

2023-08-21 06:43:36

自己做的板子,现在用F28069调试CAN通信,应用controlsuite例程自测试功能,可以运行,收发正常,将自测试改成正常模式,就无法正常工作

2018-09-07 11:24:11

法是一种针对时序电路芯片的DFT方案.其基本原理是时序电路可以模型化为一个组合电路网络和带触发器(Flip-Flop,简称FF)的时序电路网络的反馈。内建自测试 内建自测试(BIST)设计技术通过在

2011-12-15 09:35:34

8章中提到的寄存器都没有引用这个自测试位。能否指出这个自测试位在哪个寄存器中。#lsm330dlc自检以上来自于谷歌翻译以下为原文 Hello, For a project we

2019-02-20 06:41:24

应用程序: 此示例代码是MA35D1系列微处理器的实时处理器( RTP) 的自测试库。 此库执行芯片的自测试功能, 以满足市场要求的安全要求。 当芯片出现错误时, 可以实时检测, 系统可以保持功能

2023-08-29 07:04:24

打开MAX中仿真采集板的测试面板出现错误提示“经自测,驱动程序与通讯失败”,重置MAX和重装labview和DAQmx还是解决不了,该怎么处理

2016-11-03 10:50:00

到电路板和我的电脑,并将以太网接口IP设置为192.168.1.100步骤2:设置视频(DVI或VGA)连接 - 使用DVI到VGA适配器将vga电缆连接到显示器和电路板步骤3:以太网连接的跳线 - 已

2019-09-18 10:42:00

测试点应均匀布在插件板上 每个节点至少有一个测试点(100%通道) 备用或不用的门电路都有测试点 供电电源的多外测试点分布在不同位置 元件标志 标志文字同一方向 型号、版本

2018-11-23 17:07:53

达到测试目的。基于以上原因,这种测试方法正逐渐被扫描测试和内建自测试技术(BIST)所取代。2.扫描技术印制电路中一般都包括了时序逻辑和组合逻辑两部分。组合逻辑使现有测试技术能较好地测试生成;而时序

2018-09-19 16:17:24

本帖最后由 大彭 于 2014-11-20 10:35 编辑

PCB设计常用板级信号完整性分析模型为了进行电路模拟,必须先建立元器件的模型,也就是对于电路模拟程序所支持的各种元器件,在

2014-11-20 10:31:44

边界扫描和集成自测试技术基础上的测试战略肯定会增加费用。开发工程师必然要在电路中使用的边界扫描元件(IEEE-1149.1-标准),并且要设法使相应的具体的测试引线脚可以接触(如测试数据输入-TDI

2014-11-19 11:47:21

STC8951单片机不断电下载的方法(亲自测试过)对于STC89C51系列单片机如果要下载程序,我们需要先断电,点击下载,再给单片机上电这时,他就会自动下载程序。这是因为单片机在冷启动时,首先执行

2013-04-30 01:04:20

dft可测试性设计,前言可测试性设计方法之一:扫描设计方法可测试性设计方法之二:标准IEEE测试访问方法可测试性设计方法之三:逻辑内建自测试可测试性设计方法之四:通过MBIST测试寄存器总结...

2021-07-22 09:10:42

msp430x14x用TINERB产生6路PWM信号,亲自测试可行

2016-07-19 21:52:22

设计了一种多通道频率测量系统。系统由模拟开关、信号调理电路、FPGA、总线驱动电路构成,实现对频率信号的分压、放大、滤波、比较、测量,具备回路自测试功能,可与主设备进行数据交互,具有精度高、可扩展

2019-06-27 07:23:11

目前随着使用大规模集成电路的产品不断出现,相应的PCB的安装和测试工作已越来越困难。虽然印制电路板的测试仍然使用在线测试技术这一传统方法,但是这种方法由于芯片的小型化及封装而变得问题越来越多

2018-09-10 16:50:00

大家,可以帮我推荐一下不同速率电路板级间的连接器吗?具体要求是如下这样:实现两块电路板的连接,它们分别含有一块FPGA的电路板的,其中包括低速的控制信号的传播和高速数据信号的传输,低速信号至少有八个,高速信号有上百个,请各位大神推荐一下。如果能介绍下接口选型的经验就更好了。

2017-09-23 21:45:54

我修改了add.S文件,想让make run_test SIM=iverilog后出现file.可是编译不了,add.S文件也没显示更新。

可是我在测试自测试用例的时候,make compile

2023-08-12 06:50:38

技术的主要缺点是通孔要占用所有层的珍贵空间,而不考虑该层是否需要进行电气连接。 2 埋孔 埋孔是连接多基板的两层或更多层的镀通孔,埋孔处于电路板的内层结构中,不出现在电路板的外表面上。图2 为具有

2018-11-27 10:03:17

本文介绍了一种基于信号完整性计算机分析的高速数字信号PCB板的设计方法。在这种设计方法中,首先将对所有的高速数字信号建立起PCB板级的信号传输模型,然后通过对信号完整性的计算分析来寻找设计的解

2018-08-29 16:28:48

环境的多模型机动目标跟踪算法。仿真结果验证了该算法跟踪性能的有效性。 0 引言 随着信息技术的快速发展和现代军事及民用需求的不断提高,对目标跟踪的精度也相应地提出了更高的要求。在真实的目标跟踪系统

2018-12-05 15:16:23

,实际板卡与简化的板卡仿真模型之间的差异将对热仿真结果带来不可预知的影响?板级热仿真技术仍存在诸多问题: 1) 板卡芯片热输入数据不统一?不确定?不准确,没有科学有效的测量计算方法? 2) 板卡EDA

2018-09-26 16:22:17

扫描技术应用在电路板快速测试系统中,设计了一套具有自 主知识产权的边界扫描测试系统,并对系统的故障分析策略进行了讨论研究,提出对周期信 号采用信号统计法和数据分析法的故障分析策略。参考文献:[1

2018-09-10 16:28:11

个位大佬你们是如何测试STM32中断抢占的,我的测试步骤如下:第一步、我配置了两个定时器,定时器2优先级为3,定时器3优先级为4,

第二步、我各自测试都可以发生中断

第三步、在定时器3中加

2024-04-22 06:31:54

工程师来说,建立在边界扫描和集成自测试技术基础上的测试战略肯定会增加费用。开发工程师必然要在电路中使用的边界扫描组件( IEEE-1149.1- 标准),并且要设法使相应的具体的测试引线脚可以接触(如测试

2015-01-14 14:34:27

测试性。对此可使用边界扫描和集成自测试技术来缩短测试完成时间和提高测试效果。 对于开发工程师和测试工程师来说,建立在边界扫描和集成自测试技术基础上的测试战略肯定会增加费用。开发工程师必然要在电路中使

2017-11-06 09:11:17

能处于插件板的背面▪ 测试点应均匀布在插件板上▪ 每个节点至少有一个测试点(100%通道)▪ 备用或不用的门电路都有测试点▪ 供电电源的多外测试点分布在不同位置 元件标志 ▪ 标志文字同一

2017-11-06 10:33:34

放大电路和加法器电路各自测试时都对,但放大器输出之后接加法器的时候输出不对!新手求助

2016-04-28 08:41:31

近期安泰维修中心接修到一台E8267C信号发生器,客户描述仪器自测试未通过,下面就来看看这台仪器的损坏原因以及维修过程。故障现象自测试未通过,频率3.2G以上功率无输出。检测过程外观完好,自检

2020-09-18 14:23:21

的接口。它们带有元件编号和序列号数据等等,还包括最近故障检测日志。PCI-DIO-96 被作为一个使用CPLD、有160 个管脚的DIO,CPLD 将来自测试控制器PC 的I/O 板卡的输出和输入进行

2013-10-28 14:41:12

)设备的接口。它们带有元件编号和序列号数据等等,还包括最近故障检测日志。PCI-DIO-96 被作为一个使用CPLD、有160 个管脚的DIO,CPLD 将来自测试控制器PC 的I/O 板卡的输出和输入

2018-09-10 16:49:58

,同时将调节元器件放置和布线所需要的时间加以计划,以便调整信号完整性设计的指针。 6 技术选择 不同的驱动技术适于不同的任务。信号是点对点的还是一点对多抽头的?信号是从电路板输出还是留在相同的电路板上

2015-01-07 11:44:45

( 甚至是多板系统 ) ,自动屏蔽 SI 问题并生成精确的“引脚到引脚”延迟参数。只要输入信号足够好,仿真结果也会一样好。这使得器件模型和电路板制造参数的精确性成为决定仿真结果的关键因素。很多设计工程师将

2014-11-18 10:20:50

和布线所需要的时间加以计划,以便调整信号完整性设计的指标。 6、技术选择 不同的驱动技术适于不同的任务。信号是点对点的还是一点对多抽头的?信号是从电路板输出还是

2009-05-24 23:02:49

、未来技术的趋势 设想系统中所有输出都可以调整以匹配布线阻抗或者接收电路的负载,这样的系统测试方便, SI 问题可以通过编程解决,或者按照 IC 特定的工艺分布来调整电路板使 SI 达到要求,这样

2018-08-23 08:42:59

本帖最后由 一只耳朵怪 于 2018-6-14 10:25 编辑

eCan 自测试模式下可以产生中断吗? F2812

2018-06-14 01:20:48

基于DSP的测试技术与传统的测试技术相比,有哪些优势?基本的混合信号测试技术包括哪些?采样和重建在混合信号测试中的应用

2021-04-21 06:41:10

继电器来选择所需的测试。图 1 是整体测试电路。在图 2 至图 13 中,信号路径以红色显示,以便与前两篇文章中所介绍的方法进行比较。图 1.该电路整合了用于测试运算放大器的自测试电路及双运算放大器环路

2018-09-07 11:04:41

测试,从而利用JTAG边界扫描架构测试高速系统级芯片(SoC)的互连上发生的时延破坏。ALT="图1:信号完整性故障模型。"> 互连中的信号完整性损耗对于数千兆赫兹高度

2009-10-13 17:17:59

一、电路在线测试技术 1、在线测试原理:在线测试的基本原理是测试仪为印制电路板上的被测芯片提供输入激励,同时在计算机控制下自动采集记录被测芯片的输出响应和状态值,通过计算机将其记录的所有状态值

2018-09-10 16:28:17

高速电路PCB板级设计技巧改进电路设计规程提高可测试性随着微型化程度不断提高,元件和布线技术也取得巨大发展,例如BGA外壳封装的高集成度的微型IC,以及导体之间的绝缘间距缩小到0.5mm,这些仅是

2009-05-16 20:41:11

上,主要应用于集成电路的设计。而MicroSim公司(后来被OrCAD公司兼并,而OrCAD又被Cadence公司兼并)开发的PSPICE运行于PC上,主要应用于PCB板级和系统级的设计。 SPICE

2018-08-31 14:55:27

电工技术(电工学I)典型题解析及自测试题是根据国家教育部(前国家教委)1995年修订的“高等工业学校电工技术(电工学Ⅰ)课程教学基本要求“编写的学习指导书,主要内容是

2008-09-20 21:46:12 0

0 近几年基于预定制模块IP(Intellectual Property)核的SoC(片上系统)技术得到快速发展,各种功能的IP 核可以集成在一块芯片上,从而使得SoC 的测试、IP 核的

2009-09-09 08:33:41 24

24 嵌入式存储器内建自测试的一种新型应用孙华义 郑学仁 闾晓晨王颂辉吴焯焰 华南理工大学微电子研究所广州 510640摘要:当今,嵌入式存储器在SoC 芯片面积中所占的比例越来

2009-12-20 09:26:11 38

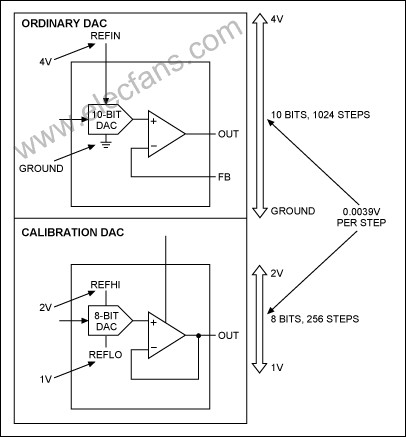

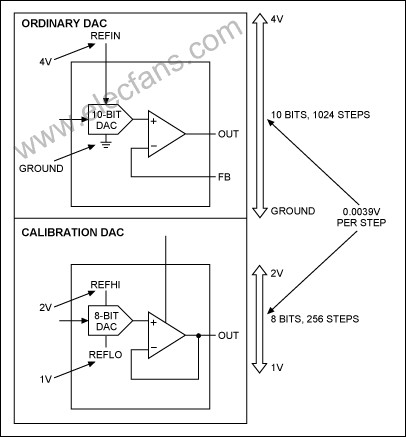

38 本设计指南探讨了信号调理、调整和校准电路,用于修正系统误差,从而以合理的成本确保工业设备安全、精确。校准部分讨论了利用最终测试补偿元件误差,通过上电自测试和连

2010-07-30 11:34:32 8

8 本文介绍了一款RISC_CPU的可测性设计,为了提高芯片的可测性,采用了扫描设计和存储器内建自测试,这些技术的使用为该芯片提供了方便可靠的测试方案。

2010-07-30 17:19:51 20

20 芯片间的互连速率已经达到GHz量级,相比较于低速互连,高速互连的测试遇到了新的挑战。本文探讨了高速互连测试的难点,传统互连测试方法的不足,进而介绍了互连内建自测试(I

2010-07-31 17:00:16 15

15 内建自测试是一种有效的测试存储器的方法。分析了NOR型flash存储器的故障模型和测试存储器的测试算法,在此基础上,设计了flash存储器的内建自测试控制器。控制器采用了一种23

2010-07-31 17:08:54 35

35 随着超大规模集成电路(VLSI)制造密度的提高.使得电子电路和系统变得日益复杂.也显著地拉加了模拟和数字集成电路充分测试的难度.另外.市场竞争的压力对集成电路(Ic)的-恻试

2010-08-06 15:53:29 39

39 介绍了用于IP核测试的内建自测试方法(BIST)和面向测试的IP核设计方法,指出基于IP核的系统芯片(SOC) 的测试、验证以及相关性测试具有较大难度,传统的测试和验证方法均难以满足

2010-12-13 17:09:11 10

10 在BIST(内建自测试)过程中,线性反馈移位寄存器作为测试矢量生成器,为保障故障覆盖率,会产生很长的测试矢量,从而消耗了大量功耗。在分析BIST结构和功耗模型的基础上,针

2010-12-23 15:35:11 0

0

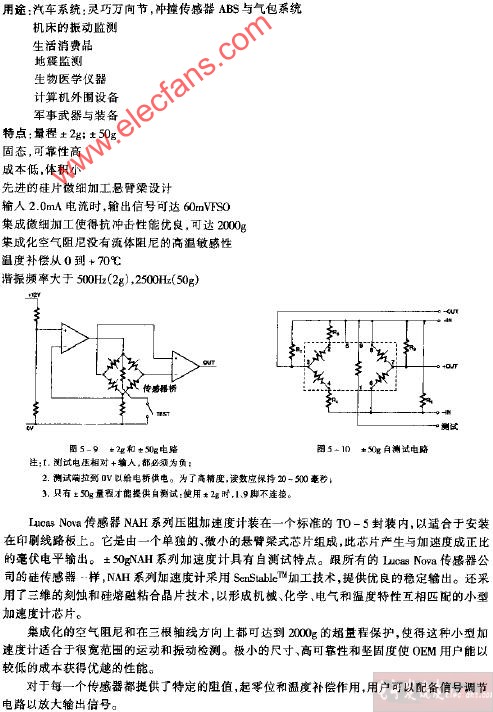

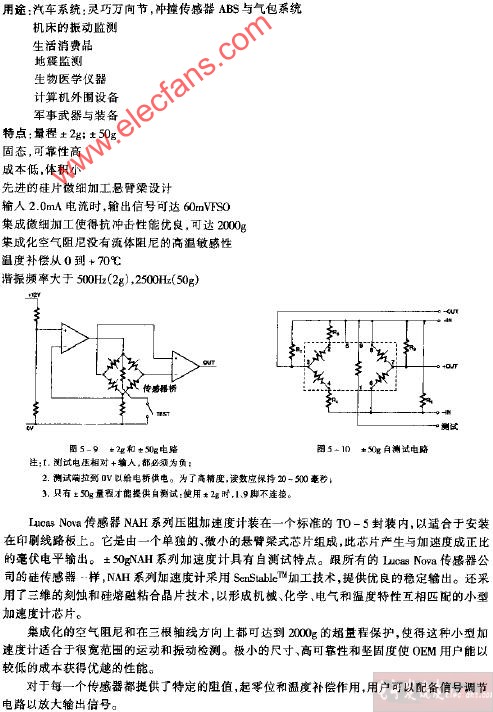

±50g自测试电路图

2009-07-03 12:03:06 411

411

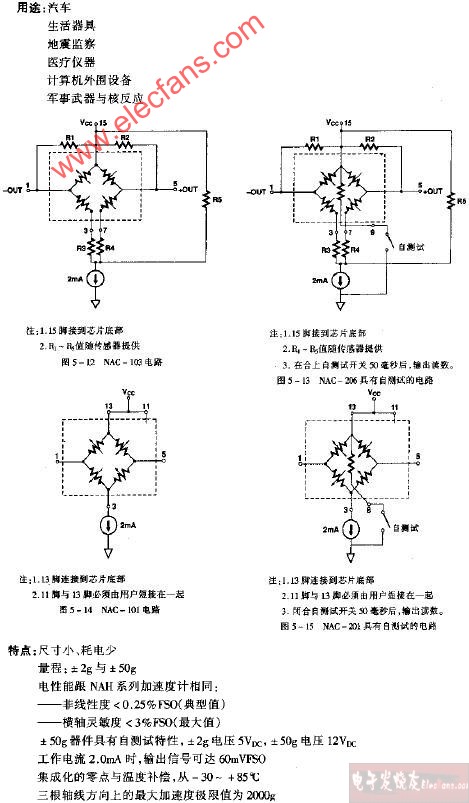

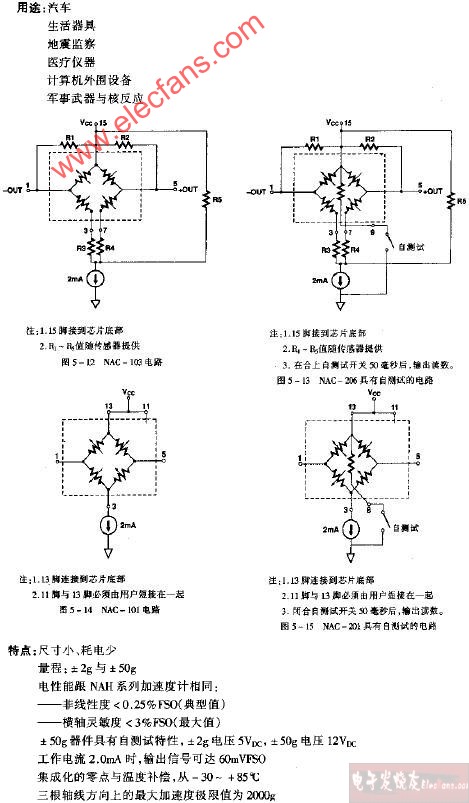

NAC-201具有自测试的电路图

2009-07-03 13:09:10 409

409

NAC-206具有自测试的电路图

2009-07-03 13:09:35 478

478

本设计指南探讨了信号调理、调整和校准电路,用于修正系统误差,从而以合理的成本确保工业设备安全、精确。校准部分讨论了利用最终测试补偿元件误差,通过上电自测试和连

2010-07-24 12:08:27 626

626 本设计指南探讨了信号调理、调整和校准电路,用于修正系统误差,从而以合理的成本确保工业设备安全、精确。校准部分讨论了利用最终测试补偿元件误差,通过上电自测试和连

2010-07-27 18:09:20 693

693

通常我们在设计芯片的同时,可以根据芯片本身的特征,额外地把可测性电路设计(Design For Testability)在芯片里。谈到可测性的电路设计,内建自测试(BIST)和基于扫描Scan—Based)的电路设计

2011-06-10 10:13:45 2157

2157

随着集成电路的规模不断增大,集成电路的可测性设计正变得越来越重要.综述了可测性设计方案扫描通路法、内建自测试法和边界扫描法,并分析比较了这几种设计方案各自的特点及应

2011-10-28 17:28:51 46

46 在集成电路内建自测试的过程中,电路的测试功耗通常显著高于正常模式产生的功耗,因此低功耗内建自测试技术已成为当前的一个研究热点。为了减少被测电路内部节点的开关翻转活

2012-02-01 14:00:36 21

21 usb口转串口的驱动,本人亲自测试通过,请放心使用

2015-11-10 17:06:56 24

24 本人亲自测试的Jlink刷机教程,很有含量哦

2015-11-06 16:56:38 15

15 XDS100V3原理图,是按照官方的原理图重新画的,亲自测试通过。

2015-12-02 10:22:11 157

157 温度控制系统,亲自测试,可以使用,十分强大,感兴趣的可以看看。

2016-07-22 16:53:46 0

0 一种基于包的逻辑内置自测试电路设计方法

2017-02-07 16:14:56 12

12 在本系列的第 1 部分中,我们为大家介绍了三种运算放大器测试电路:自测试电路、双运算放大器环路以及三运算放大器环路。这些电路有助于测试失调电压 (VOS)、共模抑制比 (CMRR)、电源抑制

2017-04-08 06:06:34 4888

4888

TMS570LS系列微控制器与可编程内置自测试(pbist)实现建筑。的pbist架构提供了一种存储器BIST引擎不同的覆盖水平在许多嵌入式内存实例中。TMS570LS系列微控制器可分为两类:130

2018-04-16 16:03:38 12

12 随着集成电路复杂度越来越高,测试开销在电路和系统总开销中所占的比例不断上升,测试方法的研究显得非常突出。目前在测试源的划分上可以采用内建自测试或片外测试。

2019-04-26 09:12:00 1030

1030

仿真结果:为了评价BIC监测仪用于新型并行模拟自测试的可行性,进行了故障仿真。全差分电流传送器被用作被测器件。在监视通过/失败输出(图2)的同时,将每个典型的MOS晶体管的终端故障(短路和开路)分别

2019-11-26 16:36:30 0

0 VLSI测试技术导论, 可测试性设计, 逻辑与故障模拟,测试生成,逻辑自测试,测试压缩,逻辑电路故障诊断,存储器测试与BIST,存储器诊断与BISR,边界扫描与SOC测试,纳米电路测试技术,复习及习题

2020-10-09 08:00:00 1

1 开关电源(Buck电路)的小信号模型及环路设计(实用电源技术答案)-开关电源(Buck电路)的小信号模型及环路设计

2021-09-18 10:03:12 78

78 糕的是,您可能很晚才发现,而此时纠正该问题已经更难了。 自测试补偿 以最简单的形式看,图 1 中的自测试电路实际上是一款增益为 1201 的闭环系统。如果将 R1 减小至 5kW,闭环增益就是 301。因此,它具有固有的稳定性,即使采用未

2021-11-23 17:46:33 1648

1648 作者:Martin Rowe — 2011 年 11 月 16 日

在本系列的第 1 部分中,我们为大家介绍了三种运算放大器测试电路:自测试电路、双运算放大器环路以及三运算放大器环路。这些电路

2021-11-23 17:41:50 1456

1456 LBIST (Logic build-in-self test), 逻辑内建自测试。和MBIST同理,在关键逻辑上加上自测试电路,看看逻辑cell有没有工作正常。BIST总归会在芯片里加入自测试逻辑,都是成本。

2022-08-29 15:33:30 2266

2266 NMOS管,其电路模型可分为大信号模型和小信号模型。

2022-10-14 13:04:13 5835

5835 UM2986 STM32U5系列IEC 60730自测试库用户指南

2022-11-22 08:21:45 0

0 大信号模型和小信号模型是电子工程和通信领域中常用的两种模型,它们在描述和分析电子电路或系统时具有不同的特点和应用范围。以下是关于大信号模型和小信号模型区别的介绍。 大信号模型:大信号模型主要用于描述

2023-12-19 11:35:55 3424

3424

电子发烧友App

电子发烧友App

评论