说到PCB板,很多朋友会想到它在我们周围随处可见,从一切的家用电器,电脑内的各种配件,到各种数码产品,只要是电子产品几乎都会用到PCB板,那么到底什么是PCB板呢?PCB板就是PrintedCircuitBlock,即印制电路板,供电子组件安插,有线路的基版。通过使用印刷方式将镀铜的基版印上防蚀线路,并加以蚀刻冲洗出线路。

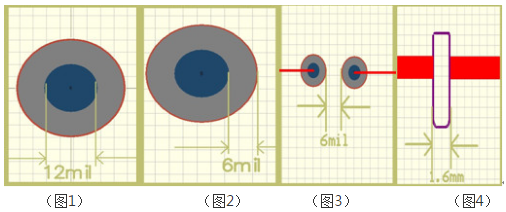

PCB板可以分为单层板、双层板和多层板。各种电子元件都是被集成在PCB板上的,在最基本的单层PCB上,零件都集中在一面,导线则都集中在另一面。这么一来我们就需要在板子上打洞,这样接脚才能穿过板子到另一面,所以零件的接脚是焊在另一面上的。因为如此,这样的PCB的正反面分别被称为零件面(ComponentSide)与焊接面(SolderSide)。双层板可以看作把两个单层板相对粘合在一起组成,板的两面都有电子元件和走线。有时候需要把一面的单线连接到板的另一面,这就要通过导孔(via)。导孔是在PCB上,充满或涂上金属的小洞,它可以与两面的导线相连接。

现在很多电脑主板都在用4层甚至6层PCB板,而显卡一般都在用了6层PCB板,很多高端显卡像nVIDIAGeForce4Ti系列就采用了8层PCB板,这就是所谓的多层PCB板。在多层PCB板上也会遇到连接各个层之间线路的问题,也可以通过导孔来实现。由于是多层PCB板,所以有时候导孔不需要穿透整个PCB板,这样的导孔叫做埋孔(Buriedvias)和盲孔(Blindvias),因为它们只穿透其中几层。盲孔是将几层内部PCB与表面PCB连接,不须穿透整个板子。埋孔则只连接内部的PCB,所以光是从表面是看不出来的。在多层板PCB中,整层都直接连接上地线与电源。所以我们将各层分类为信号层(Signal),电源层(Power)或是地线层(Ground)。如果PCB上的零件需要不同的电源供应,通常这类PCB会有两层以上的电源与电线层。采用的PCB板层数越多,成本也就越高。当然,采用更多层的PCB板对提供信号的稳定性很有帮助。

专业的PCB板制作过程相当复杂,拿4层PCB板为例。主板的PCB大都是4层的。制造的时候是先将中间两层各自碾压、裁剪、蚀刻、氧化电镀后,这4层分别是元器件面、电源层、地层和焊锡压层。再将这4层放在一起碾压成一块主板的PCB。接着打孔、做过孔。洗净之后,将外面两层的线路印上、敷铜、蚀刻、测试、阻焊层、丝印。最后将整版PCB(含许多块主板)冲压成一块块主板的PCB,再通过测试后进行真空包装。如果PCB制作过程中铜皮敷着得不好,会有粘贴不牢现象,容易隐含短路或电容效应(容易产生干扰)。PCB上的过孔也是必须注意的。如果孔打得不是在正中间,而是偏向一边,就会产生不均匀匹配,或者容易与中间的电源层或地层接触,从而产生潜在短路或接地不良因素。

铜线布线过程

制作的第一步是建立出零件间联机的布线。我们采用负片转印方式将工作底片表现在金属导体上。这项技巧是将整个表面铺上一层薄薄的铜箔,并且把多余的部份给消除。追加式转印是另一种比较少人使用的方式,这是只在需要的地方敷上铜线的方法,不过我们在这里就不多谈了。正光阻剂是由感光剂制成的,它在照明下会溶解。有很多方式可以处理铜表面的光阻剂,不过最普遍的方式,是将它加热,并在含有光阻剂的表面上滚动。它也可以用液态的方式喷在上头,不过干膜式提供比较高的分辨率,也可以制作出比较细的导线。遮光罩只是一个制造中PCB层的模板。在PCB板上的光阻剂经过UV光曝光之前,覆盖在上面的遮光罩可以防止部份区域的光阻剂不被曝光。这些被光阻剂盖住的地方,将会变成布线。在光阻剂显影之后,要蚀刻的其它的裸铜部份。蚀刻过程可以将板子浸到蚀刻溶剂中,或是将溶剂喷在板子上。一般用作蚀刻溶剂使用三氯化铁等。蚀刻结束后将剩下的光阻剂去除掉。

1.布线宽度和电流

一般宽度不宜小于0.2mm(8mil)

在高密度高精度的PCB上,间距和线宽一般0.3mm(12mil)。

当铜箔的厚度在50um左右时,导线宽度1~1.5mm (60mil) = 2A

公共地一般80mil,对于有微处理器的应用更要注意。

2.到底多高的频率才算高速板?

当信号的上升/下降沿时间《 3~6倍信号传输时间时,即认为是高速信号。

对于数字电路,关键是看信号的边沿陡峭程度,即信号的上升、下降时间,

按照一本非常经典的书《High Speed Digtal Design》的理论,信号从10%上升到90%的时间小于6倍导线延时,就是高速信号!------即!即使8KHz的方波信号,只要边沿足够陡峭,一样是高速信号,在布线时需要使用传输线路论

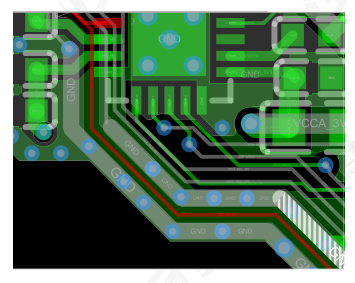

3.PCB板的堆叠与分层

四层板有以下几种叠层顺序。下面分别把各种不同的叠层优劣作说明:

第一种情况

GND

S1+POWER

S2+POWER

GND

第二种情况

SIG1

GND

POWER

SIG2

第三种情况

GND

S1

S2

POWER

注:S1 信号布线一层,S2 信号布线二层;GND 地层 POWER 电源层

第一种情况,应当是四层板中最好的一种情况。因为外层是地层,对EMI有屏蔽作用,同时电源层同地层也可靠得很近,使得电源内阻较小,取得最佳郊果。但第一种情况不能用于当本板密度比较大的情况。因为这样一来,就不能保证第一层地的完整性,这样第二层信号会变得更差。另外,此种结构也不能用于全板功耗比较大的情况。

第二种情况,是我们平时最常用的一种方式。从板的结构上,也不适用于高速数字电路设计。因为在这种结构中,不易保持低电源阻抗。以一个板2毫米为例:要求Z0=50ohm. 以线宽为8mil.铜箔厚为35цm。这样信号一层与地层中间是0.14mm。而地层与电源层为1.58mm。这样就大大的增加了电源的内阻。在此种结构中,由于辐射是向空间的,需加屏蔽板,才能减少EMI。

第三种情况,S1层上信号线质量最好。S2次之。对EMI有屏蔽作用。但电源阻抗较大。此板能用于全板功耗大而该板是干扰源或者说紧临着干扰源的情况下。

4.阻抗匹配

反射电压信号的幅值由源端反射系数ρs和负载反射系数ρL 决定

ρL = (RL - Z0) / (RL + Z0) 和 ρS = (RS - Z0) / (RS + Z0)

在上式中,若RL=Z0则负载反射系数ρL=0。若 RS=Z0源端反射系数ρS=0。

由于普通的传输线阻抗Z0通常应满足50Ω的要求50Ω左右,而负载阻抗通常在几千欧姆到几十千欧姆。因此,在负载端实现阻抗匹配比较困难。然而,由于信号源端(输出)阻抗通常比较小,大致为十几欧姆。因此在源端实现阻抗匹配要容易的多。如果在负载端并接电阻,电阻会吸收部分信号对传输不利(我的理解)。当选择TTL/CMOS标准 24mA驱动电流时,其输出阻抗大致为13Ω。若传输线阻抗Z0=50Ω,那么应该加一个33Ω的源端匹配电阻。13Ω+33Ω=46Ω (近似于50Ω,弱的欠阻尼有助于信号的setup时间)

当选择其他传输标准和驱动电流时,匹配阻抗会有差异。在高速的逻辑和电路设计时,对一些关键的信号,如时钟、控制信号等,我们建议一定要加源端匹配电阻。

这样接了信号还会从负载端反射回来,因为源端阻抗匹配,反射回来的信号不会再反射回去。

电子发烧友App

电子发烧友App

评论