2.3视频信号卡

视频信号卡为整个系统的核心部分,因其视频信号的生成所涉及的运算量很大,单个DSP难以生成多路视频信号,同时出于系统升级的考虑,因此该视频信号模拟器的每路都使用高性能的TMS320C6713型浮点数字信号处理器。该DSP采用先进的超长指令字结构,内置8个独立的功能单元、2个定点算术逻辑单元,2个浮点乘法器,4个浮点ALU、32个32位通用目的寄存器,4 K字节的L1高速程序缓存区,4 K字节的L1高速数据缓存器,256 K字节的L2两级数据缓存器。这种结构能最大限度地发挥8个功能单元的并行计算能力,使得300 MHz系统时钟工作下的DSP性能达到2400MI/s和1 800MFLO/s。

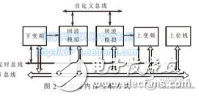

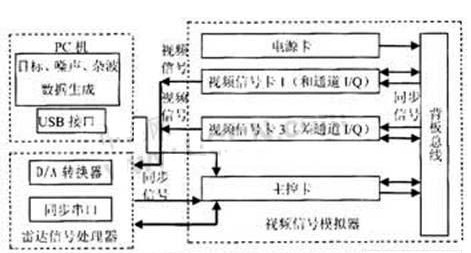

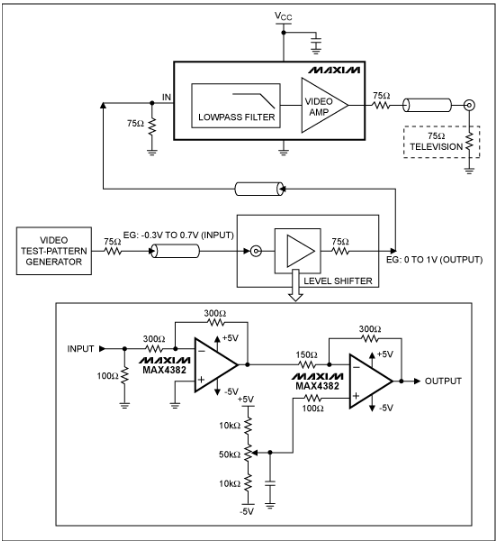

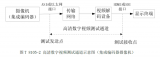

单路视频信号生成原理框图如图4所示。其中,DSP完成视频信号运算;FPGA(1)用于控制LVDS收发器接收来自总线上的命令、地址及数据,在产生视频信号前,将上位机事先产生的杂波数据、噪声及目标参数下载至Flash存储器中。在生成视频信号期间,FPGA(1)判断DSP的工作状态,将Flash存储器的数据读入输入FIFO中;FPGA(2)主要完成DSP渎写输入、输出FIFO的逻辑转换,接收来自DSP计算视频信号相对PRF信号的延迟时间,通过FPGA(1)接收同步信号,读取输出FIFO的数据并启动D/A转换器;DSP将输入FIFO的数据渎人其内部RAM,根据对应的数据及目标参数生成所需的视频信号数据,并将运算后的数据写入输出FIFO。FIFO采用IDT72V17160,其读写速度可达100 MHz。

3系统工作流程

上位机根据噪声和杂波模型脱机产生和路、方位差、俯仰差三通道I/O杂波、噪声及目标参数,由上位机发出指令、卡地址将各通道的数据下载至对应的Flash存储器。然后,由上位机生成DSP指令,发送至主控卡的缓存中,触发同步信号,将指令发送至DSP,同时视频卡根据该同步信号产生视频信号,DSP对视频信号进行采样、运算,并将其结果及状态信息发送至上位机显示。

3.1数据下载

数据下载即将上位机预先产生的杂波、噪声数据及目标参数通过背板总线下载到各通道对应的Flash存储器中,整个发送过程由上位机控制,按表1所示格式将命令、地址、数据的顺序发送至主控卡,然后由主控卡FPGA控制LVDS收发器,将命令、地址及数据发送至单环总线上,所有总线节点(视频卡)接收到命令后,转为数据下载工作状态,接着再判断是否为该节点地址。若是,准备接收数据,并判断区地址,将数据写入对应的Flash分区中;若不是,关闭数据通道,等待接收新卡地址。因为Flash存储器在写入2 K字节数据后需要一个较长的编程时间,所以在实际数据下载的过程中,使用轮询写人方法,即上位机每发送2 K字节数据后,就发送新卡地址,将数据写入下一通道的Flash存储器中,依次执行,直到第一通道,Flash存储器编程结束,再将数据继续写入,节约了数据下载时间。

3.2视频信号的生成

整个视频信号的生成过程,数据的搬移及信号的运算均由DSP完成,由于TMS320C6713 DSP具有16个EDMA通道,可在不占用CPU运行周期的前提下,实现数据快速搬移,所以该设计在DSP内部开辟一个乒乓缓存区(Ping PangCache),CPU在调用乒乓缓存数据时,EDMA往乒乓缓存中搬移数据后进行交换,这样可同时执行EDMA数据搬移和CPU信号运算,保证实时生成视频信号。

当各通道的杂波、噪声及目标参数下载完成,各通道FPGA(1)接收上位机指令,将存储在Flash的数据读入输入FIFO中,DSP启动EDMA通道将输入FIFO数据读至其内部乒乓缓存中。此时,DSP发出READY信号给FPGA(2),FPGA(2)将PRF同步信号接入DSP的外部中断引脚,这样当下一个PRF同步信号到来时,触发DSP的外部中断,DSP执行内部的波形运算程序,并启动EDMA通道将杂波等数据搬移至乒乓缓存,运算结束后,DSP将目标出现的延时发给FPGA(2),并将运算完毕的波形数据搬移至输出FIFO。FPGA(2)收到延迟后,在下一个PRF同步信号到来时,计数DSP接收时间,计数结束,从输出FIFO读取运算完毕的数据,同时启动D/A转换器进行数据转换。

3.3性能改进

虽然系统性能能够满足实际应用需求,但对某些环节稍作改进,会使整个系统功能进一步增强。对于DSP而言,同步FIFO为异步存储器,所以DSP在读写FIFO时设置为异步方式,读FIFO的频率仅能达到25 MHz,写FIFO的频率仅能达到33 MHz。如果将DSP读写SDRAM时序进行逻辑转换,可使读写FIFO的频率达到100 MHz,大大增强DSP的数据吞吐能力;另外单路视频信号的数据仅使用一片Flash存储器,虽然其峰值读数速度可达40 M字节,但由于每读2 K字节后,Flash需占一个缓存时间,这样其平均读数速度仅能达到约27 M字节。若将两片Flash并联,则达到其峰值速度,提高了系统性能;另外,目前在DSP内部仅在数据输入端开辟一个乒乓缓存,若在数据输出端也开辟一个乒乓缓存,则可将数据搬移和CPU运算进一步并行执行,缩短每个PRF周期的数据处理时间。

4结语

针对具体的雷达信号处理器,提出一种视频信号模拟器的硬件设计,模拟器采用PC机+DSP组合架构,整个系统采用插卡式结构,各路视频信号的生成使用相似的硬件电路,由PC机产生所需的杂波、噪声数据及目标参数,并事先将生成的各路视频信号所需的杂波、噪声及目标参数通过自行设计的自适应单环总线下载到对应的大容量Flash存储器中,数据下载完毕后,经由DSP组合实时运算,在每个PRF同步信号的触发下输出视频模拟信号。由于Flash存储器为非易失性存储器,具有掉电后数据不丢失的优点,所以如果杂波、噪声及目标参数不改变的情况下,数据只需下载一次。另外,使用文中提出的环网总线结构,可保证数据的快速下载。

2.3视频信号卡

视频信号卡为整个系统的核心部分,因其视频信号的生成所涉及的运算量很大,单个DSP难以生成多路视频信号,同时出于系统升级的考虑,因此该视频信号模拟器的每路都使用高性能的TMS320C6713型浮点数字信号处理器。该DSP采用先进的超长指令字结构,内置8个独立的功能单元、2个定点算术逻辑单元,2个浮点乘法器,4个浮点ALU、32个32位通用目的寄存器,4 K字节的L1高速程序缓存区,4 K字节的L1高速数据缓存器,256 K字节的L2两级数据缓存器。这种结构能最大限度地发挥8个功能单元的并行计算能力,使得300 MHz系统时钟工作下的DSP性能达到2400MI/s和1 800MFLO/s。

单路视频信号生成原理框图如图4所示。其中,DSP完成视频信号运算;FPGA(1)用于控制LVDS收发器接收来自总线上的命令、地址及数据,在产生视频信号前,将上位机事先产生的杂波数据、噪声及目标参数下载至Flash存储器中。在生成视频信号期间,FPGA(1)判断DSP的工作状态,将Flash存储器的数据读入输入FIFO中;FPGA(2)主要完成DSP渎写输入、输出FIFO的逻辑转换,接收来自DSP计算视频信号相对PRF信号的延迟时间,通过FPGA(1)接收同步信号,读取输出FIFO的数据并启动D/A转换器;DSP将输入FIFO的数据渎人其内部RAM,根据对应的数据及目标参数生成所需的视频信号数据,并将运算后的数据写入输出FIFO。FIFO采用IDT72V17160,其读写速度可达100 MHz。

3系统工作流程

上位机根据噪声和杂波模型脱机产生和路、方位差、俯仰差三通道I/O杂波、噪声及目标参数,由上位机发出指令、卡地址将各通道的数据下载至对应的Flash存储器。然后,由上位机生成DSP指令,发送至主控卡的缓存中,触发同步信号,将指令发送至DSP,同时视频卡根据该同步信号产生视频信号,DSP对视频信号进行采样、运算,并将其结果及状态信息发送至上位机显示。

3.1数据下载

数据下载即将上位机预先产生的杂波、噪声数据及目标参数通过背板总线下载到各通道对应的Flash存储器中,整个发送过程由上位机控制,按表1所示格式将命令、地址、数据的顺序发送至主控卡,然后由主控卡FPGA控制LVDS收发器,将命令、地址及数据发送至单环总线上,所有总线节点(视频卡)接收到命令后,转为数据下载工作状态,接着再判断是否为该节点地址。若是,准备接收数据,并判断区地址,将数据写入对应的Flash分区中;若不是,关闭数据通道,等待接收新卡地址。因为Flash存储器在写入2 K字节数据后需要一个较长的编程时间,所以在实际数据下载的过程中,使用轮询写人方法,即上位机每发送2 K字节数据后,就发送新卡地址,将数据写入下一通道的Flash存储器中,依次执行,直到第一通道,Flash存储器编程结束,再将数据继续写入,节约了数据下载时间。

3.2视频信号的生成

整个视频信号的生成过程,数据的搬移及信号的运算均由DSP完成,由于TMS320C6713 DSP具有16个EDMA通道,可在不占用CPU运行周期的前提下,实现数据快速搬移,所以该设计在DSP内部开辟一个乒乓缓存区(Ping PangCache),CPU在调用乒乓缓存数据时,EDMA往乒乓缓存中搬移数据后进行交换,这样可同时执行EDMA数据搬移和CPU信号运算,保证实时生成视频信号。

当各通道的杂波、噪声及目标参数下载完成,各通道FPGA(1)接收上位机指令,将存储在Flash的数据读入输入FIFO中,DSP启动EDMA通道将输入FIFO数据读至其内部乒乓缓存中。此时,DSP发出READY信号给FPGA(2),FPGA(2)将PRF同步信号接入DSP的外部中断引脚,这样当下一个PRF同步信号到来时,触发DSP的外部中断,DSP执行内部的波形运算程序,并启动EDMA通道将杂波等数据搬移至乒乓缓存,运算结束后,DSP将目标出现的延时发给FPGA(2),并将运算完毕的波形数据搬移至输出FIFO。FPGA(2)收到延迟后,在下一个PRF同步信号到来时,计数DSP接收时间,计数结束,从输出FIFO读取运算完毕的数据,同时启动D/A转换器进行数据转换。

3.3性能改进

虽然系统性能能够满足实际应用需求,但对某些环节稍作改进,会使整个系统功能进一步增强。对于DSP而言,同步FIFO为异步存储器,所以DSP在读写FIFO时设置为异步方式,读FIFO的频率仅能达到25 MHz,写FIFO的频率仅能达到33 MHz。如果将DSP读写SDRAM时序进行逻辑转换,可使读写FIFO的频率达到100 MHz,大大增强DSP的数据吞吐能力;另外单路视频信号的数据仅使用一片Flash存储器,虽然其峰值读数速度可达40 M字节,但由于每读2 K字节后,Flash需占一个缓存时间,这样其平均读数速度仅能达到约27 M字节。若将两片Flash并联,则达到其峰值速度,提高了系统性能;另外,目前在DSP内部仅在数据输入端开辟一个乒乓缓存,若在数据输出端也开辟一个乒乓缓存,则可将数据搬移和CPU运算进一步并行执行,缩短每个PRF周期的数据处理时间。

4结语

针对具体的雷达信号处理器,提出一种视频信号模拟器的硬件设计,模拟器采用PC机+DSP组合架构,整个系统采用插卡式结构,各路视频信号的生成使用相似的硬件电路,由PC机产生所需的杂波、噪声数据及目标参数,并事先将生成的各路视频信号所需的杂波、噪声及目标参数通过自行设计的自适应单环总线下载到对应的大容量Flash存储器中,数据下载完毕后,经由DSP组合实时运算,在每个PRF同步信号的触发下输出视频模拟信号。由于Flash存储器为非易失性存储器,具有掉电后数据不丢失的优点,所以如果杂波、噪声及目标参数不改变的情况下,数据只需下载一次。另外,使用文中提出的环网总线结构,可保证数据的快速下载。

电子发烧友App

电子发烧友App

评论