的GPIO/中断引脚。在每个读取周期中,控制器都可以监视ERR引脚的输出。当检测到ERR引脚上的高电平时,ASIC应启动软件子例程以重写从SRAM读取的正确数据。图6显示了此方案的体系结构。1.2宽度扩展

2020-10-23 11:32:38

基本正确。外部可变的数据输入fpga,通过spi也基本正确,外部输入变化,单片机接收的数据也会相应的变化。测试SRAM时,参考网上的DE2开发板的SRAM例子,往SRAM里写固定的递增数据,然后由输入

2013-07-24 22:41:55

的读和写端口,设计里在每个数据引脚上以双倍数据速率各自独立地工作,因此能在一个时钟周期中传输4个数据字,因此4倍数据速率而得名。设计上采用分离的读/写端口从根本尚消除了SRAM与存储控制器之间对总线争用

2017-06-02 10:45:40

介绍的是关于SRAM的基础模块存有三种情况:standby(空余),read(读)和write(写)。 第一种情况:standby假如WL沒有选为上拉电阻,那么M5和M62个做为操纵用的晶体三极管处在

2020-09-02 11:56:44

介绍的是关于SRAM的基础模块存有三种情况:standby(空余),read(读)和write(写)。

2020-12-28 06:17:10

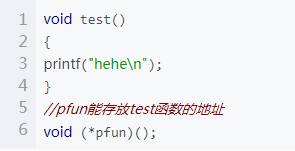

数据指针 在嵌入式系统的编程中,常常要求在特定的内存单元读写内容,汇编有对应的MOV指令,而除C/C++以外的其它编程语言基本没有直接访问绝对地址的能力。在嵌入式系统的实际调试中,多借助C语言指针

2021-12-15 08:56:20

TFT LCD液晶显示屏、LY68L6400SLI SRAM芯片,对应的引脚如下:软件设计QSPI SRAM测试初始化TFT LCD初始化QSPI SRAM写数据到QSPI SRAM从QSPI

2022-05-27 19:52:05

CLA_CPU_MSGRAM 时,还没有写完,此时CPU中断读这个值,会不会出问题?反之CPU写数据到 CPU_CLA_MSGRAM 时,还没有写完,此时CLA中断读这个值,会不会出问题?

2018-10-17 15:01:23

什么是指针?指针是变量。像其他变量一样,它具有数据类型和标识符。但是,使用指针的方式与使用“普通”变量的方式根本不同,并且必须使用星号告诉编译器应该将变量视为指针。这是指针声明的两个示例:char

2020-09-08 23:30:28

随机存取存储器(RAM)读、写随机寻址数据丢失只读存储器(ROM)读随机寻址数据不丢失工作前写入数据 闪存(Flash Memory)读、写随机寻址数据不丢失先进先出存储器(FIFO)读、写顺序寻址

2012-08-15 17:11:45

SRAM 在读写上有严格的时序要求,用 WEOECE 控制完成写数据,具体时序如图 7-17所示。图 7-17 SRAM 的写时序系统中两块 SRAM 分别由 DSP 和 FPGA 控制。当 DSP

2018-12-11 10:14:14

我现在需要统计sram的地址出现的频率,比如如果地址1出现一次,就在地址1里存1,地址10出现了5次,就在地址10里存5,其它地址也是进行类似操作。。。本来准备是根据地址直接对这个地址进行写1操作

2016-10-26 11:18:25

,这部分是写数据。就看写的数据和sram_data是不是一样的,发现是一样的。说明功能正确。然后观察黄线右边的部分,这部分是读数据。就看读的数据是不是和sram_data_reg一样的。发现

2015-03-19 20:17:25

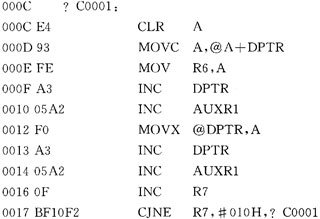

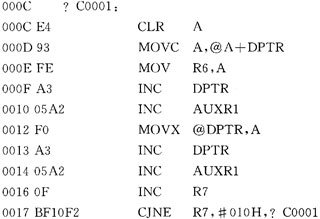

的性能。作为一种增强特性,有许多8051派生型器件支持双数据指针。以宏晶科技STC89系列的产品为例,DPTR被增强为DPTR0和DPTR1两个,仍然使用原来的地址,用另外一个SFR AUXR1的0位

2011-11-30 17:30:00

顺序写入数据,乱序写入数据,直接填充数据都是正常的。在程序中使用指针操作时,如果地址%64<32,改变这个地址的数据,也会改变这个地址+32的数据。如果地址%64>

2023-03-28 08:13:08

的标称性能。双模结构如图1所示。标准模式标准模式是标准接口的一个配置选项,在这种模式下,为了节省必须从内核发送的信号总数,I-SRAM和D-SRAM信号合并在一起。除了数据写总线外,D-SRAM接口

2019-05-28 05:00:02

应用:数据闪光模拟EEPROM和写/读EEPROM

BSP 版本:Mini51DE系列 BSP CMISIS V3.02.000

硬件: NuTiny-EVB-Mini51_V2.1

使用数据闪电

2023-08-30 07:54:52

嗨,我写了一个软件,将数据写入FPGA寄存器,并读取处理结果。我发现重复读/写,软件再也无法读取寄存器(DpcPutReg函数返回-1)我也尝试使用Adept软件,经过一些(10~30)读/写后,我

2019-07-22 08:14:21

。FIFO选用了IDT公司的IDT7202。它具有输入和输出两套数据线,独立的读/写地址指针在读/写脉冲的控制下顺序地从双口FIFO读/写数据,读/写地址指针均从第一个存储单元开始,直到最后一个存储单元

2019-04-26 07:00:06

的IDT7202。它具有输入和输出两套数据线,独立的读/写地址指针在读/写脉冲的控制下顺序地从双口FIFO读/写数据,读/写地址指针均从第一个存储单元开始,直到最后一个存储单元,然后又回到第一个存储单元

2018-12-05 10:13:09

0xC1FFFFFF遍历写入并读出,通过TIM2计时,以字节写入时,写时间0.16秒,读时间0.73秒,以半字节操作时,写时间0.09秒,读时间0.71秒。请问为什么读比写要慢得多?

下面是写入和读出代码,系统主频550M,逻辑操作耗时应该基本可以忽略

for(temp=0; temp

2024-03-11 06:40:14

与SRAM芯片连接。 SRAM型号IS62WV51216,管脚图如下: IS62WV51216的管脚总的来说大致分为:电源线、地线、地址线、数据线、片选线、写使能端、读使能端和数据掩码信号线

2020-05-07 15:58:41

1. 程序和数据在Flash和SRAM上的存储结构在讲解 STM32 启动过程之前,我们先来了解一下 STM32 的程序和数据在 Flash 和 SRAM 上到底是如何存储的,因为有了这方面的知识

2022-02-18 06:13:34

接口对于SRAM的读操作时序,其波形如图所示。对于SRAM的写操作时序,其波形如图所示。具体操作是这样的,要写数据时,(这里是相对于用FPGA操作SRAM而言的,软件读写可能有时间顺序的问题需要

2015-12-16 12:46:04

实例每秒钟定时进行一个SRAM地址的读和写操作。读写数据比对后,通过D2 LED状态进行指示。与此同时,也可以通过chipscope pro在ISE中查看当前操作的SRAM读写时序。 2 模块划分该

2015-12-18 12:57:01

在SRAM中存满数据,并通过以太网发送满盘数据。发送时也是像例程一样,定义数据数组,读一个SRAM地址指针更新一次数据数组?还是有其他方法?

2019-07-01 04:35:46

使用MCU的FMC外扩SRAM时,对外部SRAM进行读写操作时,写操作无异常,通过寄存器均可按照手册控制。在进行读操作时,开启EXTMOD功能,即使总线周转时间设置为0,两次连续的读操作时间还为

2018-08-23 08:51:05

都是低电平有效,后缀_n用于强调这一特性。功能表如表1所示:信号ce_n用于存储器扩展,信号we_n和oe_n用于写操作和读操作,lb_n和ub_n用于字节配置。 表1 SRAM控制信号的真值表接下来

2017-03-07 16:26:01

,比如读、写、调用函数等。 2、永远不要使用“野”指针 前面说了,指针的内容是 地址,是内存地址,一旦你拥有了一个指针,你也就有了权力去通过这个指针名字去访问指针指向的内容了,我们可以打个比方,内存

2019-08-20 08:30:00

写入相应的数据。2、(2级) sram的读写操作要求:1、每隔1s对sram读一次,每次读取一个数据,读地址每次增加1(0--1---、、、--15--0),2、写数据要求:在不影响sram读的情况下

2015-05-09 10:41:41

这里写自定义目录标题为什么要扩展外部SRAM(一)什么是SRAM简介存储器型号容量引脚配置通讯方式读写特性读取数据时序图读取数据的时序要求写入数据时序图写入数据的时序要求(二)什么是FSMC外设简介

2021-08-05 07:13:19

这里写自定义目录标题(一)为什么要扩展外部SRAM(二)什么是SRAM简介 存储器型号 容量 原理框图 引脚配置 通讯方式 读写特性 读取数据时序图 读取数据的时序要求 写入数据时序图 写入数据

2021-08-05 08:22:50

寻址的存储单元将它存储的数据送到相应位线上的操作。图3.5 表示的是进行读操作的一个SRAM单元,两条位线开始都是浮空为高电平。假设当前单元中存储的值为逻辑“1”,即节点A为高电平,节点B为低电平

2020-04-29 17:27:30

这是网上比较流行的一个异步fifo方案,但是fifo的空满判断不是应该是立即的吗,加上同步器之后变成写指针要延时两个读周期再去个读指针做空比较,而读指针要延时两个写周期再去和写指针做满比较,这样虽然可以避免亚稳态之类的问题,可是这个延时对总体的空满判断没有影响吗,如果没有影响是怎么做到的呢,求解

2016-07-24 16:25:33

已用这种模式成功驱动了一些psram,但是SRAM始终驱动不了。

SRAM驱动架构

XMC复用模式读时序,其中一个HCLK=4.16ns(240Mhz)

SRAM读时序参数

SRAM读时序图

XMC

2024-01-04 10:46:19

SRAM接口对于SRAM的读操作时序,其波形如图8.36所示。图8.36 SRAM读时序对于SRAM的写操作时序,其波形如图8.37所示。图8.37 SRAM写时序具体操作是这样的,要写数据时,(这里是

2018-05-03 21:02:25

其应用范围,难坏了一大帮业余科学实验家。 今这小亮一“读SD卡图形直接写屏”的非常规招式,不占SRAM内存了、代码量减少了、速度加快了、低阶的单片机也能引用了,这可是“鼠辈得翼成仙”的节奏,非同小可

2017-07-31 12:52:13

的寄存器,例如:#define DDRB (*(volatile unsigned char *)0x25)分析如下:这样读/写以0x25为地址的SRAM单元,直接书写DDRB即可,即DDRB...

2021-11-30 08:07:19

SRAM 单元[17],如图 3 所示。这种结构具有独立的读写字线(RWL, WWL)和读写位线(RBL, WBL 和 WBLB),从而有分开的读端口和写端口;数据从读端口读出,从写端口写入。这样不仅

2020-07-09 14:38:57

你好,我有一个设计使用SRAM块,我想用一组输出寄存器配置它们。这通常会在读取操作中引入额外的延迟周期。但是,如果系统的其余部分以50MHz的频率运行,那么我可以将SRAMat设置为100MHz

2019-07-03 12:51:27

};pthread_mutex_lock(&mut);//考虑到485是半双工,读的时候不能写,写的时候不能读,故加锁控制sendCmdToSerial(sendData, sizeof(sendData

2016-10-14 14:22:24

在MCU(以常见的stm32为例)开发中使用多线程操作,我们经常遇到的问题是关于多线程访问数据的问题,多线程访问数据基本上可以分为几大类:多写一读多写多读一写多读一写一读多线程中如果出现多写,数据

2023-02-01 15:42:35

仅仅优化了单元读、写一方面的性能,另一方面保持不变或者有恶化的趋势;单端读写单元往往恶化了读写速度,并使灵敏放大器的设计面临挑战;辅助电路的设计,往往会使SRAM的设计复杂化。 为了使SRAM存储单元

2020-04-01 14:32:04

了,并继之以读使能校准。读使能逻辑对向存储器发送的读命令进行校准,为已采集到并写入读数据 FIFO 的数据生成写使能。校准逻辑使用 SRL16 构建而成,有助于确定读命令信号所需寄存器级数的数量,以

2019-04-22 07:00:07

我的目标是读/写8位数据到SRAM芯片AS6C4008。有点像尼古拉斯·维南2011A年5月在硅芯片上的SPORTSYNC项目,两周后仍然不能工作:1。我已经检查了所有的线路2。所有的MCU引脚都能

2019-10-11 07:31:13

(__IO uint16_t*)(0x60000000)将内部地址强制转换成了8位和16位的指针,这又是为什么?这个指针指向的不是内部SRAM的地址吗?如果是,这样子转换不会导致数据丢失吗,如果不是,这个指针又是指向哪里?难道是直接映射到外部SRAM里面了吗?恳请求教,十分感谢!

2022-08-19 01:08:14

Rev2S25FL256L:002-00124 版本 * H 我目前正在使用H723创建一个读写NORFLASH的项目。 但是,读/写不成功。 我想以H723为主,外接flash为从进行读写。 1、CubeMX设置不正确

2022-12-27 06:38:05

你好,我正在做一个使用GPIF II接口作为主机来从SRAM中写入和读取数据的项目。在我的固件项目中,DMA大小是512,计数是2。我已经成功地测试了写和读数据不到1024BIT。并且知道我想要像

2019-09-25 14:56:47

NUC472/NUC472/NUC442系列装有外部连接设备的外部公交界面(EBI)。 NUC472/NUC442 EBI便利连接控制界面由地址、数据、芯片选择和读/写斯特罗贝组成的设备,例如NOR闪光

2023-08-23 06:35:44

请问一下影响编程时间的因素是什么?如何减少写编程时间和读等待时间以提高读写性能呢?

2021-06-21 07:21:06

的值和*a的值都输出,这时候printf输出的a就是一串数,十进制的,而*a就是b的值,这时候我有个疑问,这个指针变量是以什么形式保存,或者说所有变量类型,我们可不可以以十进制直接保存,然后让他以指针

2019-11-05 03:40:28

如何对RAM进行读和写的操作?

2022-01-18 06:47:23

大家好,我正在尝试使用Nexys-3板设计PDP-8内存。但我正在努力弄清楚如何使用板上的CellularRAM来读/写。我在Google上找不到任何有用的信息。有人能给我一个关于如何用

2019-07-01 08:50:31

我正在使用SPC560D和SPC5Studio。我想在将设备置于待机模式之前保存设备配置/状态,并在设备退出待机模式时使用/检索此状态。这可以通过使用SRAM来实现吗?如何访问SRAM以进行可变存储

2019-06-21 08:53:02

如图所示的异步FIFO,个人觉得在读写时钟同步时会产生两个时钟周期的延时,如果读写时钟频率相差不大,某一时刻读写指针相等,当写指针同步到读模块时会产生延时,实际同步到读模块的写指针是两个时钟周期之前的,这样就不会产生空满信号,要两个周期之后才能产生空满信号,结果是写溢出或读空

2015-08-29 18:30:49

本帖最后由 一只耳朵怪 于 2018-6-14 10:51 编辑

我想往CPU1TOCPU2RAM写一组数据,CPU2来读,如何来判断这一组数据读时已写完?可不可以用这个呢?

2018-06-14 04:20:16

我正在使用 S32k358 uC,我想禁用内存区域的数据缓存。在框图中,我看到树形 SRAM 块 SRAM0、SRAM1、SRAM2。是否可以禁用 SRAM2 的数据缓存并保留 SRAM 0 和 SRAM1 的数据缓存?

2023-04-23 08:01:09

静态存储单元和其读写控制电路组成的记忆体电路,对此的详细内容在四个晶体管搭建静态存储单元,加两个晶体管搭建写控制电路一文中。LY62L5128是一个CMOS SRAM。容量512KB(512K X 8

2016-08-30 04:32:10

谷歌和这个论坛没有返回太多关于在 8 位模式下直接访问 GPIO 端口以进行读/写的信息......例如控制一个 8 位 TFT 模块......HAL 库也没有它的功能....我认为这是可能的..但只有在深入研究低级直接寄存器访问时才有可能?

2023-02-07 06:25:37

请教各位大神讲解下如何用ActiveX控件与Excel实现数据读、写?

2014-03-27 19:49:20

亲爱的,流水线SRAM的数据表(例如部分CY7C1382KV33)在第8页的“单读访问”段落中表示,支持连续的读周期。一个读周期有一个延迟2个时钟周期。这是否意味着你可以每2个CLK周期做一个读周期

2018-08-16 04:11:48

用FPGA往SRAM芯片中写数据重复写多次才能写是怎么回事呢?

2023-04-23 11:46:44

单片机和LCD1602的读状态,写状态,读数据,写数据各指的什么,不是太明白,请高手帮忙解答,谢谢

2019-04-12 06:35:22

STM8读同时写RWW

2020-11-10 07:20:30

F207VE-26ms/1Mbytes;实测写速度:F103VC-43.5ms/1Mbytes F207VE-27.3ms/1Mbytes(7)要使用SRAM,定义1个这样的指针:static U32 *aMemory = (U32 *)FSMC_BANK1_1_NE1;(8)有时间的话了解下我们的人机界面解决方案GLCD

2016-07-08 15:10:32

SRAM,SRAM原理是什么?

静态随机存取存储器SRAM。

SRAM主要用于二级高速缓存(Level2 C ache)。它利用晶体管来存储数据。与DRAM相比,SRAM的速度快

2010-03-24 16:11:32 8479

8479 在8051体系中,数据指针DPTR作为一个特殊的16位寄存器,用于寻址64 KB的XDATA或CODE空间,通常它被当作一个16位指针,指向一个常数表。双数据指针可以改善同时有两个16位指针使用时

2010-07-20 17:36:46 1276

1276

STM32单片机上的SRAM 中的数据丢失

2015-11-25 14:49:27 0

0 C和指针习题答案配C和指针

2017-09-07 14:29:48 6

6 SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,功耗较小。

2017-11-03 16:11:12 11253

11253 首先,你要明白一个概念,指针,是做什么的?答案是,指针,是指向地址的。程序指针,指向的空间,在物理上是Flash,在逻辑上,就是代码空间。比如说51单片机的PC指针,指向的就是Flash,即程序下一步要执行的指令的地址。

2017-11-10 11:21:57 7418

7418

堆栈指针总是指向栈顶位置。一般堆栈的栈底不能动,所以数据入栈前要先修改堆栈指针,使它指向新的空余空间然后再把数据存进去,出栈的时候相反。堆栈指针,随时跟踪栈顶地址,按“先进后出”的原则存取数据。

2017-11-13 09:40:17 12736

12736

为什么使用指针?因为在操作大型数据和类时,指针可以通过内存地址直接访问数据,可避免在程序中复制大量的代码,因此指针的效率最高。一般来说,指针会有3大用途

2018-10-04 10:33:00 4720

4720 SRAM主要用于二级高速缓存。它利用晶体管来存储数据。与DRAM相比,SRAM的速度快,但在相同面积中SRAM的容量要比其他类型的内存小。

2019-04-01 16:28:47 9613

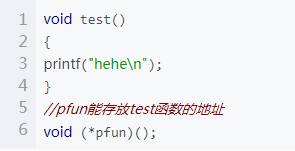

9613 理解函数指针、函数指针数组、函数指针数组的指针

2020-06-29 15:38:34 14291

14291

一种由普通SRAM、后备电池以及相应控制电路集成的新型存储器:非易失性SRAM(NVSRAM)。 为解决SRAM的数据保存问题,国外著名半导体公司率先推出了可以完全替代SRAM的NV-SRAM系列产品,国内也有同类产品相继问世。面对众多的NVSRAM产品,广大用户如何选择质优价廉的产品呢?建议用户根据以

2021-01-11 16:44:20 1714

1714 C语言指针的理解使用指针变量的声明给普通变量的赋值对比给指针变量的赋值代*的指针的使用说明指针变量的声明一个指针声明后没有赋值,它的数据位是随机的:unsigned char *p;给一个指针变量

2022-01-13 13:42:25 3

3 在C语言中一个数组,若其元素均为指针类型数据,称为指针数组,也就是说,指针数组中的每一个元素都存放一个地址,相当于一个指针变量。

2023-03-10 15:26:24 1140

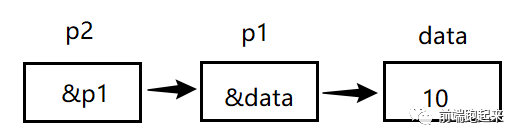

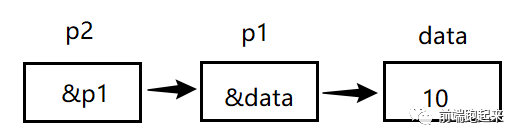

1140 一级指针的用法其实是取数据的地址,以此类推,二级指针就是取一级指针的地址,也可以表示一级指针的指向的内容。

2023-05-19 17:30:29 863

863

SRAM可以分为低速、中速、高速。===========================================================16位宽的SRAM//16BITSRAM指针

2023-04-06 15:13:03 554

554

电子发烧友App

电子发烧友App

评论