传统的D/A转换方法有加权电阻器、R-2R梯形网络和零点交叉失真等。正如A/D中的情况那样,Σ-Δ设计统治了D/A转换的领域。这些转换器可以接受16位44.1kHz的信号,然后使用插值滤波器把它转换为2.8224MHz的1位样点流。然后用1位的DAC把这些超级采样的样点流转换成模拟信号。

一个典型的嵌入式数字音频系统可以使用一个Σ-Δ音频ADC和一个Σ-Δ DAC,因此,在PCM信号和过采样流之间的转换要进行两次。由于这个原因,Sony与Philips (NXP半导体)已经在它们的Super Audio CD(SACD)格式中引入了一种与PCM不同的格式,被称为直接流数字(DSD)。这种格式用1位的高频(2.8224MHz) Σ-Δ流来存储数据,因而绕过了PCM转换。它的缺点是,DSD流不像PCM那样直观,而且需要一套独立的数字音频算法。

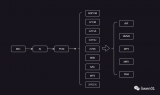

好了,我们有了足够的背景知识。现在让我们看一下实际的转换器连接的例子。对于低成本音频ADC的很好的选择是ADI公司的AD1871,它使用Σ-Δ技术以96kHz的速率进行24位的转换。图3a示出了AD1871的功能框图。这个转换器有左(VINLx)和右(VINRx)两个输入声道,这其实就是能够处理立体声数据的另外一种说法。数字化的音频数据是通过数据端口串行流出的,通常流到信号处理器的一个相应的串行端口(如Blackfin处理器上的SPORT接口)。另外还有一个SPI(串行外围接口)端口,利用该端口,主处理器可对AD1871通过软件命令进行配置。这些命令包括设置采样率、字长、声道增益和静音等的方法,还有其他一些参数的设定。

图3 (a)AD1871音频ADC的功能框图

(b) 一个ADSP-BF533媒体处理器与AD1871的无缝连接

正如图3b中的框图所指出的,AD1871 ADC与 Blackfin处理器可无缝连接。电路的模拟部分被简化了,因为在这个讨论中只有数字信号才是重要的。AD1871的过采样率由外部晶振提供。图中的处理器有2个串行端口(SPORT)和一个SPI端口,用于连接AD1871。被配置成I2S模式的SPORT是与AD1871进行数据连接的端口,而 SPI端口用作控制连接。

I2S协议是由Philips(NXP半导体)为音频信号的数字传输而开发的一个标准。该标准使音频设备制造商所生产的器件可以相互兼容。

确切地说,I2S是一种用于传输立体声数据的3线串行接口。正如图4a中所示,它规定了位时钟(中)、数据线(下)和左右同步线(上),而左右同步线用来选择当前正在传送的数据帧是左声道的还是右声道的。

从本质上讲,I2S是一个带有两个活动声道的时分复用(TDM)串行流。TDM是一种通过一条物理链路传输超过一个声道(比如左声道与右声道)的方法。

在AD1871电路结构中,当对SPORT时钟(RSCLK)和帧同步(RFS)线进行驱动时,ADC可以降低它从外部晶振接收到的12.288 MHz采样率。该配置保证了采样和数据传输是同步的。

SPI接口,如图4b所示,是Motorola为了使主处理器可以与各种数字器件相连而设计的。这个在SPI主设备与SPI从设备之间的接口由一条时钟线(SCK)、两条数据线(MOSI和MISO)和一条从设备选择(SPISEL)线组成。其中一条数据线由主设备(MOSI)驱动,而另一条由从设备(MISO)驱动。在图3b的例子中,处理器的SPI端口是无缝地与AD1871的SPI模块相连接的。

图4 (a)数据信号由AD1871使用I2S协议进行传送

(b) SPI 3线接口用于控制AD1871

带有独立SPI控制端口的音频编解码器允许主处理器在运行中修改ADC的设置。除了静音和增益控制外,其中一个确实很有用的ADC(如AD1871)设置是对节电模式的设置能力。对于电池供电的应用来说,这通常是一个本质功能。

DAC与编解码器

将音频DAC与主处理器相连接与我们才讨论过的与ADC连接的过程完全一样。在一个同时使用ADC和DAC的系统中,同一个支持双向传输的串行端口可以同时连接这两者。

但是,如果您正在考虑全双工音频,那么您最好采用一个可以同时完成模拟数字转换和数字模拟转换的单芯片音频编解码器。这样的编解码器的一个很好的选择是ADI公司的AD1836,它有三个立体声DAC和两个立体声ADC,而且可以通过多种串行协议进行通讯,包括I2S。

在本文中,我们讲到了将音频转换器与嵌入式处理器进行连接的一些基本内容。在本文的第二部分,我们将叙述音频数据在存储和处理时的格式。我们将特别回顾在选择数据字长时的折衷方法。这是很重要的,因为这决定了所用的数据类型,而且,如果希望获得的质量等级太高而某个特定器件达不到的时候,也可以避免选择某些处理器。此外,数据字长的选择有助于在增加动态范围和增加处理能力之间的折衷选择。

音频功能在嵌入式媒体处理中起到关键性的作用。虽然一般来说,音频处理比视频处理占用较少的处理能力,但它们具有相同的重要性。

本文共包括三个部分,在第一部分中,我们将探讨数据是如何从各种音频转换器(DAC和ADC)传送给嵌入式处理器的。在这之后,我们将探讨一些经常用于连接音频转换器的外围接口标准。

模拟与数字音频信号之间的转换

采样

所有的A/D与D/A转换都应该遵循Shannon-Nyquist采样定理。简言之,该定理规定了模拟信号在被采样时的速率 (Nyquist采样率)必需等于或超过它的带宽(Nyquist频率)的两倍,以便可以在最后的D/A转换中进行信号重构。低于Nyquist采样率的采样将产生混叠,而这种混叠是那些超过Nyquist频率的频率分量在低频区的镜像叠影。如果我们取一个带宽限制在0-20kHz范围内的音频信号,并在2×20kHz=40kHz频率下进行采样,那么Nyquist定理就能确保我们可以对原来的信号进行完美重构而不会有任何信号损失。但是,对这个0-20kHz带限信号用任何低于40kHz的采样率进行采样时,将会由于混叠而产生失真。图1示出低于Nyquist采样率的采样如何使信号表示得不正确。在40kHz频率下采样时,20kHz的信号被正确地表示(图1a)。但是,同样的20kHz正弦波,当在30kHz频率下采样时,实际上看起来像是原始正弦波在一个较低频率上的混叠(图1b)。

图1 (a)用40kHz对20kHz信号进行采样可以正确地捕捉到原始信号。

(b)用30kHz对同一个20kHz信号进行采样所捕捉到的是一个被混叠了的信号(低频重影)

然而,没有一个实际系统是正好用两倍的Nyquist频率进行采样的。例如,把一个信号限制于一个指定的频带内要使用模拟低通滤波器,但这些滤波器从来就不是理想滤波器。因此,通常用来还原音乐的最低采样率是44.1kHz而不是40kHz,而且许多高质量系统是用48kHz进行采样的,以捕捉到0-20kHz范围内更加逼真的听觉感受。

由于语音信号只是我们可以听到的频率范围的一小部分,所以4kHz以下的能量就足以使还原的语音信号能够听得懂。基于这个原因,电话应用中通常只使用8kHz的采样率(=2×4kHz)。表1归纳了我们所熟悉的一些系统的采样率。

表1 常用的采样率

PCM输出

音频信号最常用的数字表示是PCM(脉冲编码调制)信号。在这种表示中,对每个采样周期内的一个模拟幅度用一个数字量进行编码。这样得到的数字波形是一个用来近似地表示输入模拟波形的由抽取点组成的矢量。所有A/D转换器的分辨率都是有限的,所以转换器引入了数字音频系统所固有的量化噪声。图2示出模拟正弦波的PCM表示(图2a),它是用一个理想的A/D转换器进行转换的,图中的量化操作显现为一种“阶梯效应”(图2b)。您可以看到,较低的分辨率导致了对原始波形的较差的表示(图3c)。

图2 (a)一个模拟信号 (b) 数字化之后的PCM信号

(c) 使用较少位数精度进行数字化之后的PCM信号

作为一个数值例子,让我们假设用一个24位A/D转换器对一个模拟信号进行采样,而这个模拟信号的范围从-2.828V到 2.828V(5.656的峰峰值)。24位有224(16777216)个量化等级。因此,有效的电压分辨率为 5.656V/16777216=337.1nV。在本文的第二部分,我们将看到编解码器的分辨率如何影响音频系统的动态范围。

PWM输出

脉宽调制(PWM)是不同于PCM的另一种调制方法,它可以直接驱动输出电路而无需任何DAC的帮助。这在需要低成本的解决方案时特别有用。

在PCM中,对每个采样周期内的幅度进行一次编码,而在PWM信号中描述幅度的是占空比。PWM信号可以通过通用I/O引脚产生,或者可以用许多处理器中都有的专用PWM定时器来直接驱动。

为了使PWM音频达到相当好的质量,PWM的载波频率应该至少12倍于信号的带宽,而且定时器的分辨率(即占空比的间隔时间)应该有16位。由于载波频率的需求,传统PWM音频电路曾经被用于窄带音频,比如超重低音。但是,利用目前的高速处理器,就可以扩展到更宽的音频谱。

PWM流必须经过低通滤波,以去除高频载波。这通常是用驱动扬声器的放大器电路来完成。D类放大器已经被成功地用于这种结构。当不需要放大时,一个低通滤波器就足以用作输出级。在一些低成本应用中,声音的品质不是那么重要,就可以把PWM流与扬声器直接相连。在这样的系统中,扬声器纸盆的机械惯性充当了滤除载波频率的低通滤波器。

音频转换器的简要背景

音频ADC

完成A/D转换可以有许多种方法。一个传统的方法是逐次逼近的方案,该方案使用一个比较器对模拟输入信号与一连串中间D/A转换输出之间的比较结果进行检测,然后得到最后的结果。

但目前的大多数ADC都是Σ-Δ转换器。这种转换器不是使用逐次逼近的方法来产生很高的分辨率,而是使用了1位的ADC。为了对这个减少了的量化等级数进行补偿,这些转换器在比Nyquist频率高得多的频率下进行过采样操作。把这些过采样的1位样点流转换成一个较低速率、较高分辨率的样点流是使用这些转换器内部的数字滤波模块完成的,目的是为了适应传统PCM流的处理。例如,一个16位44.1kHz的Σ-Δ ADC可以用64倍的过采样率,产生一个速率为2.8224MHz的1位样点流。然后用一个数字抽取滤波器把这个超级采样的样点流转换成一个速率等于44.1kHz的16位样点流。

由于对模拟信号的过采样操作,Σ-Δ ADC放宽了对用来限制输入信号带宽的模拟低通滤波器的性能要求。这些转换器还具有将输出噪声分布在比传统转换器更宽的频谱内的优点。

电子发烧友App

电子发烧友App

评论