1 引言

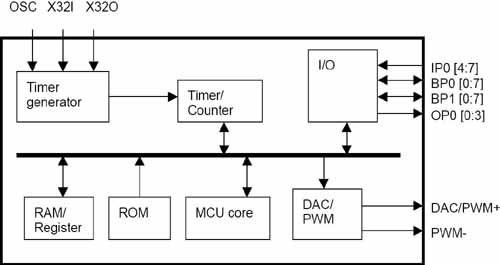

G.723.1是删组织于1996年推出的一种低码率的语音编码算法标准,也是目前该组织颁布的语音压缩标准中码率最低的一种标准。G.723.1主要用于对语音及其它多媒体声音信号的压缩,目前在一些数字音视频传输、高质量语音压缩等系统中都得到广泛应用。

2 G.723.1算法的复杂度分析

将G.723.1移植到TMS320C64xx后,就可借助TI集成开发工具CCS(Code Composer Studio)的Profile功能来评估其各个子程序或函数的执行运算量,从而把程序的优化集中在对程序性能影响最大的代码上去。

通过分析可以看出,在G.723.1的编解码算法中,码本搜索所花费的运算量是比较大的,如Find_Best(),Find_Fcbk(),Find_Acbk():另外,在LPC分析和LSP参数的计算上也有运算量比较大的,如Comp_Lpc(),Lsp_Qnt(),Lsp_Svq()。

3 代码的优化

代码优化的工作有两大目的:一是执行速度提高,实现实时;二是尽量不扩大程序体积(Code Size),使之在内存允许的范围内。显然,两者存在一定的矛盾,当今超大规模集成电路的发展使RAM资源不再是系统的瓶颈,因此该部分工作的主要任务是怎样提高执行速度。代码的优化工作主要在CCS环境中进行。优化的原则是要充分考虑C64xx处理器超长指令字、多个运算单元和深度流水线的结构特点,以及避免过多的读写内存指令和程序转移指令,充分发挥其强大的运算能力。具体方法包括(次序有先后):

3.1基本运算集的优化

G.723.1算法程序是用定点运算完成浮点运算,为了防止定点运算时可能溢出,许多运算需要进行饱和判断,为此程序专门定义了基本运算集,实现诸如饱和加法、饱和乘法、除法和移位等操作。在程序中这些操作调用相当频繁,经CCS的profile工具测试,基本运算函数集的调用占用了95%以上的CPU时间。因此,我们要从基本运算集的优化开始。在熟悉掌握C64xx指令集的前提下,分析基本运算集中各个函数完成的悉掌握C64xx指令集的前提下,分析基本运算集中各个函数完成的功能和对全局变量产生的影响,用C64xx指令取而代之或加以改编。其中包括对跳转和流水线的优化讨论、对乘积的饱和调整和全局变量OveRFlow的相关操作。

由于基本运算集以函数形式存在,两次跳转f函数的调用与返回1必不可少,将引起流水线的两次打断,表现为12个指令周期的占用。将这嵝基本运算函数集改成宏的形式,即将基本运算内嵌(inline)至lJ调用程序中,由此町以消除跳转和流水线打断带来的指令周期占用,提高执行速度。虽然这样做增加了代码长度,多占用了一些内存,但由于基本运算函数体积均较小,再经过一定的代码优化,在程序体积上的牺牲几乎町以忽略。

基本运算的函数定义在BASIC.C文件里面,如果能够对这些简单甬数进行内联指令(intrinsic)的优化,就能达到事半功倍的效果。内联指令是汇编指令的直接映射,具有很高的效率。与此同时带来的一个问题是溢出保护位Overflow的判断,这是基本函数里用来标识溢出的全局变量,它的作用等同于CSR(Control Status Register)寄存器的SAT(Saturation)位,当数据溢出时,SAT位被系统自动设置为1,所以编解码函数里对Overflow的判断可以转化成对SAT位的判断。引用CSR寄存器时需要在最开始的时候声明extem cregister volatile ansigned int CSR。

C64xx指令提供了饱和乘法指令SMPY,实现16"16位的乘法与饱和结果调整,其执行操作如下:

if(cond){

if((src 1*src2<<1)!=0x80000000)

dst=((src 1*src2)<<1);

else

dst=0x7ffffff;

}

else

nop;

将原指令中的乘法指令改为SMPY.就可以完成乘法和饱和调整两种计算,这样可以省去饱和调整3条指令。与此类似,其它的饱和运算,C64xx都提供了相应的指令实现,将普通运算指令替换为饱和运算指令,饱和结果调整部分的运算均可以省去。

3.2主程序的优化

主程序的优化手段主要采用了以下几种方法:

(1)使用内联函数(intrinsics)

内联函数是可直接映射为C64xx指令的特殊函数,它在指令前加上"_”表示。例如:

#define L_add(L_var1,L_var2) _sadd(L_var1,L_var2)

#define L_mult(var1,vat2) _smpy(var1,var2)

等,基本函数的内联优化需要对原函数的定义和内联指令都比较熟悉。

使用内联函数代替相应的C语句是一种非常简便高效的优化方法。如上面提到的饱和乘法,在C语句中。我们通常要使用两个嵌套的条件判断语句来检查结果是否溢出,而指令int_smpy(int a.int b) 则在完成乘b的运算后,再做一次饱和处理,这样一条DSP指令就可完成C语言中多条语句才能完成的计算,可以节省很多时钟周期。

(2)循环展开(loop—unrolling)

程序中的有很多的双重循环和多晕循环(比如代数码本搜索计算),由于C64xx优化器在优化时只在最内层循环中形成一个指令流水(最多可以达到8级流水),这样循环语句就不能充分利用软件流水线,而且对于内部循环次数较少的情况,消耗在prolog和eplog上的时钟周期也不可忽视。针对这种情况,一个有效的办法就是将双重或多重循环展开,降低循环次数。这样虽然代码长度增加了,但有更多的运算能够参加到pipeline中。由于减少了流水线排空和提高了功能单元的利用率,程序执行速度会大大提高。

(3)减少分支和调用指令,减少判断指令

程序中的分支、调用以及判断指令会引起程序的跳转,而每个跳转指令都有5个延迟间隙。因此延长了程序执行时间;另外,循环内跳转也会使软件流水受到阻塞,降低了代码执行效率。优化中,可以使用内嵌、合并判断语句来减少判断次数或用逻辑指令替代判断的方法尽可能的消除中断流水线指令带来的影响。

(4)使用字或双字存取和计算

C64xx系列DSP是32位CPU,当16位数据在内存中连续存放时,可利用uint_amem4(void*ptr)或double & _amemd8 (void*ptr)指令进行字或双字数据的读取或存贮。这样每次可同时存取2个或4个16位数据,由于从内存执行取数操作需要4个delay,所以减少存取次数可以节省大量的时钟同期;同时,可利用C64xx指令集中特有的打包指令_pack2(unsigned a,unsigned b),_packh2(unsigned a,unsigned b)等将两个16位数打包成一个32位数,在进行乘、加计算时则利用_add 2(int a,int b)、_mpy2(int a,int b)同时完成两组16位数的加法和乘法,效率比单纯16位数的加法和乘法提高一倍。

3.3汇编编程的优化

线性汇编是TI提供的一种汇编语言,其指令系统和汇编语言的指令系统完全相同,但在编写时不需要指定寄存器和操作单元,也不需要考虑延时的问题,因此编写线性汇编相对要容易一些。

经过以上的优化后,音频编码程序在DM642上的运行状况有了很大改善,但是经测试仍然没有到达可以接收的程度,而高级语言的效率几乎发挥到了极致,所以在具体分析耗时大的模块特点后,采用线性汇编语言重新编写C代码的低效率段程序,迸一步提高程序的执行效率。

在编写线性汇编优化代码的过程中,为了提高代码执行效率,我们需要遵循以下原则:

(1)写并行代码:通过使用汇编指令并行执行的方法减少循环内的执行周期数,优化线性汇编代码。这里的关键问题是弄清指令相关性,只有不相关的指令才能并行执行。辨别指令是否相关.可以使用相关图。

(2)处理跳转指令和转移指令:汇编程序的一大特点就是频繁地跳转,当满足不同的条件时,要求程序进行不同的操作,或跳到相应的位置。对于“大于”、“大于等于”、“小于”、“小于等于”等较为接近的逻辑判断和处理,应慎重对待,否则将产生逻辑性错误,并且很难调试。当发生溢出需进行相应处理时,这种现象尤为突出。

(3)尽量减少循环体内的指令数[7]:G.72.1的算法实现,有许多是在循环内部完成的,有些地方如同定码本搜索过程中,为了确定四个非0脉冲的位置和幅度,还用到了多重循环。在循环内部,特别是在嵌套较深的循环内部,减少一条指令可以大大降低程序的操作次数。例如。对于一个每重循环8次的四重嵌套循环,在最内层循环每减少一条指令,整个程序可以少执行84=4096语句。因此在设计程序时,能够放在循环体外执行的语句.尽量放在循环体外执行。

(4)展开程序体:尽在一定条件下,尽量展开程序,以减少子程序的调用和返回次数,牺牲空问换取时间。

经汇编优化器优化后,代码效率比C语言直接编译有明显提高。

4 优化工作的创新点

在对G.723.1的优化中.本文在前人研究成果的基础上,针对DSP C64xx系列芯片提}n了一些有价值的新方法。这些创新点在不同程度上提高了代码的优化速度和执行效率,在语音编解码的DSP实时实现中起到了关键性作用。下面,本文将以举例的方式阐明一些经典的方法。

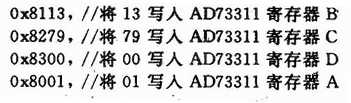

(1)编写连接命令文件.cmd

明确了系统的程序和数据映射地址后,编写连接器命令文件将部分调用次数较多的函数、堆栈段、数据段放入内存:cmd文件内容如下:

一L\evmdm642_echocfg.cmd //连接CCS提供的连接命令文件

SECTIONS

{

.tahles>SDRAM

.cinit>ISRAM //将变量初值表放入内存

. far >SDRAM

.const>ISRAM //将常数段放入内存

.pinit>SDRAM

. tin >SDRAM

.text>SDRAM

.test >ISRAM

}

一levmdm642bsl.lib //连接库文件

一levmdm642_edma_aic23.164 //连接驱动程序的库文件

一lc6xlx_edma_mcasp.J64 //连接串口McASP的库文件

其中.test是笔者在C程序内用#pragma CODE_SECTION或DATA_SECTION自定义的段。

(2)高速缓冲寄存器Cache的使用

Cache即高速缓存,是位于CPU和片内存储器之间的规模小速度快的存储器。Cache的工作原理是保存CPU中最常用的数据。当Cache中保存着CPU要读写的数据时,CPU直接访问Cache。由于Cache的速度与CPU相当,CPU能在零等待状态下迅速地实现数据存取。只有在Cache中不舍有CPU所需的数据时CPU才去访问片内存储器。因此Cache的有效利用对整个程序速度的提高有着举足轻重的作用。在主函数中加入以下代码,使Cache使能:

CACHE_clean (CACHE_L2ALL,0,0}; //清除Cache内原有内容

CACHE_setL2Mode (CACHE_64KCACHE); //设置Cache的大小为64K

CACHE_enableCaching (CACHE_EMIFA_CE00); //Cache使能

添加以上代玛后,测试速度由原来的20帧/s提高到了400帧/s。提高了将近20倍。

5 结束语

本文详缁分绍了G.723.1标准的DSP代码优化工作,重点描述了代码优化的方法和本课题的创新点.对于算法中的一些函数提出了独创性改写方法。基于线性汇编的优化以及Cache的有效利用使本课题的工作取得了显著成果,在没有降低音质的情况下,实现了DSP的语音实时编解码。

本文作者创新点:在对G.723.1的优化中,针对TMS320DM 642 DSP系列芯片提出了一些有价值的新方法。例如:编写连接命令文件.cmd和高速缓冲寄存器Cache的使用。这些创新点在不同程度上提高了代码的优化速度和执行效率,在语音编解码的DSP实时实现中起到了关键性作用。

语音编解码算法G.723.1在DSP上的优化

- 语音(37617)

- 编解码(19292)

相关推荐

语音信号的A律编解码的DSP实现

本文介绍了G.711标准的A律压缩算法的基本原理,设计出了A律编解码的软件流程框图,在以TMS320VC5416为处理器的硬件开发平台上实现了语音信号的A律压缩解压算法,并给出了C54x的汇编语

2011-10-13 14:45:04 3420

3420

3420

3420

在FPGA上h.264视频编解码的实现

想在DE2-115的开发板上完成h.264视频编解码,自己的想法是在已有的tpad_camer代码上加一软核,但一直失败,希望有相关经验的高手指点下?

2014-03-05 16:24:19

在TMS320C6657器件上轻松运行经TI 优化的Opus编码器/解码器

适用于语音通信、联网音频甚至高性能音频处理应用。较之 ARM 等通用处理器,此设计还通过在 DSP 上实现 Opus 编解码器来提升性能。根据通用处理器上所运行代码的优化级别,通过在 C66x TI

2022-09-22 06:32:42

语音压缩算法研究

希望广大DSP大侠们帮我出出主意,怎么才能写一个好的音频压缩算法,最好是在时域的压缩。频域的压缩发现都相对比较复杂。大家好,我是做语音芯片的。最近想研究一种压缩率高,音质好,并且解码简单。最好能用8

2013-09-18 17:38:38

语音和音频统一编解码算法研究

最近在研究MPEG-D标准的语音和音频统一编解码算法(USAC),USAC是2011年才开始提出来的,感觉挺有研究意义的,大家有兴趣可以互相交流下

2014-07-20 15:38:57

FPGA进行视频编解码

求助用FPGA进行视频编解码,可行吗?尤其在高清领域,FPGA强大的计算能力似乎很有优势,但算法极其复杂,各位高手指点指点。

2009-02-06 09:40:04

I91260语音芯片在SDS不同的编解码格式有什么区别?

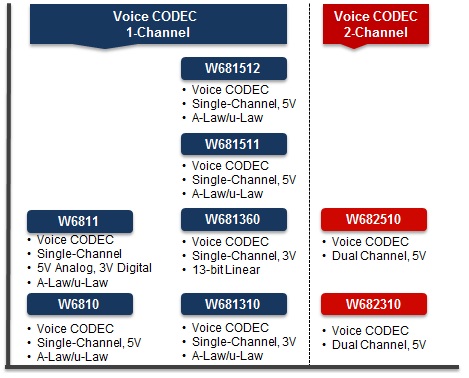

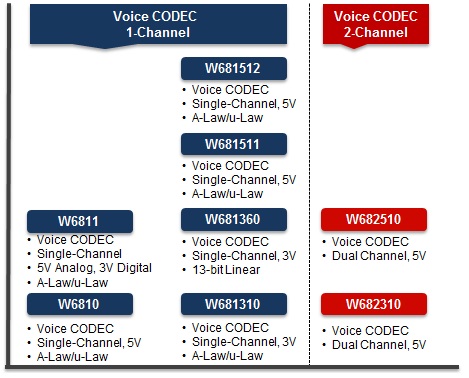

我正在使用 I91260 语音芯片,我在SDS 看到有不同的编解码格式(AudioPlayback MD4 NuOneEx ...) 我想知道这些格式有什么区别,我如何更好的选择使用那个格式?

我的另一个问题是,在那个文档 展示了关于 音频编解码的 介绍,比如 采样率,通道选择 等描述

2023-08-21 07:39:16

ISD91260编解码格式如何选择?

我正在使用 I91260 语音芯片,我在SDS 看到有不同的编解码格式(AudioPlayback MD4 NuOneEx ...) 我想知道这些格式有什么区别,我如何更好的选择使用那个格式?

我的另一个问题是,在那个文档 展示了关于 音频编解码的 介绍,比如 采样率,通道选择 等描述

2023-06-13 06:16:22

ITU Speech Codec音频协议的相关资料分享

一、G.711音频协议二、G.722.1音频协议三、G.722.2音频协议四、G.723.1音频协议五、G.726音频协议六、G.729音频协议

2021-12-24 06:31:19

MP3解码算法的软件优化有什么方法?

,嵌入式MP3软解码器的应用将越来越广泛。这里在分析MPEG I Audio Layer3解码算法的基础上,提出基于ARM946E处理器实现解码算法的软件优化方法。

2019-09-03 06:26:26

电子发烧友App

电子发烧友App

评论